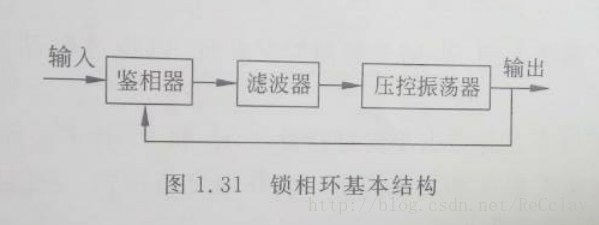

一、锁相环组成

锁相环一般由三部分组成压控振荡器、滤波器和鉴相器。最终使得输入和输出两个频率同步,且具有稳定的相位差。

二、锁相环作用

用来把输入的时钟频率进行倍频。

三、锁相环各个部分介绍

压控振荡器:电压变化控制输出的振荡器,输入电压越高,输出频率越大!

鉴相器:鉴定两个输入波形的相位,输出占空比稳定的波形。

滤波器:把鉴相器输出的或高或低的方波电压,经过滤波器变成平稳的直流电压。

四、如何具体实现输出信号的分频和倍频

如果想要倍频,只需要将压控振荡器的输出进行分频,比如二分频,其中一部分分频和输入频率得一样,那么对应输出的频率就是输入频率的二倍了。

想要实现分频,只需要吧输入的时钟频率分频即可!

2285

2285

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?