提示:文章写完后,目录可以自动生成,如何生成可参考右边的帮助文档

文章目录

xilinx 7系列FPGA配置、速率比较、专用管脚说明及启动顺序等介绍,参考xilinx文档ds1807series_overview

一、名词缩写介绍

HR: High range I/O (I/O voltage from 1.2V to 3.3V).

HP: High performance I/O (I/O voltage from 1.2V to 1.8V).

CMT: Clock management tiles.

MMCM: Mixed mode clock manager.

FIFO: First in first out.

SLRs: Super logic regions.

LUTs: Look up tables.

EOS: End of startup.

DCI: Digitally controlled impedance.

SPI: Serial peripheral interface.

BPI: Byte peripheral interface.

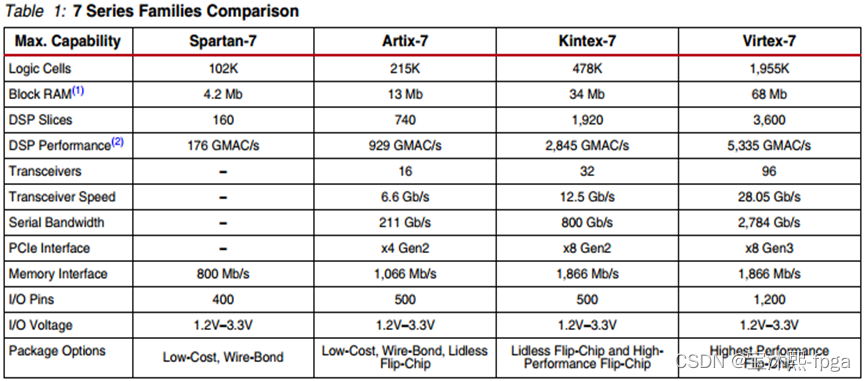

二、7系列FPGA比较

三、FPGA的配置模式说明

| Configuration mode | M[2:0] |

|---|---|

| Master serial | 000 |

| Master SPI | 001 |

| Master BPI | 010 |

| Master selectMAP | 100 |

| JTAG | 101 |

| Slave selectMAP | 110 |

| Slave serial | 111 |

| 注1:M2,M1,M0 pins can through pull-up or pull-down resistors(≤1kΩ),or tied directly to ground or Vcco. These pins should not be toggled. | |

| 注2:选择配置模式时要考虑:总体结构、处理速度、功耗、价格和其它复杂的东西。 | |

| 注3:3Master modes: self-loading FPGA configuration;Slave modes: externally controlled loading FPGA configuration; |

四、专用管脚说明

BANK 0:

1、CFGBVS(configuration banks voltage select_输入):给专门管配置的bank 0和拥有多功能复用引脚的bank 14、bank 15选择操作电压。CFGBVS连到高电平(Vcco_0),bank 0的操作电压为2.5V或3.3V;如果bank 0的Vcco_0电压≤1.8V,CFGBVS连到低电平(GND)。在配置期间,bank 14和bank 15也满足以上规则。

2、M[2:0](configuration mode_输入):模式配置管脚,配置方式见上表。这些引脚可以直接接到VCC或GND,也可以通过一个≤1KΩ的电阻连接到VCC或GND。

3、TMS、TCK、TDI、TDO: JTAG下载管脚。如果这些信号都经过buffer传输,其中TMS、TCK需要在buffer输入处连接一个弱上拉电阻(10KΩ)。

4、PROGRAM_B(program bar_输入): 低电平有效,复位配置逻辑。在下降沿时配置复位初始化,上升沿时配置时序开始启动。平时连接一个外部≤4.7KΩ的电阻到VCC_0确保稳定的高电平输入。

5、INIT_B(initialization bar_双向):低电平有效,表示FPGA初始化或是配置有错误的信号。当FPGA的配置处于复位状态或是FPGA初始化配置存储器或是FPGA检测到配置错误时,该引脚会被置低;如果该引脚被外部上拉电阻拉高,在FPGA初始化整个进程期间,这个引脚都会是高阻状态。通过一个≤4.7KΩ的电阻连接到VCCO_0上…。

6、DONE(双向):引脚电平为高时表示配置时序完成。该引脚内部有个10KΩ的上拉电阻。

7、CCLK(configuration clock_输入/输出):在主模式下,configuration clock由FPGA提供,CCLK是输出时钟;在从模式下,CCLK是输入需要连接到外部时钟源;在JTAG模式下,CCLK是高阻状态可以悬空不连接。

BANK 14:

1、PUDC_B(pull-up during configuration bar_输入):当该引脚为高时,内部上拉电阻作用于每一个SelectIO引脚;当该引脚为低时,内部上拉电阻不作用于每一个SelectIO引脚;该引脚必须直接或者通过≤1KΩ的电阻接在VCCO_14或GND(不能悬空,不允许电平浮动)。

2、EMCCLK(external master configuration clock_输入):在主模式下,FPGA可以随意转换EMCCLK作为时钟源从而代替内部振荡器,而且EMCCLK可以被随意分频输出作为master CCLK信号;在从模式和JTAG模式下,EMCCLK可以被忽略悬空不连接。

3、CSI_B(chip select input bar_输入):低电平输入时,FPGA的SelectMAP配置接口被使能。在主SelectMAP模式下,该引脚可以直接或者通过≤1KΩ电阻接到GND;在从SelectMAP模式下,该引脚被外部配置控制器控制在SelectMAP总线上选择FPGA或者在一个并联的配置菊花链中把CSO_B连到上一个FPGA;在其它模式下,该引脚可以被忽略悬空不连接。

4、CSO_B(chip select output bar_输出):在BPI(仅异步读模式)和SelectMAP模式下,如果设计是一个并联配置菊花链而且后面还有一个装置,那么连接外部电阻330Ω上拉到VCCO_14并且连接CSI_B到后一个装置,否者,该引脚输出高阻状态;在serial模式下,该引脚是一个多功能引脚作为DOUT使用;在其它模式下,该引脚输出高阻可以被悬空不连接。

5、DOUT(data output_输出):该引脚是串联配置菊花链的数据输出。在serial和SPI(仅×1)模式下,如果设计是一个串联配置菊花链,那么连接DIN到后一个从-串联的FPGA,否则,该引脚输出高阻;在BPI和SelectMAP模式下,该引脚是一个多功能引脚作为CSO_B使用;在其它模式下,该引脚输出高阻可以被悬空不连接。

6、RDWR_B(read/write bar_输入):该引脚可以控制SelectMAP数据总线的方向,如果引脚为高电平,FPGA的输出读数据到SelectMAP数据总线上,如果引脚为低电平,外部控制器通过SelectMAP数据总线把数据写到FPGA。在主SelectMAP模式下,该引脚可以直接或者通过≤1KΩ电阻接到GND;在从SelectMAP模式下,一个外部设备通过控制该引脚来控制SelectMAP数据总线的方向读或写到SelectMAP接口;在其它模式下,该引脚可以被忽略悬空不连接。

7、D00_MOSI(master output slave input_双向): FPGA主SPI模式发送命令到从SPI的flash设备。在SPI模式下,连接到SPI flash数据输入引脚;在SelectMAP模式下,该引脚是一个多功能引脚作为D00数据输入引脚使用(D00是D[00-31]中的第一位);在其它模式下,该引脚可以被忽略悬空不连接。

8、D01_DIN(data input_双向):串行数据输入引脚。在serial和SPI模式下,该引脚从数据源接受串行数据送入FPGA中(连接该引脚到数据源的串行数据输出引脚);在BPI和SelectMAP模式下,该引脚是一个多功能引脚作为D01数据输入引脚使用(D01是D[00-31]的第二位);在其他模式下,该引脚被忽略。

9、FCS_B(flash chip select bar_输出):低电平有效,芯片选择输出使能SPI或者BPI的flash芯片。在SPI和BPI模式下,连接该引脚到flash的芯片选择输入处并且外部上拉一个≤4.7KΩ的电阻到VCCO_14;在其他模式下,该引脚输出高阻,可以悬空不连接。

BANK15:

1、FOE_B(flash output-enable bar_输出):低电平有效,输出使能控制信号控制一个并行NOR flash。在BPI模式下,连接该引脚到flash的输出使能的输入处并且外部上拉一个≤4.7KΩ的电阻到VCCO_15;在其他模式下,该引脚输出高阻,可以悬空不连接。

2、FWE_B(flash write-enable bar_输出): 低电平有效,写使能控制信号控制一个并行NOR flash。在BPI模式下,连接该引脚到flash的写使能的输入处并且外部上拉一个≤4.7KΩ的电阻到VCCO_15;在其他模式下,该引脚输出高阻,可以悬空不连接。

3、ADV_B(address valid bar_输出): 低电平有效,地址有效输出信号控制一个并行NOR flash。在支持地址有效输入的带flash的BPI模式下,连接该引脚到并行NOR flash的地址有效引脚并且外部上拉一个≤4.7KΩ的电阻到VCCO_15;在不支持地址有效输入的带flash的BPI模式下,不连接该引脚;在其他模式下,该引脚输出高阻,可以悬空不连接。

4、RS0,RS1(revision select_输出):这两个引脚是版本选择输出引脚,是用来驱动一个并行flash较高级的地址线。通常,在配置期间这两个引脚都是高阻态。当configFALLback选项被使能,并在fallbank配置进程期间检测出配置错误信号,FPGA的RS0,RS1输出低电平;当用户要求MultiBoot配置被初始化,在MultiBoot配置进程期间,RS0,RS1处于一个被用户定义的状态。在fallbank未被使能且MultiBoot未被使用或者在SPI模式下,RS0,RS1引脚输出高阻,可以悬空不连接。

五、FPGA启动顺序

Step 1 设备上电(Device power-up)

1.VCCINT—FPGA内核电压(0.9V or 1V);

2.VCCBATT—AES密码存储器备用电源,不使用时应该被连到VCCAUX或者GND;

3.VCCAUX—辅助电源(1.8V);

4.VCCAUX_IO_#--I/O口辅助电源(1.8V or 2.0V);

5.VCCBRAM—FPGA bank RAM电源;

6.VCCO_0,VCCO_14,VCCO_15—配置板块0电源和多功能引脚板块14、15电源。

上电顺序:VCCO_0、VCCAUX、VCCBRAM、VCCOINT。

Step 2 初始化(Clear configuration memory)

在上电的期间配置存储器数据会被相继清零,并且在初始化期间,除了一些配置引脚和JTAG引脚外其它I/O口都呈高阻态。

Step 3 模式采样引脚(Sample mode pins)

模式采样引脚---M[2:0]。在主模式下,当INIT_B变成高,FPGA采样M[2:0]引脚来确定FPGA的工作模式并开始驱动CCLK时钟输出。这个时候,FPGA在配置时钟的上升沿开始采样配置输入引脚上的配置数据。

Step 4 同步(Synchronization)

在BPI、从SelectMAP和主SelectMAP模式下,总线宽度必须被先检测;而在从串行、主串行、SPI和JTAG模式下,总线宽度检测会被忽略。那么一个特殊的32位同步字0XAA995566必须被发送到配置逻辑,这个同步字让FPGA注意即将到来的配置数据和配置数据一起到来的内部配置逻辑。任何在同步信号前面的配置输入引脚上的数据都会被忽略,除了总线宽度自动检测时序。

Step 5 检查FPGA的ID(Check device ID)

在FPGA被同步后,一个FPGA ID检查必须通过在配置数据包被下载之前。对于一个不同的FPGA来说,这是为了防止配置比特码被格式化。在配置期间,如果一个ID错误产生,FPGA会尝试返回重新配置。FPGA的ID检查是被创建到比特码中的,是为了让这个步骤在很多设计中都是看不见的。

Step 6 下载配置数据包(Load configuration data frames)

在同步字被下载和FPGA的ID被检查之后,配置数据包也被下载。这个过程对于很多用户来说是看不见的。

Step 7 冗余量循环检查(Cyclic redundancy check—CRC)

在配置数据包被下载之后,FPGA会计算配置数据包的冗余量循环检查后的值。

1845

1845

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?