文章目录

参考文档:xapp587和UG470;

一、配置模式

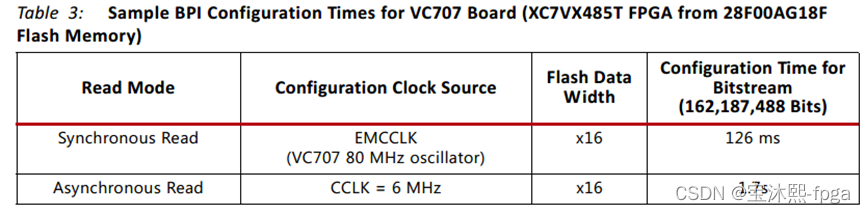

1、BPI configuration支持异步读配置模式和同步读配置模式,而同步配置的时间约为异步配置的8%;配置时间的计算见第3点;

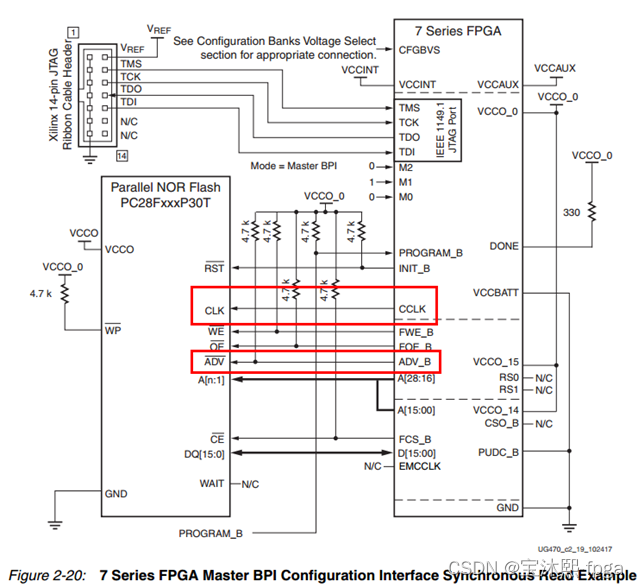

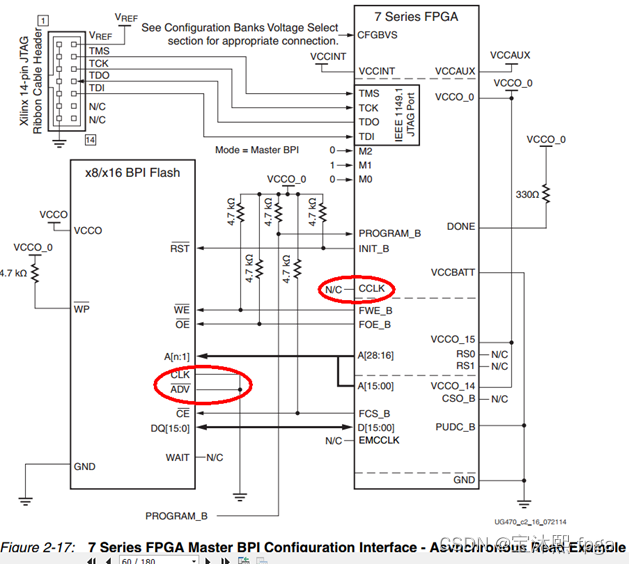

2、同步配置和异步配置在硬件连接上的区别为CCLK和ADV_B的区别,异步配置时flash这两个信号管脚接到GND,同步配置模式则是连接到FPGA(同步配置硬件连接支持异步配置),如下图所示:

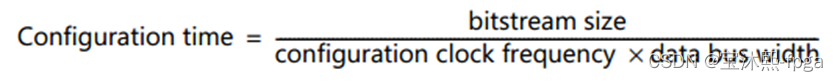

3、配置时间的计算与对比:同步配置模式下,CCLK可以达66MHz及更高,如果使用外部EMCCLK,配置时钟可达100MHz;而异步配置模式下,CCLK通常不超过10MHz;配置时间计算公式如下:

二、BPI flash的选择

1.选择BPI注意事项

1.根据应用选择存储容量;

2.根据所需配置时间选择FLASH数据位宽(同步读配置只支持16bit位宽的flash);

3.选择flash I/O电压范围;

2.支持同步读配置的FLASH

仅有MICRON公司的G18F和P30后缀系列FLASH支持同步读配置模式中的写命令时序:

1.G18F后缀的FLASH如:28F00AG18F;

2.P30后缀的FLASH如:PC28F00AP30EFA;

3.BPI FLASH在ISE中的设置

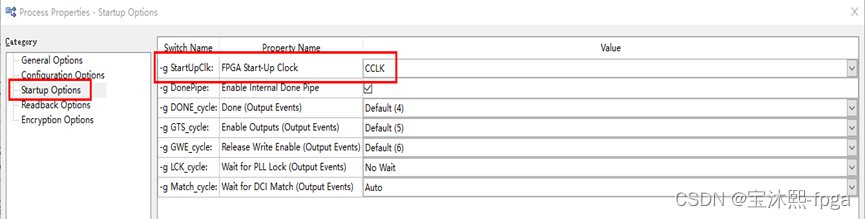

1、在ISE中,如使用同步读配置模式,需要右击“Generate Programming File”打开“Process Properties”,将“-g StartupClk”设置为“CCLK(默认就是)”,将“-g BPI_sync_mode”选择为“Type1”或“Type2”(Type1=G18F,Type2=P30),其它“-g ConfigRate”、“-g Compress”配置速率与是否压缩根据实际情况更改;(只有7系列的FPGA可选“-g BPI_sync_mode”等配置,如SP6就没有);

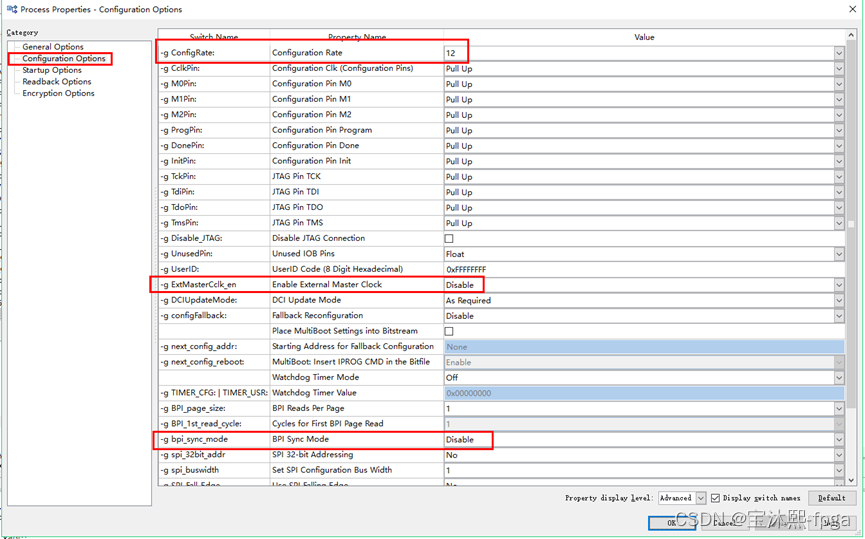

2、如果想使用EMCCLK时钟代替FPGA内部的CCLK时钟,则必须在“-g ExtMasterCclk_en”选项中选择分频设置,默认是disable,使用EMCCLK时必须更改;如下图所示:

三、使用命令行生成bit及mcs的步骤

a) 在开始菜单下找到ISE Design Suite 32/64bit Command …的命令输入界面;

b) 生成bit的命令:bitgen.exe -w -g StartUpClk:CClk -g Compress -g ConfigRate:12 -g BPI_sync_mode:Type1 -g ExtMasterCclk_en:div-1 -g BPI_page_size:1 -g BPI_1st_read_cycle:1 G:\project\CODE\K7\CLTOP.ncd

G:\project\CODE\K7\CLTOP_xxxx.bit

注:以上代码中,根据实际情况更改橘黄色参数;红色字体是路径,根据实际情况更改;TOP.ncd是生成bit需要的ncd文件,TOP_xxxx.bit是生成的bit名字。

c) 生成mcs的命令:Promgen -w -p mcs -c FF -bpi_dc parallel -data_width 16 -o C:\Users\Administrator\Desktop\flash_file_name -s 131072 -u 00000000 C:\Users\Administrator\Desktop\xc7k325t_u1_top.bit

注:以上代码中,根据实际情况更改黄色参数,16是flash数据位宽,131072是flash的存储容量,计算方式为:131,072 x 1,024 bytes x 8 bits = 1,073,741,824=1Gb,00000000是BPI flash的起始地址;红色字体是路径,根据实际情况更改;flash_file_name是生成的mcs名字,xc7k325t_u1_top.bit是生成mcs需要的bit文件。

四、在VIVADO中设置BPI configuration模式

a) 首先打开已编译完成工程的implementation,即open implementation design;

b) 然后在设置(settings)-->Bisttreamconfigure additional bitstream settings;

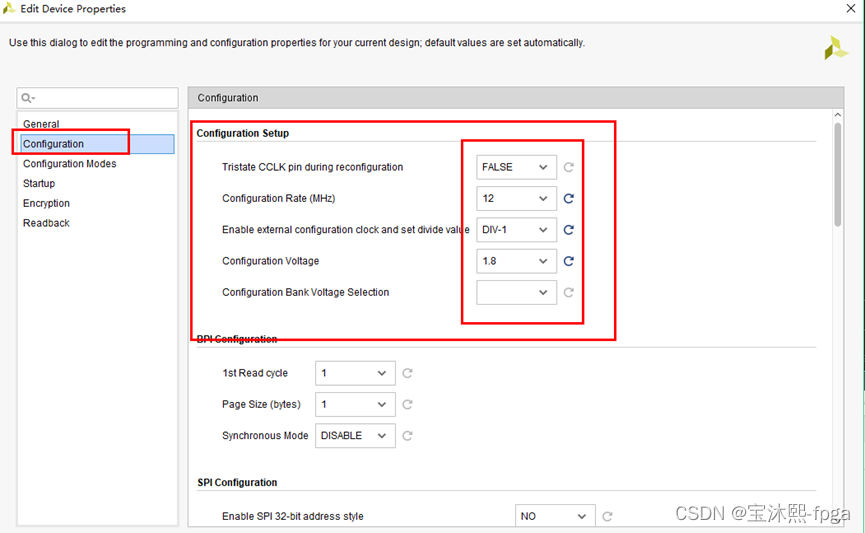

c) 根据应用设置CCLK、Configuration Rate、enable external configuration clock…、configuration Vlotage、configuration modes等等,如下图所示:

注:

1、configuration rate这项,如果不更改默认是3MHz,你会发现固化程序后,FPGA会在几秒甚至十几秒才会启动(done信号拉高);而该时钟如果设置的过高,如33MHz这种,FPGA可能在上电后根本启动不了,因为速率过高导致数据出错(FPAG的启动过程可以参考我前面的文章:xilinx 7系列FPGA配置、速率比较、专用管脚说明及启动顺序等介绍–>第5节);一般我设置为12MHz比较合适。

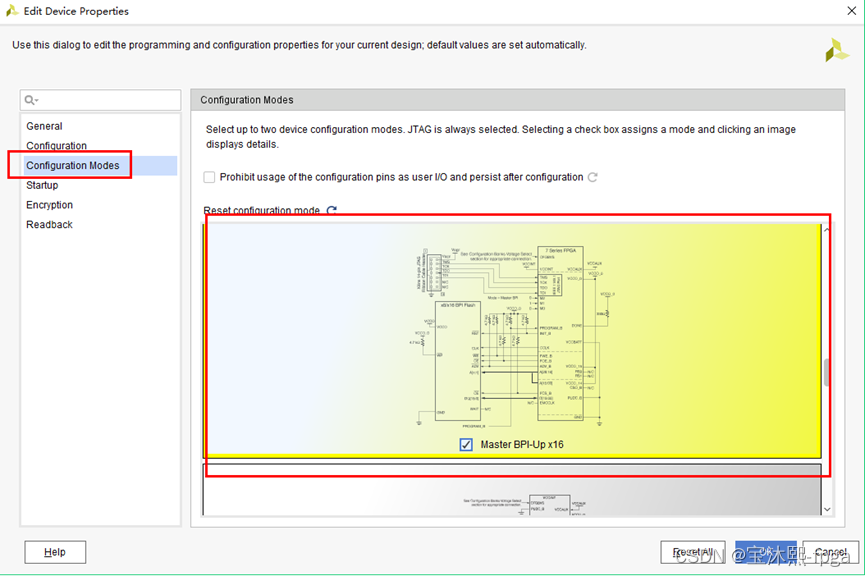

2、configuration modes这项,默认勾选了JTAG的模式,而其他模式如x8/x16这些需要手动选择,如果不勾选,在生成mcs文件时,可能会报错误导致生成mcs文件失败。

3、在general这个选项下,还有个压缩选项可以选择,默认是不压缩的,我建议是选上;举个例子,V7_690T的bit在不压缩的情况下大小约为27MB,而JTAG仿真器的下载速率一般是3MHz或6MHz,咱们选6MHz,27M*8bit/6Mb≈36秒,加上其他启动步骤、校验等等,时间算40秒上下,这个时间很长了;如果是个程序不大再压缩了,bit可能只有4MB,时间也只需要5~6秒,大大节约了时间。

以上的选项设置了都可以在xdc文件中查看。

1242

1242

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?