提示:文章写完后,目录可以自动生成,如何生成可参考右边的帮助文档

文章目录

前言

`主要介绍和整理了ZYNQ系列FPGA设计注意事项,以及PS部分如何分配外设等等。

注:该文档主要是针对ZYNQ的PS部分设计,仅个人找的一些资料和自己的理解,可能会有误。

一、硬件设计注意事项

1、PS_SRST_B信号

a.信号说明

系统调试复位,低有效(Debug system reset,active low),按理说应该在上电时强迫给一个复位,但直接上拉不控制也可以正常工作,这是因为下载SDK程序时,勾选“ssystem reset”这个选项,一样会给PS system进行复位;

b.硬件设计注意事项

PS_SRST_B(对应网络 PS-RST) 通过电阻上拉到VCC18 (Bank PS501 对应的电压是 1.8V), 同时连接到JTAG(14PIN) 接口的INIT 管脚上( 场效应管漏极开路OD 门, 参考 xtp185-zc702-schematic-rev1-1.PDF ds593.pdf );

注:ug865-Zynq-7000-Pkg-Pinout.pdf 文件中 ASCII Pinout Files 指定的链接地址包含各个封装对应的管脚定义文件。

2、PS_POR_B 信号

a.信号说明

PS_POR_B 是上电复位信号,低有效(Power on reset,active low);

b.硬件设计注意事项

1.通常使用TPS3808G33复位芯片控制该复位信号;

2.注意不同电平电源的上电顺序,PS_POR_B 应由最先上电的那组电源驱动;

3.PS_POR_B 信号在上电过程中应保持低电平,在最后一组电源(last power supply ramp)上电达到250mv 后开始,避开 Lockdown Window 时间区域变为高电平;

4.不要用 PS_SRST 控制 PS_POR_B 上电复位,会丢失软复位上电状态(CPU寄存器中);

注1:参考: ug585-Zynq-7000-TRM.pdf page 164, must be held Low during PS power supply ramp-up.Note: PS_POR_B must not be de-asserted during a certain timing window relative to when the

last PL power supply starts to ramp. Asserting PS_POR_B during this window can cause a

lock-down event. Refer to section 6.3.3 BootROM Performance: PS_POR_B De-assertion

Guidelines, page 178 for more details.

注2:参考 ug585-Zynq-7000-TRM_.pdf Page 164,查看上电顺序。

3、PS_CLK信号

PS_CLK是给PS提供工作时钟的管脚,LVCMOS电平,范围是30~60MHz,通常选用33.33333MHz,这是因为DDR3=1600MHz(33.33333*48)或者1066.666667MHz(33.33333*32);ARM/CPU=666.66666MHz(33.33333*20),都可以由33.33333MHz倍频上去。

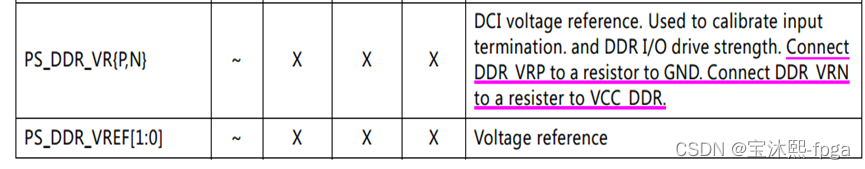

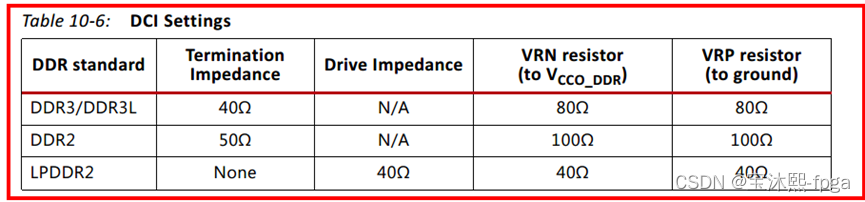

4、DDR_VRP与DDR_VRN

DDR_VRP与DDR_VRN的设计:(参考文档UG585)

注:DDR_VRP通过电阻连接到GND,DDR_VRN通过电阻连接到VCC_DDR;电阻值见下图;

二、启动方式和MIO控制

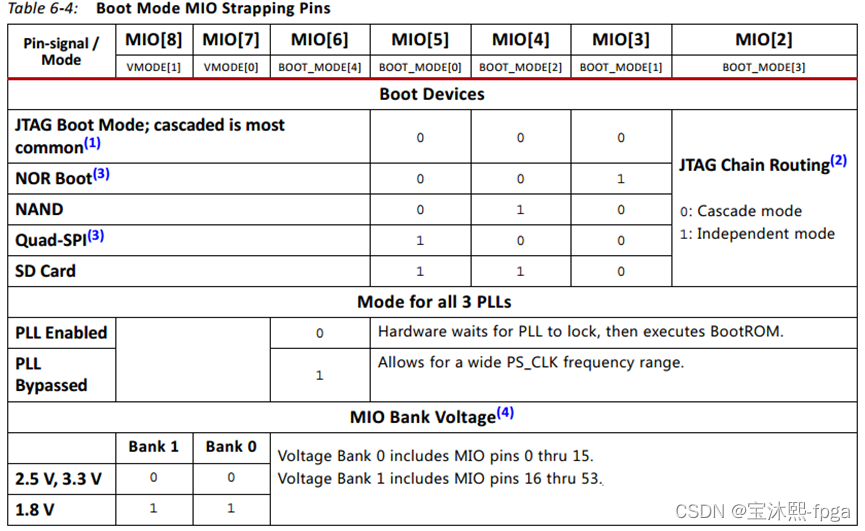

1.启动方式

ZYNQ的启动方式配置(见下图):(参考UG585—P167)

通常设计时会把MIO2~MIO5设计成用跳线帽可选的状态,一开始使用JTAG模式,程序固化在FLASH里面之后,就会切换成QSPI模式启动,这时就可以使用电阻固定启动模式了。

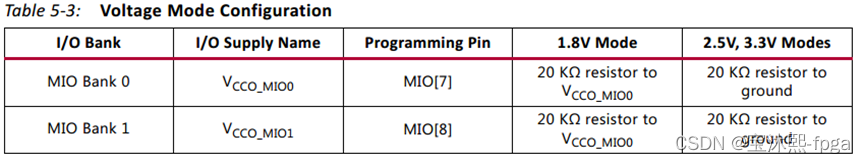

2.其他MIO控制

其它MIO引脚配置:(参考文档UG933)

三、ZYNQ的外设

1、必不可少的外设

1.系统时钟配置,包括PS_CLK和PL_CLK(当然,PL_CLK也可以由PS_CLK派生产生);

2.DDR3外设配置,用来执行PS应用程序;

2、其它外设(常用的)

1.EMMC外设:一般容量是Gbit,可以用来存放数据(存放缓冲数据或者使用select Map在线更新时存放其它FPGA的bit/bin文件);

2.SPI FLASH:用来固化ZYNQ程序(为什么不是必不可少的外设呢,因为ZYNQ的启动方式有很多,包括SPI、SD卡、nor flash与nand flash等等 );

3.串口:这个不用多说了吧,调试时一般都会用到,或者通过串口和其它设备通信等等;

4.千兆网:PS端最多可以挂2个千兆网,接口为RGMII或者GMII;

5.I2C外设:和其它设备通信;

6.4线SPI外设:和其它设备通信;

7.CAN外设:和其它设备通信;

8.USB外设:和其它设备通信;

......

四、ZYNQ的MIO管脚定义

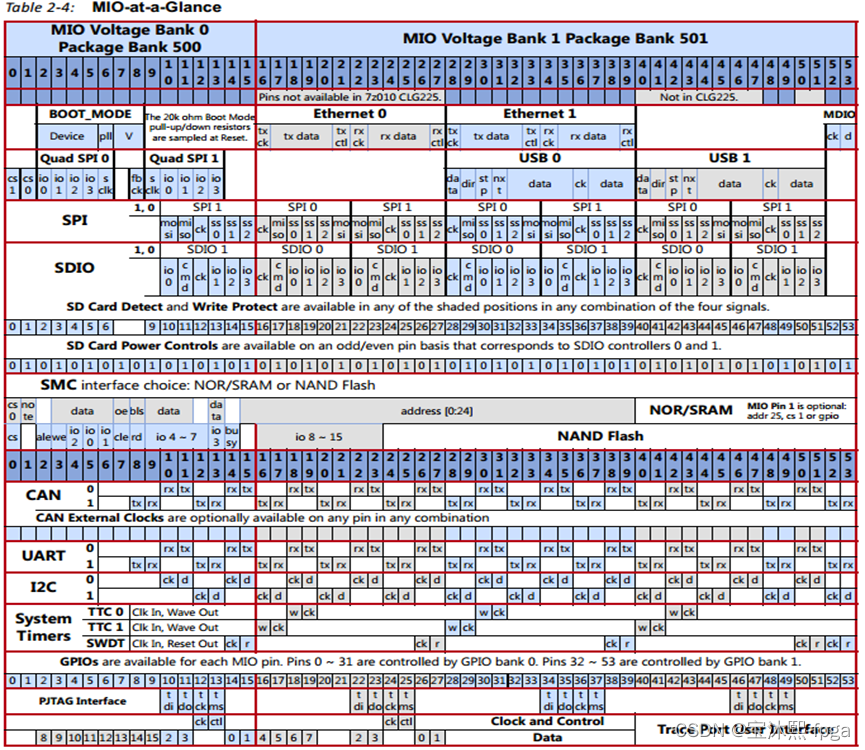

参考文档UG585-P53,表2-4;

五、ZYNQ的上电顺序

1、PS电源

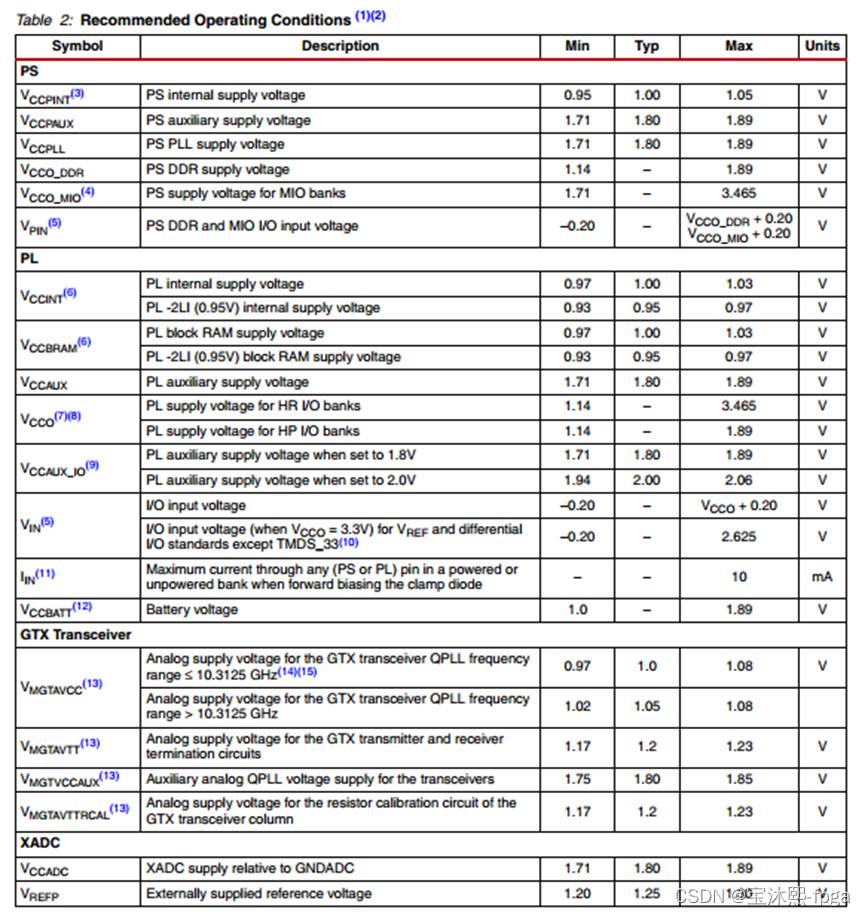

VCCPINT--> VCCPAUX--> VCCPLL--> PS_VCCO(VCCO_MIO0、VCCO_MIO1、VCCO_DDR);

2、PL电源

VCCINT --> VCCBRAM --> VCCAUX-->VCCAUX_IO--> VCCO;

3、各电源电压

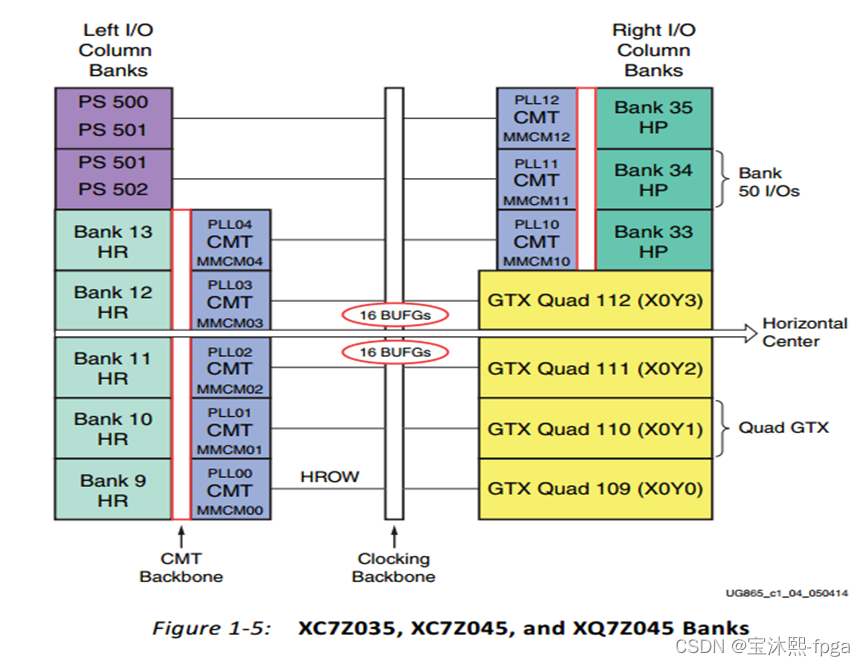

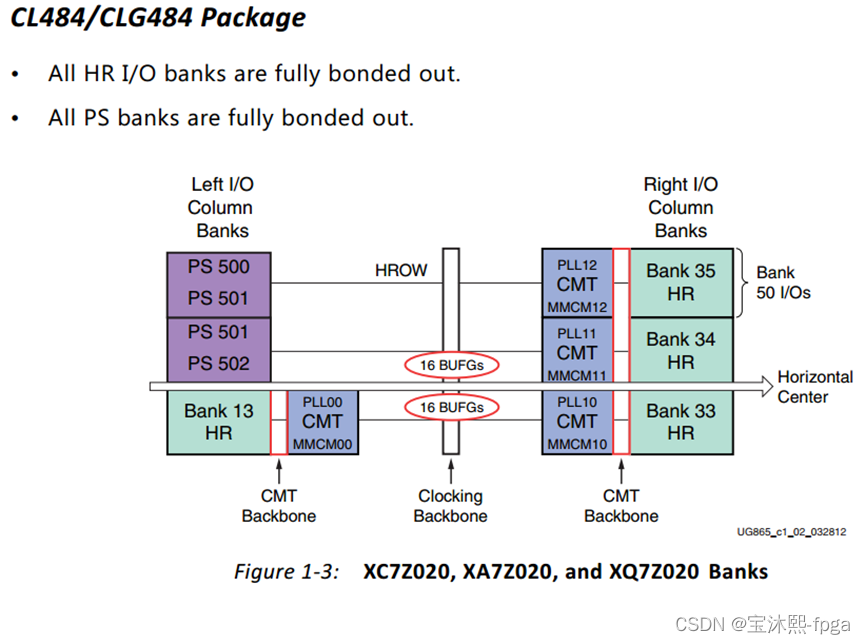

六、HP和HRbank分布

七、VIVADO XDC约束示例

1.注释XDC语句时,语句前加 “#”;

2.IO位置约束 :set_property PACKAGE_PIN <pin name> [get_ports <port>]

例:set_property PACKAGE_PIN U14 [get_ports i_clk]

3.IO电平约束 :set_property IOSTANDARD <IO standard> [get_ports <port>]

例:set_property PACKAGE_PIN LVCMOS33 [get_ports i_clk]

注:后期专门出一期IO约束、时序约束、电平约束、区域约束等的文章。

3249

3249

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?