实验目的

使用时钟ip核产生不同频率和相位的时钟信号。具体参数设置如下:

输入信号时钟:50Mhz

输出信号时钟:1.100Mhz 0deg

2.100Mhz 180deg

3.50Mhz 0deg

4.25Mhz 0deg

ip核设置

顶层文件

ip核例化

顶层文件设计

顶层文件设计

module clock_wizard(

input s_clk ,//系统时钟

input s_rst_n ,//系统复位

output clk_100M ,//输出100Mhz时钟信号

output clk_100M_180deg ,//输出100Mhz,相位180度的时钟信号

output clk_50M ,//输出50Mhz时钟信号

output clk_25M ,//输出25Mhz时钟信号

output locked

);

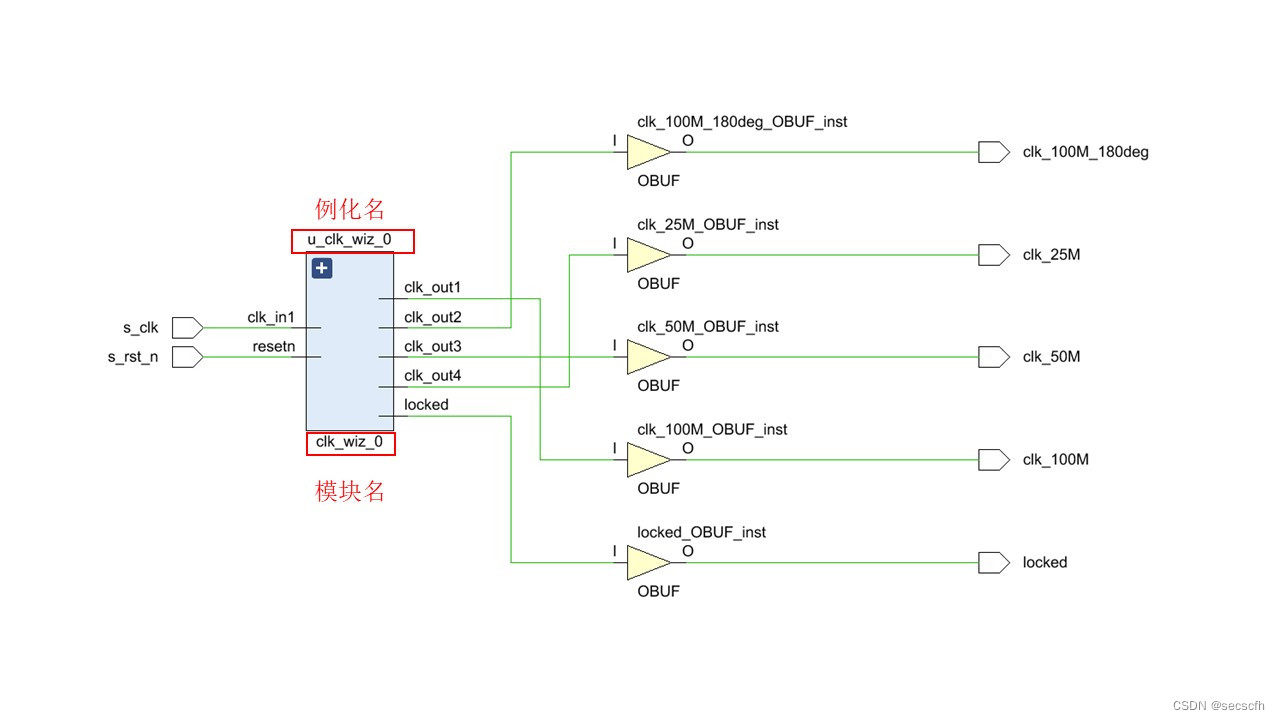

clk_wiz_0 u_clk_wiz_0

(

// Clock out ports

.clk_out1(clk_100M), // output clk_out1

.clk_out2(clk_100M_180deg), // output clk_out2

.clk_out3(clk_50M), // output clk_out3

.clk_out4(clk_25M), // output clk_out4

// Status and control signals

.resetn(s_rst_n), // input resetn

.locked(locked), // output locked

// Clock in ports

.clk_in1(s_clk)

);

endmodule

RTL图

测试文件

`timescale 1ns / 1ps

module tb_clock_wizard( );

reg s_clk;

reg s_rst_n;

wire clk_100M;

wire clk_100M_180deg;

wire clk_50M;

wire clk_25M;

wire locked;

initial begin

s_clk=1'b0;

s_rst_n=1'b0;

#200

s_rst_n=1'b1;

end

always #10 s_clk=~s_clk;//输入50Mhz的时钟

clock_wizard u_clock_wizard(

. s_clk (s_clk),

. s_rst_n (s_rst_n),

. clk_100M (clk_100M),

. clk_100M_180deg (clk_100M_180deg),

. clk_50M (clk_50M),

. clk_25M (clk_25M),

.locked (locked)

);

endmodule

仿真结果

来源参考:

来源参考:

正点原子

基于zynq7020核心板——领航者V2开发板

1140

1140

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?