协议规定,SCL时钟和SDA数据线都必须是双向开漏结构的,通过总线上的上拉电阻拉到逻辑高电平,空闲状态SCL和SDA应该被上拉到高电平,这样的结构可以实现线与的操作

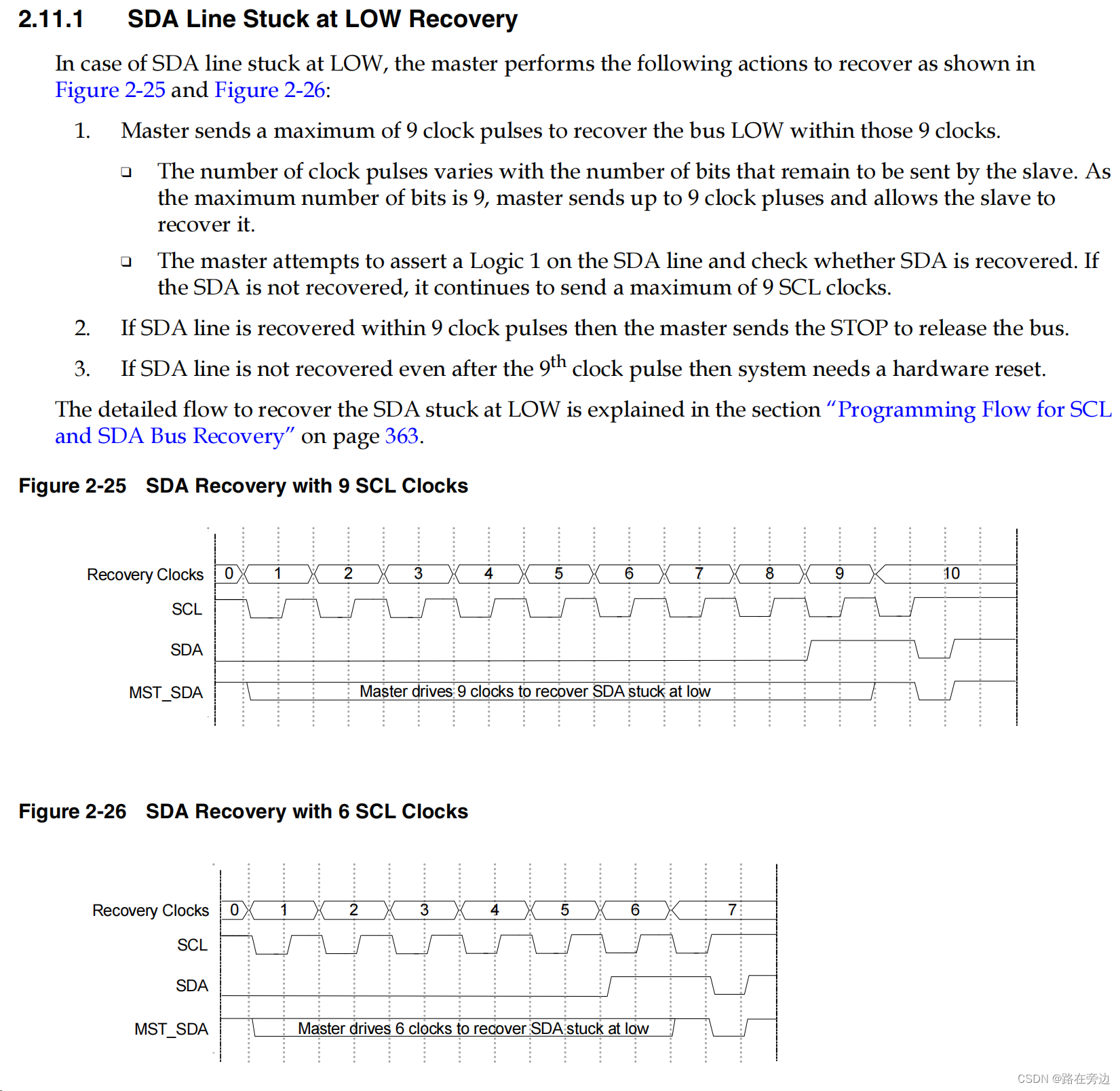

SDA被拉低:

主机会发送9个clk尝试拉高SDA,如果不能成功,需要硬件复位

SCL被拉低:

主机主动拉低SCL是合理的行为,在IP初始化配置的时候,可以选择时钟展频功能。

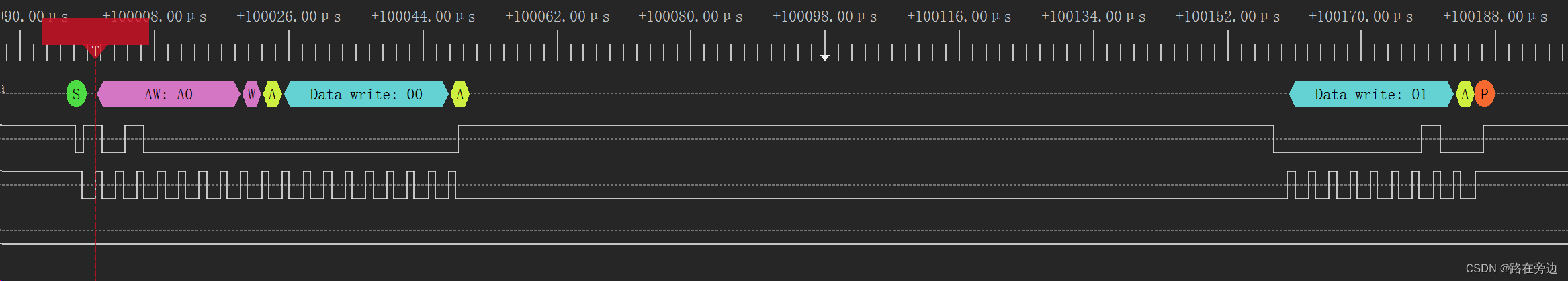

如下图在从机访问地址与写入数据之间加入一点延时,就会出现SCL被主机拉低的情况

其它情况的SCL拉低就要考虑代码实现是否合理了:

1、I2C是否被意外关闭了

2、是否在某个位置有while等待,一直无法跳出循环

其它内容可以参考:

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?