本文以STM32F429时钟架构切入Soc时钟一般配置过程。

一、时钟配置过程

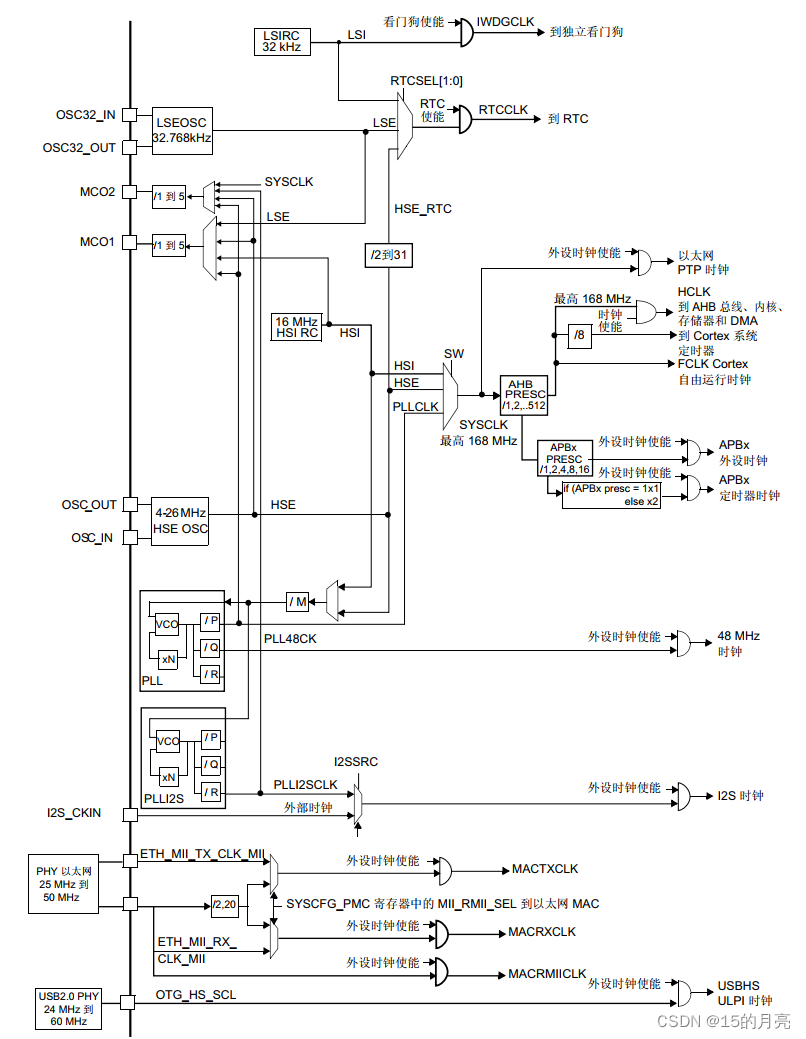

过程:系统上电,在启动文件中执行SystemInit()完成时钟配置,SystemInit()函数定义在系统文件system_stm32f4xx.c中,SystemInit()中的SetSysClock()函数配置系统时钟与分频因子,STM32F4xx时钟树框图如下图1所示

图1 STM32F4xx时钟树框图

二、时钟树讲解

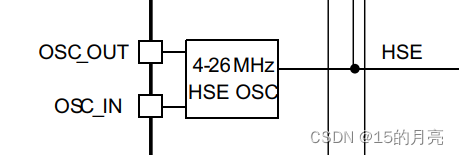

1、HSE时钟:high speed external clock signal,高速外部时钟,来源:有源晶振(1-50M),无源晶振(4-26M),HSE对应如下图2

图2 HSE时钟

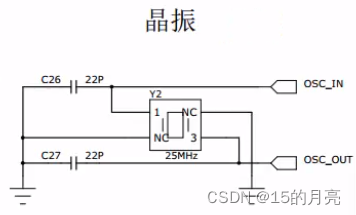

有源晶振单独使用一个脚OSC_IN,无源晶振两个脚使用,25M无源晶振电路图如下图3所示,使用了25M的无源晶振

寄存器控制:RCC_CR时钟控制寄存器的第16位:HSEON控制

图3 25M无源晶振电路图

2、HSI时钟:high speed Internal clock signal,高速内部时钟,来源:芯片内部,16M,当HSE故障时,系统时钟会自动切到HSI,直到HSE重新启动成功

寄存器控制:RCC_CR时钟控制寄存器的第0位:HSION控制

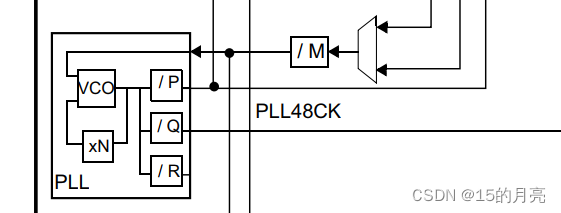

3、锁相环时钟:PLLCLK,来源:HSI,HSE,配置PLLSRC位选择来源

PLLCLK = (HSE/M)*N/P = 25/25*360/2 = 180M,F429推荐的最高频率180M,锁相环时钟框图对应如下图4

分频因子:M(2~63),P(2,4,6,8)

倍频因子:N(192~432),本SOC中N范围应在192-432之间

寄存器控制:RCC_PLLCFGR:RCC PLL配置寄存器,注意下图中经过M分频后的VCO须在1-2M之间,建议选择2M以限制PLL抖动,通过PLL可将HSE,HSI时钟倍频作为系统时钟使用

图4 锁相环时钟框图

上图中若是要除以Q,则输出的PLL48CK时钟用以给USB_FS,RANG以及SDIO提供时钟,如是F446型号则可满足上图中R分频通路

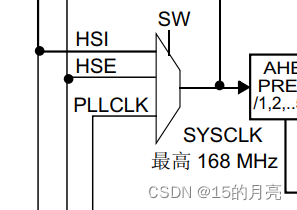

4、系统时钟:SYSCLK,最高180M,F407最高168M,来源HSI,HSE,PLLCLK,系统时钟框图对应如下图5

寄存器控制:RCC_CFGR时钟配置寄存器SW位,00:选择 HSI 振荡器作为系统时钟 01:选择 HSE 振荡器作为系统时钟 10:选择 PLL 作为系统时钟 11:不允许

图5 系统时钟框图

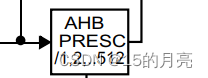

5、HCLK时钟:AHB高速总线时钟,最高180M。为AHB总线外设提供时钟,为Cortex系统定时器提供时钟(systick),为内核提供时钟(FCLK)

来源:系统时钟分频得到,AHB时钟框图对应如下图6

寄存器控制:RCC_CFGR时钟配置寄存器HPRE位

图6 AHB时钟框图

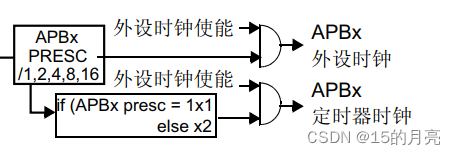

6、PCLK1时钟:APB低速总线时钟,最高45M。为APB1总线的外设提供时钟。2倍频后则为APB1总线的定时器提供时钟,最大为90M

来源:HCLK分频得到

寄存器控制:RCC_CFFGR时钟配置寄存器PPRE1位

7、PCLK2时钟:APB高速总线时钟,最高90M。为APB2总线的外设提供时钟。2倍频后则为APB2总线的定时器提供时钟,最大为180M,APB时钟框图对应如下图7

来源:HCLK分频得到

寄存器控制:RCC_CFFGR时钟配置寄存器PPRE2位

图7 APB时钟框图

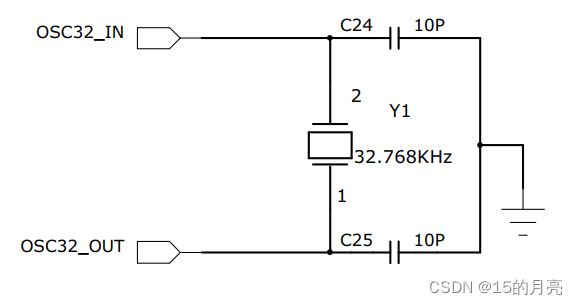

8、其它时钟之RTC时钟:

RTC:为芯片内部RTC提供时钟,RTC电路图如下图8所示

来源:HSE_RTC(HSE分频得到)、LSE(外部32.768KHZ的晶体提供)、LSI(32KHZ)

寄存器控制:RCC备份域控制寄存器RCC_BDCR:RTCSEL位控制

图8 RTC电路图

9、其它时钟之独立看门狗时钟:IWDGCLK,由LSI提供

10、其它时钟之I2S时钟:由外部引脚I2S_CKIN或PLLI2SCLK提供

11、其它时钟之以太网PHY时钟:由外接的PHY芯片如LAN8720提供,50M

12、其它时钟之USB PHY时钟:由外接的PHY芯片如USB33000提供

13、其它时钟之MCO时钟:把控制器时钟通过外部引脚输出,可以为外部设备提供时钟,MCO1,MCO2对应特定针脚,其中MCO1对应PA8,MCO2对应PA9,可通过示波器测量对应引脚观测时钟频率配置是否正确

MCO1时钟来源:HSI LSE HSE PLLCLK

MCO2时钟来源:HSE PLLCLK SYSCLK PLLI2SCLK

寄存器控制:RCC_CFGR时钟配置寄存器的MCOX的PREx位

三、时钟函数编写

STM32F4XXX系统配置函数SystemInit()使用了SetSysClock函数,可在SetSysClock函数中通过宏定义USE_HSE_BYPASS定义有源晶振,不使用该宏则为无源晶振

配置过程:

1)使能HSE,并等待HSE稳定

2)配置AHB APB2 APB1总线的预分频因子

3)配置PLL的各种分频因子,并使能PLL

4)选择系统时钟来源,一般选择锁相环时钟作为系统时钟来源

注意:根据公式PLLCLK = (HSE/M)*N/P可以用HSE进行超频配置,HSI也可以,一般不用,因为HSI精度不高需要补偿

更多IC设计,验证,嵌入式等精彩内容,欢迎关注公众号:最炫ICerr

参考文献:

1、STM32F4xx中文参考手册

2、STM32F4xx-Cortex_-M4内核参考手册

本文详细介绍了STM32F429的时钟配置流程,包括HSE、HSI、PLL和系统时钟的设置,以及各个时钟源的选择和控制。重点讲解了时钟树结构和如何通过SetSysClock函数配置不同时钟。

本文详细介绍了STM32F429的时钟配置流程,包括HSE、HSI、PLL和系统时钟的设置,以及各个时钟源的选择和控制。重点讲解了时钟树结构和如何通过SetSysClock函数配置不同时钟。

2395

2395

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?