为了保证DDR3有很高的数据传输速度及高质量的信号完整性,JEDEC标准规定在设计DDR3的过程中必须满足下面的相应设计指标。

1、时序指标

在设计DDR3的硬件过程中,考虑很高的工作频率和需要保证走线长度值比较小的条件下,时延情况直接影响着总线的时序。故复杂严格的时序要求直接影响着DDR3芯片设计的结果。

(1)数据选通的建立和保持时间

建立时间(Setup time)是指接收端口在接收数据时,触发器的时钟信号上升沿到来之前,数据稳定不变的存在时间。若建立时间不够,那么数据信号不能在这个有效时钟信号沿将数据存入到存储器中去。

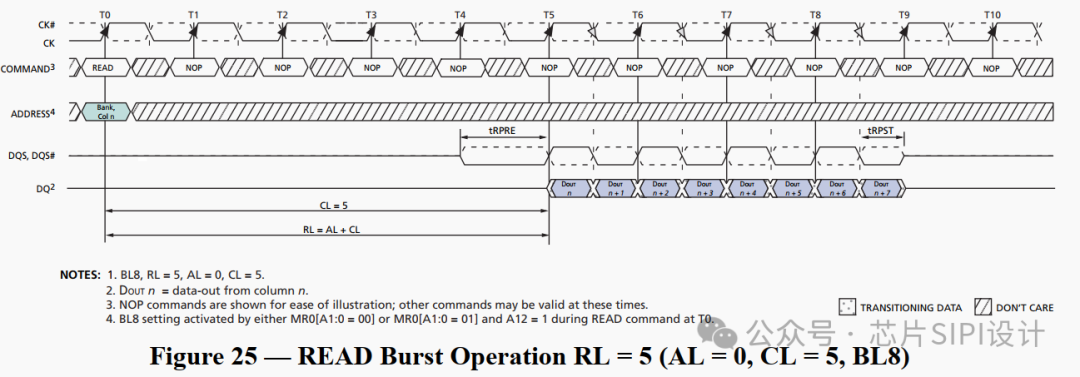

保持时间(Hold time)是指触发的时钟信号上升沿到来之后,数据信号持续这一状态不变的时间。同样保持时间不够时,也不能将数据存入到存储器中去。在写周期时,数据选通信号比数据信号要提前90度相位差,下两图分别为其写数据时序图和读数据时序图,在读周期时,数据选通信号和数据信号的相位差为0度并保持边缘同步的关系。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?