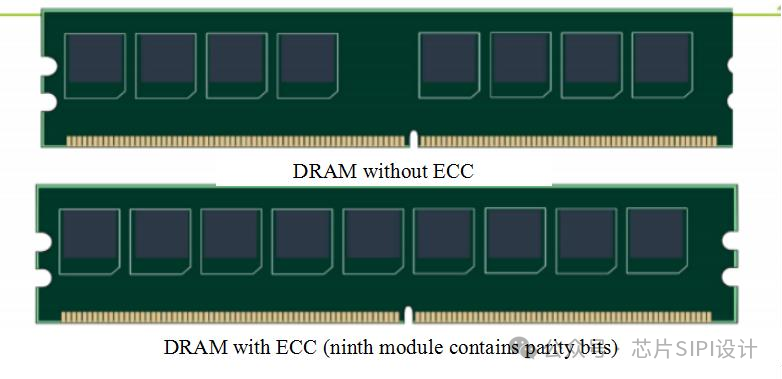

ECC是LPDDR4新增的带有校验功能的模块,提高了LPDDR4在读写及掩蔽写操作中数据信息的可靠性,ECC模块是增加在存储阵列里的一个模块。数据到达ECC时为128比特,相对应的校验码为8比特,采用汉明码的算法可以对128比特的数据进行一位错码的定位与纠正,ECC模块在读写以及掩蔽写的操作过程中都能起到校验的作用。如图为带ECC功能与不带ECC功能的DRAM芯片,对比可以看到,ECC的DEAM的存储颗粒多一个,这个存储单元是用来保存ECC模块中计算得到的校验位的数据信息的。ECC模块的加入使得数据在稳定性上得到了提升,由于LPDDR4中占用面积最大的为存储阵列,ECC的加入就必须增加相应的存储阵列用来存储校验码,内存颗粒自然会变多但是ECC模块对芯片的尺寸几乎是没有影响的。LPDDR4本身即为低功耗的设备,工作电压仅为1.1v,ECC对功耗的影响也是微乎其微的。

对于存储器来说,数据只有先写入存储单元才能做读取操作。ECC在写入的操作中,128比特数据信息经过编码得到8比特校验码信息,一共136比特在写入时钟的高电平被锁存传输至存储单元。在读取操作的过程中,存储单元中本来就保存着136比特信息,其中128比特的读出数据以及8比特的校验码,校验码是用来对128比特数据信息做检测与纠错,当128比特数据到达ECC模块经过编码得到8比特校验码,为了校验数据在读出存储单元时是否出错,将新得到的8比特校验码与存储单元里本来就保存的8比特校验位做异或处理,最终得到8位校验码如若每一比特都为0,则

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

922

922

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?