充分提升DRAM RAS性能之一的有利工具是ECC.

ECC基本分为:1): on die ECC 2): link ECC 3): side-band ECC 4): inline ECC

on-die ECC

On-die ECC是确保array里面的data的正确性,在出现array里面的data出现错误的时候进行纠错。

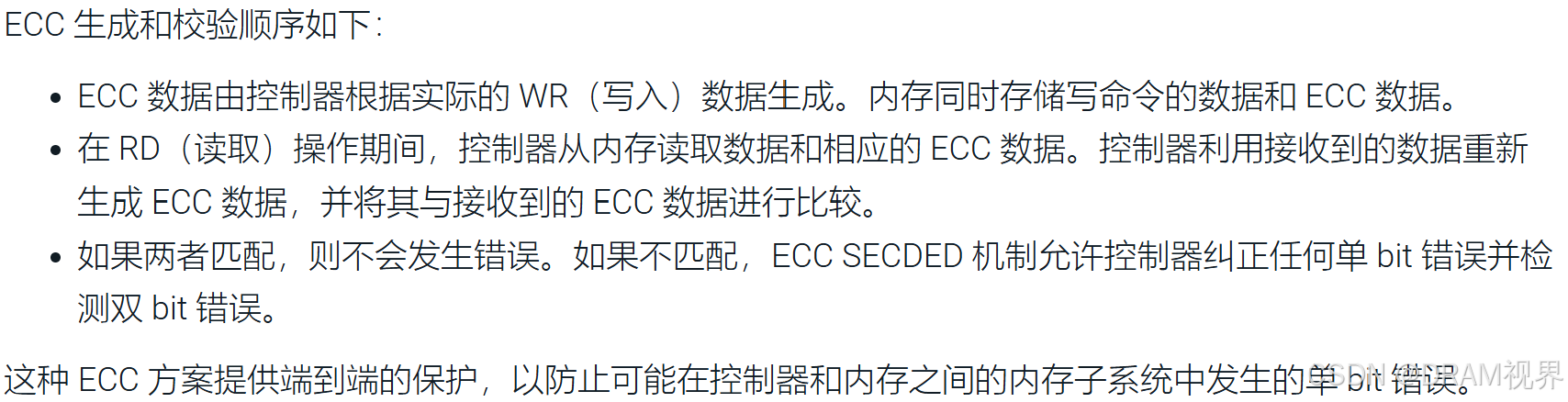

在LPDDR4的spec里面,没有定义on-die ECC,但是大部分的DRAM厂商实际上在LPDDR4里面实现了on-die ECC功能。在DDR5的spec里面已经明确定义了on-die ECC的spec要求跟ECS的要求。on-die ECC是指die内做ECC校验。控制器发送data到DRAM内部,DRAM内部自己产生ECC parity, 并将ECC parity存储到DRAM内部(注意这是DRAM内部自己的行为), 然后控制器从DRAM读取数据的时候,DRAM内部把ECC parity从array里面读出来进行内部校验并进行纠错从而保证读出来的data的正确性。

Link ECC

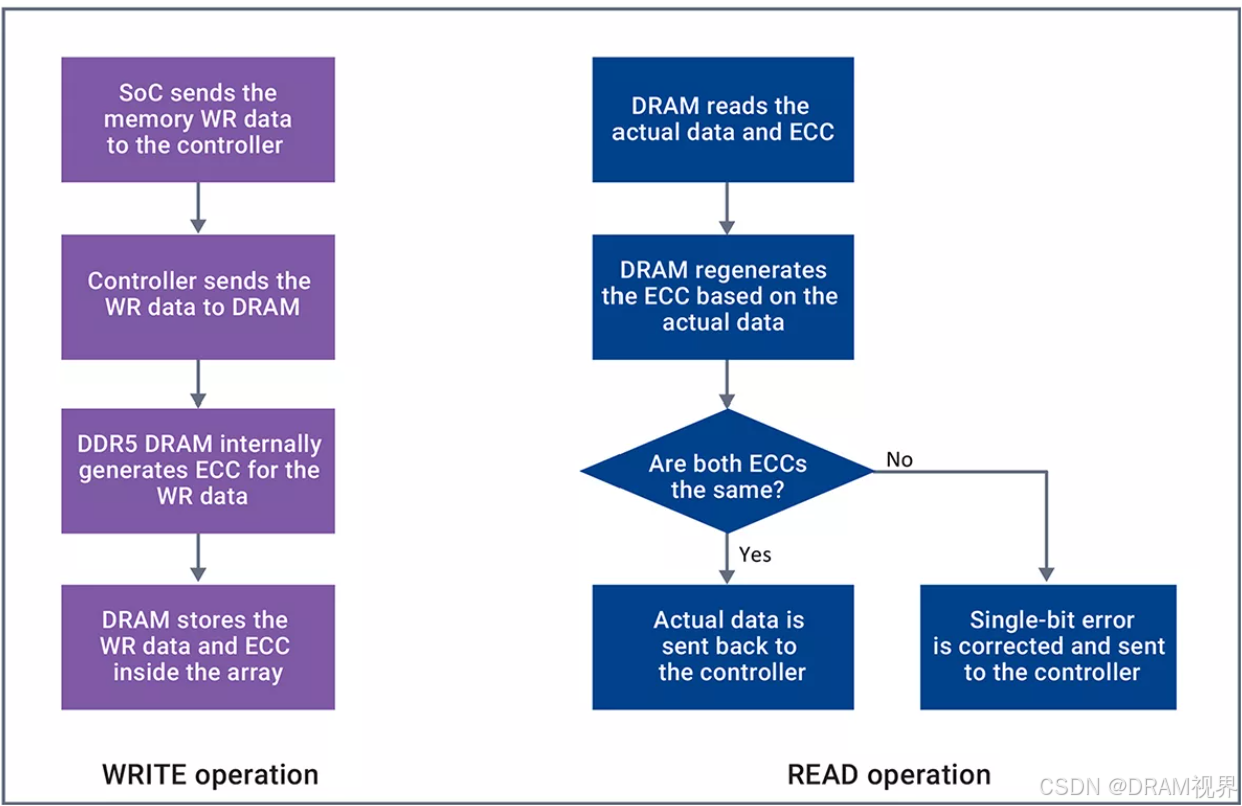

在LPDDR5开始spec定义了link ECC. Link ECC是用来check SOC跟DRAM之间传输过程中出现的潜在的error并进行纠错 控制器会将write data跟控制器自己计算的parity一起送到DRAM端,DRAM端接受到write data跟ECC parity后,DRAM会根据write data自己也再算一遍ECC parity,自己计算的跟控制器送过来的一样,就说明data在传送过程中没有出错。如果不一样,就进行纠错,并将data写入DRAM。但是ECC parity不会写入到DRAM中。从而不会占用更多的存储单元。ECC parity只是中间的临时产物。反之对于read操作同样的sequence。只是判断的逻辑在控制器那边,DRAM只需要送出ECC code给到控制器即可。

Side-band ECC

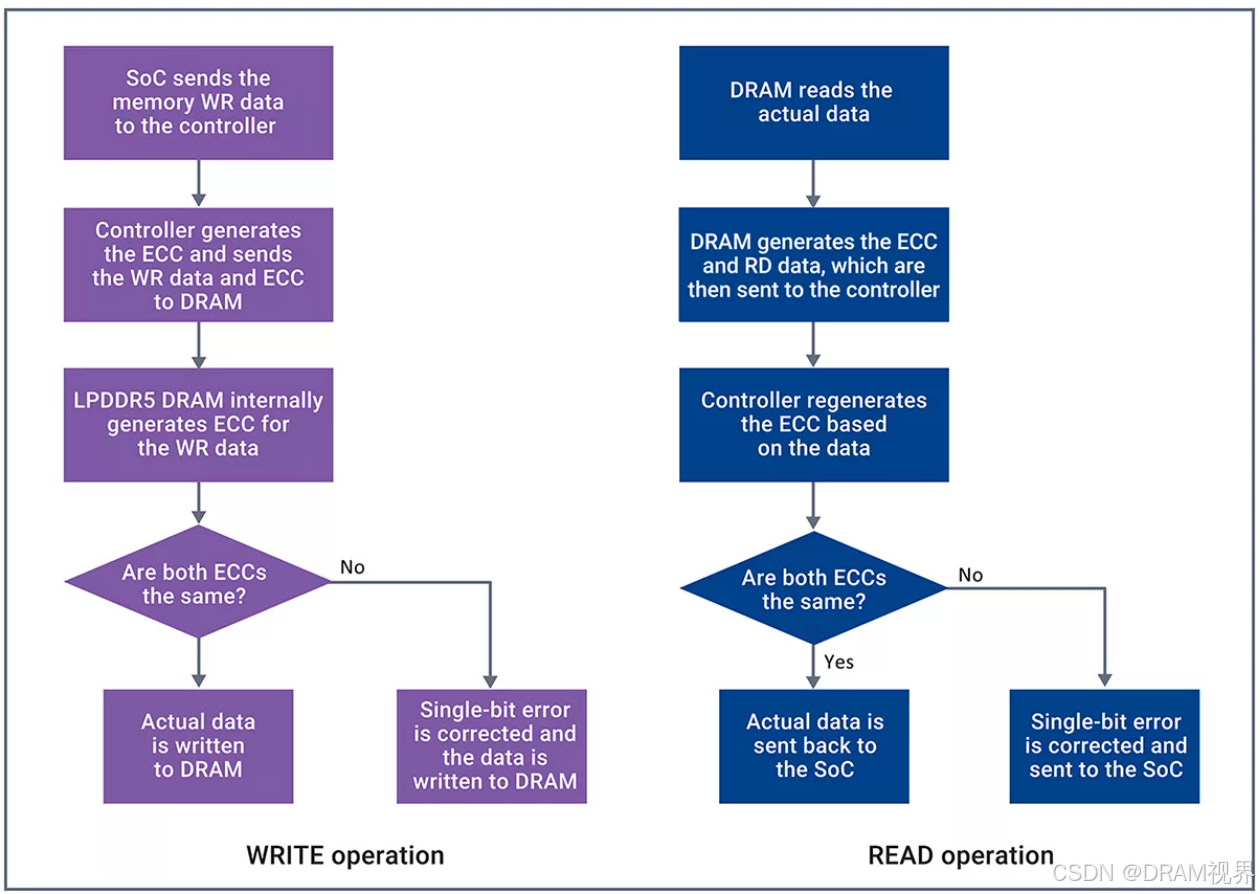

DIMM上多出来的ECC颗粒,就是用的Side-band ECC。

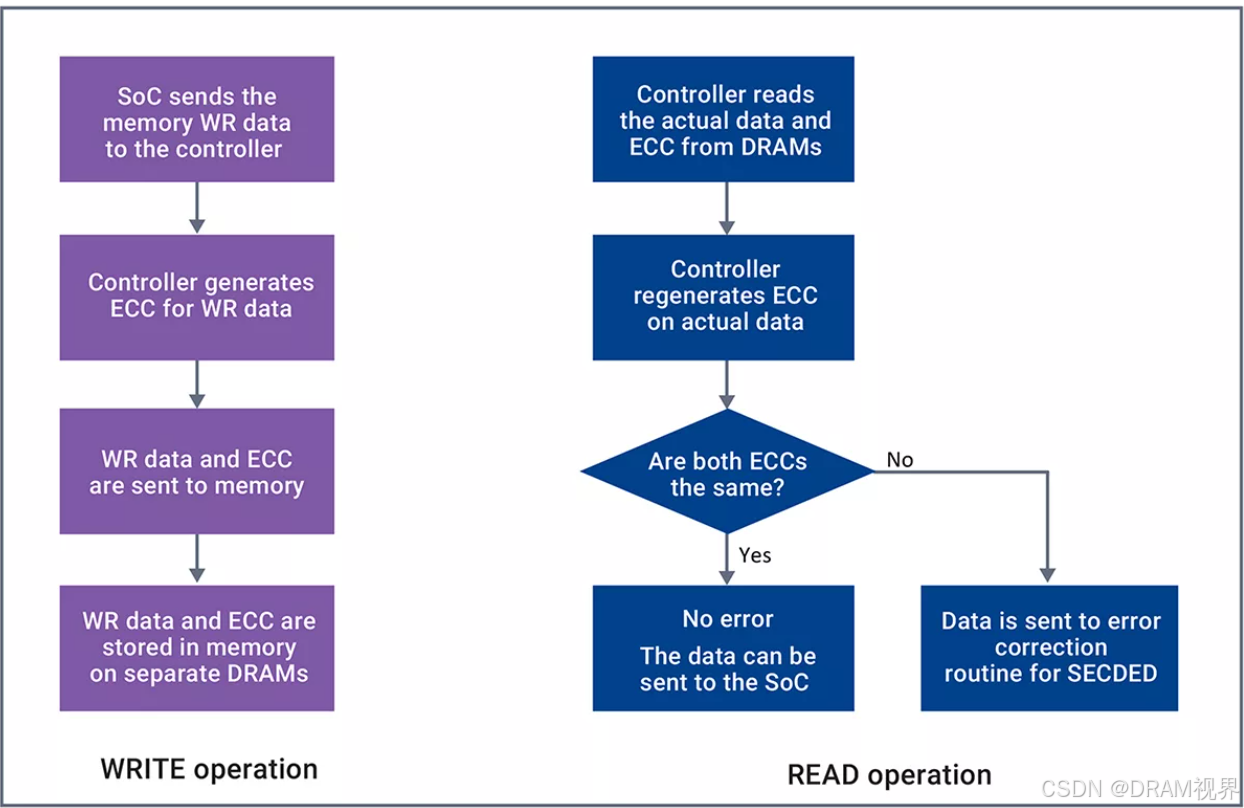

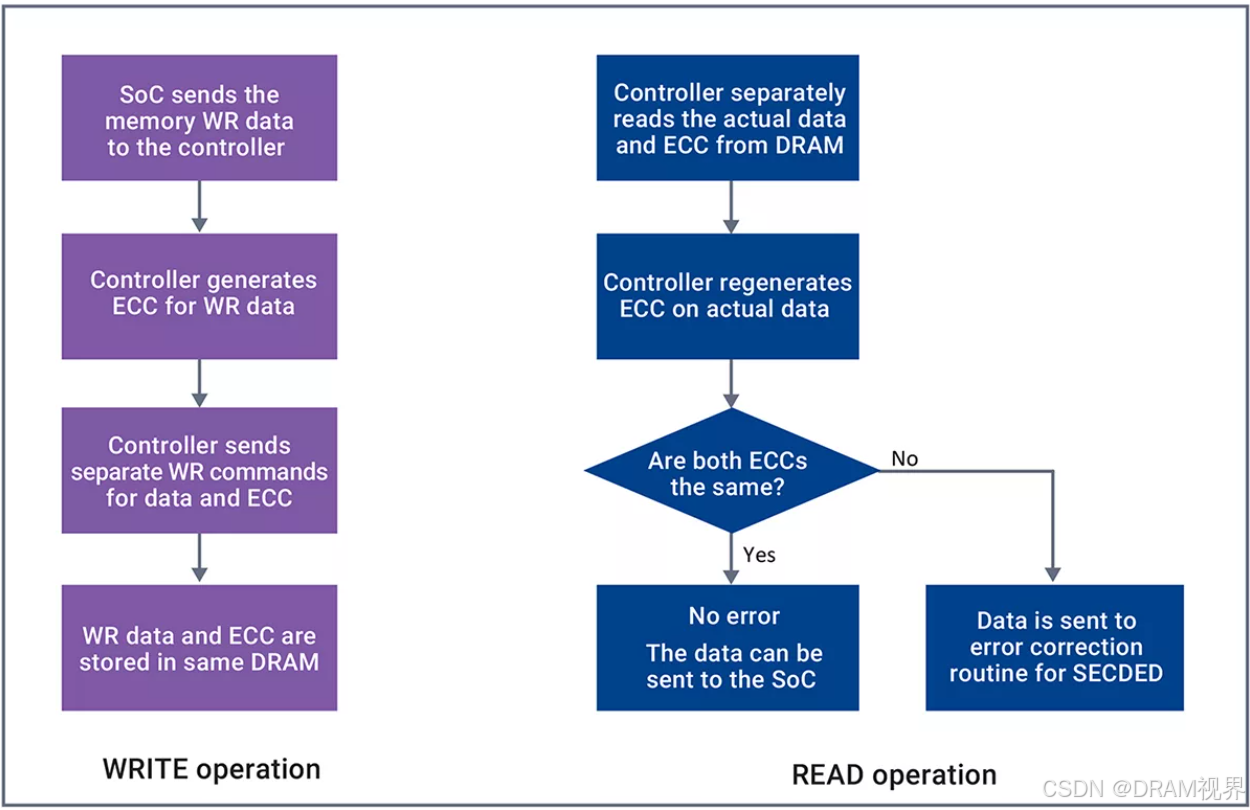

控制器产生的write data跟ECC data会同时写入到DRAM中,只是被写入到不同的DRAM中。读取的时候也会从不同的DRAM中把data跟ECC code同时读取出来进行校验。

Inline ECC

Inline ECC不增加DRAM颗粒数量,但是需要增加DRAM的array的容量。ECC code也是存储在DRAM memory里面的。但是差别是:Inline ECC的ECC parity的data是单独的write/read command进行操作的,即要分两次write or read来完成校验工作。第一次读取本身的data,第二次读取ECC code.

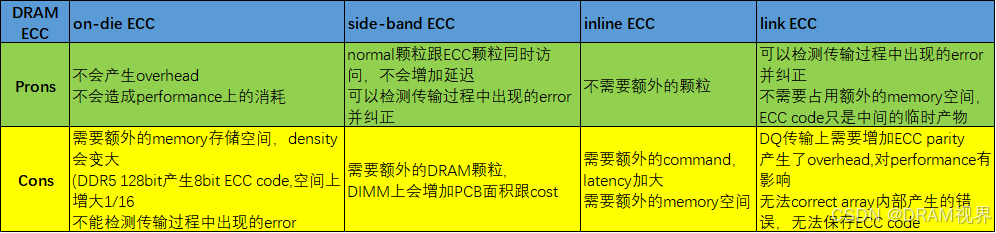

我们具体对比一下四种ECC方式的差别,prons vs cons:

而DDR5一般采用on-die ECC + side-band ECC方式来提供强大的RAS能力。LPDDR5一般采用on-die ECC+link ECC来确保array跟传输线上的quality。那为何两种方案是不一样的?RDIMM对RAS性能要求更高,side-band ECC能提供强大的chipkill能力,而LPDDR5的speed更高,link ECC带来的些许overhead能通过speed上的优势来弥补。

729

729

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?