经过数十年的快速发展,大规模集成电路已成为信息技术的核心。过去,集成电路(IC)制造工艺始终遵循摩尔定律发展——7纳米工艺已进入量产阶段,5纳米和3纳米工艺也在稳步推进。每一次工艺节点的突破都带来了性能提升与功耗降低。然而,随着IC制造工艺复杂度大幅增加,流片成本急剧上升。例如,新一代图形处理器(GPU)、中央处理器(CPU)或片上系统(SoC)的设计成本高达3亿美元,这对多领域芯片设计提出了巨大挑战。

摩尔定律的放缓与停滞以及丹纳德缩放的失效加剧了这一问题。具体而言,自2000年起,摩尔定律的增速逐渐放缓。到2008年,其预测与实际芯片性能的差距扩大了15倍。丹纳德缩放则从2007年开始显著放缓,并于2012年近乎停滞。随着工艺升级,芯片性能与功耗优化的性价比逐渐降低。学术界与产业界普遍认为“后摩尔时代”即将到来,这意味着长期研究需围绕“MoreMoore”技术展开,并在设计、器件架构、封装工艺甚至后CMOS新型器件等全产业链环节持续创新,以维持性能、功耗、面积与成本(PPAC)的平衡。

作为“MoreMoore”框架下的集成技术,Chiplet设计技术因从三方面解决上述问题而备受关注:

w异构集成:通过内部互连技术将多个模块化芯片(以Die为主要形式)集成至单一封装中,开发专用异构芯片。该方案高效解决了规模、开发成本与周期问题。

w先进封装:借助25D、3D等先进封装技术实现高性能多芯片互连,提升系统集成度及性能与功耗优化能力。

w模块化优势:加速开发速度、降低门槛,使研发聚焦算法与核心技术,提升整体创新能力。

相比传统单片集成,Chiplet在多方面具备潜力,但其成熟与广泛应用仍面临挑战:

w接口与标准:异构系统的统一接口与标准需平衡性能、灵活性与市场竞争。

w封装技术:性能、功耗、成本等问题亟待突破。

wEDA工具链:支持Chiplet设计与实现的EDA工具链及生态系统的完整性与可持续性仍需完善。

目前,Chiplet已在高端技术企业成功应用。例如:

wHBM存储器:早期成功案例。

wFPGA领域:英特尔基于Chiplet的Agilex FPGA采用3D封装技术实现异构集成。

w高性能CPU:AMD的Zen2架构[8]将IO模块与处理器核心分离为多颗小芯片(7纳米、14纳米工艺),按需集成。

w网络芯片:英特尔(原Barefoot)的Tofino2芯片通过Chiplet集成交换逻辑芯片与高速SerDes芯片,实现128T交换能力。

Chiplet概述

传统IC设计主要通过两种方式升级产品:

1工艺微缩:将设计迁移至更小工艺节点以提升性能(PPA)。

2功能扩展:在同一工艺节点集成更多功能模块,降低掩膜与EDA工具成本。

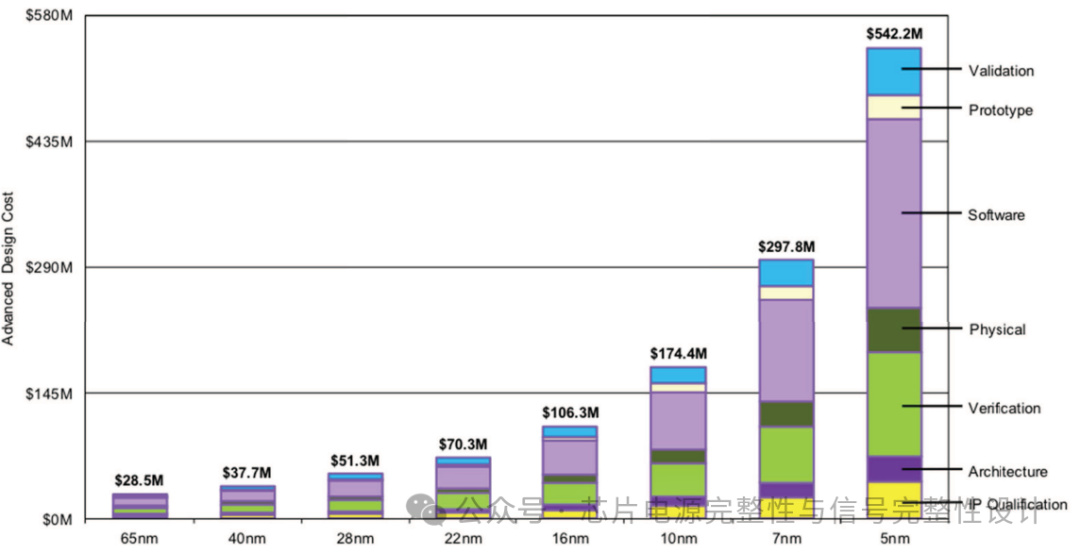

然而,随着工艺演进,设计成本因复杂度的提升而大幅增加。国际商业战略公司(IBS)数据显示,22纳米后每代技术设计成本增幅超50%(包括EDA、验证、IP核、流片等)。例如,7纳米工艺总设计成本约3亿美元,3纳米预计达15亿美元(如图)。此外,光刻机掩膜尺寸等技术限制使得单片集成在新工艺中的功能扩展难以为继。

在此背景下,Chiplet为未来芯片设计提供了可行路径。多芯片模块(MCM)技术(1980年代)已体现Chiplet思想,其通过基板连接多颗芯片以满足复杂系统需求,降低板级互连开销。近年来,英特尔、AMD等基于MCM技术开发了多款高性能芯片。但MCM主要关注底层封装,未解决异构集成中的高层问题(如互连标准、接口、工具与生态)。

2017年,DARPA在“电子复兴计划”中提出“CHIPS计划”,联合洛克希德·马丁、英特尔、Cadence等企业与学术机构,致力于开发集成不同功能Die的技术框架,通过中介层(Interposer)实现低成本、高灵活性的片上系统集成。

2018年底,Facebook等公司推动的开放计算项目(OCP)提出“开放领域专用架构(ODSA)”,旨在定义开放接口标准,构建Chiplet开放市场,支持跨厂商灵活组合。

为实现上述目标,软件工具链(如物理层、链路层、网络层的互连接口标准、先进封装技术、良率导向的EDA工具等)与典型应用研发成为关键。

Chiplet的优势

相比传统PCB集成与单片ASIC,Chiplet的优势体现在技术、成本与商业模式三方面:

技术优势:

w性能与功耗优化:通过重组小芯片实现领域定制,缓解摩尔定律放缓的影响。例如:

w网络芯片(如英特尔Tofino2)将高速SerDes模块与核心逻辑分离,优化布局与功耗。

w3D堆叠技术提升CPU与AI芯片的内存带宽,缓解“存储墙”问题。

成本优势:

w制造成本:小芯片面积小、良率高,整体成本显著降低。

w研发成本:通过复用已知合格芯片(KGD)缩短周期。AMD的32核EPYCCPU成本降低40%。

w风险控制:选择成熟芯片Die集成,减少流片次数与封装成本。

商业模式:

w创新加速:降低开发门槛,推动核心算法与技术突破。

w产业链重构:催生Chiplet供应商、集成商与EDA工具商三类角色。目前英特尔、美光等企业已占据重要地位,初创公司(如zGlue)则致力于填补产业链空白。

表1对比了Chiplet与传统技术的差异。Chiplet在性能、功耗与集成度上接近单片ASIC,成本与设计周期接近PCB技术,展现出巨大潜力。

表1Chiplet与传统芯片集成技术对比

集成技术 | Chiplet | 单片ASIC | PCB |

性能 | 高(按需选择) | 最高 | 低 |

功耗 | 低(按需选择) | 最低 | 高 |

集成度 | 较高 | 最高 | 低 |

成本(美元) | 千元-百万级 | 百万级 | 百元-千元级 |

设计周期 | 数月 | 12个月以上 | 数周 |

Chiplet的挑战

尽管Chiplet优势显著,其进一步发展仍面临以下挑战:

互连接口与协议

Chiplet间的互连接口与协议需平衡工艺匹配、系统集成、扩展性及性能指标(如带宽密度、每比特功耗)。当前接口主要分为两类:

1) 串行接口

wLR/MR/VSR SerDes:适用于PCB板级互连(如PCI-E、以太网),传输距离长、成本低,但功耗与面积劣势明显。

wXSR SerDes:面向Die-to-Optical Engine(D2OE),需复杂前向纠错(FEC),延迟与功耗较高。

wUSR SerDes:基于25D/3D封装实现超短距离(10毫米级)Die-to-Die互连,功耗低(如Kandou Glass wing 112G USR SerDes达072pJ/bit),但专利技术限制其兼容性。

下表2对比了不同串行接口的特性:

表2. OIF 56G SerDes接口对比

SerDes类型 | MR/LR SerDes | VSR SerDes | XSR SerDes | USR SerDes |

应用场景 | 芯片间 | 芯片-模块 | Die-to-Die/Optical Engine | Die-to-Die |

传输介质 | PCB | PCB | 基板 | 硅中介层 |

编码方案 | PAM4, ENRZ | PAM4 | NRZ | CNRZ-5 |

误码率 | 1E-4~1E-6 | 1E-10~1E-15 | 1E-10~1E-15 | 1E-10~1E-15 |

传输距离 | 500~1000 mm | 125/25 mm | 50 mm | 10 mm |

每比特功耗 | - | - | 5 pJ/bit | 3 pJ/bit |

2)并行接口

wAIB/MDIO(英特尔):适用于25D/3D封装(如EMIB、Foveros),带宽密度高。

wLIPINCON(台积电):基于InFO/CoWoS封装,无需PLL/DLL,功耗低。

wBoW(OCP):支持有机基板互连,分Base/Fast/Turbo三档,兼容性强。

下表3对比了并行接口的关键参数:

表3物理层并行接口对比

并行接口 | AIB Gen1 | MDIO Gen1 | LIPINCON | BoW-Turbo(3片) |

数据速率(GT/s) | 2 | 5.4 | 8 | 16 |

带宽密度(Gbps/mm) | 504 | 1600 | 536 | 1280 |

每比特功耗(pJ/bit) | 0.85 | 0.5 | 0.5 | 0.5(7纳米) |

典型应用 | Stratix 10 FPGA | - | VLSI演示 | GF样品 |

3) 其他接口

wTilelink:开源协议,解耦片上网络与缓存一致性协议。

wCCIX:专为CPU与加速器互连设计,支持缓存一致性。

wISF(Netronome):轻量级消息协议,支持异步存储访问。

封装技术

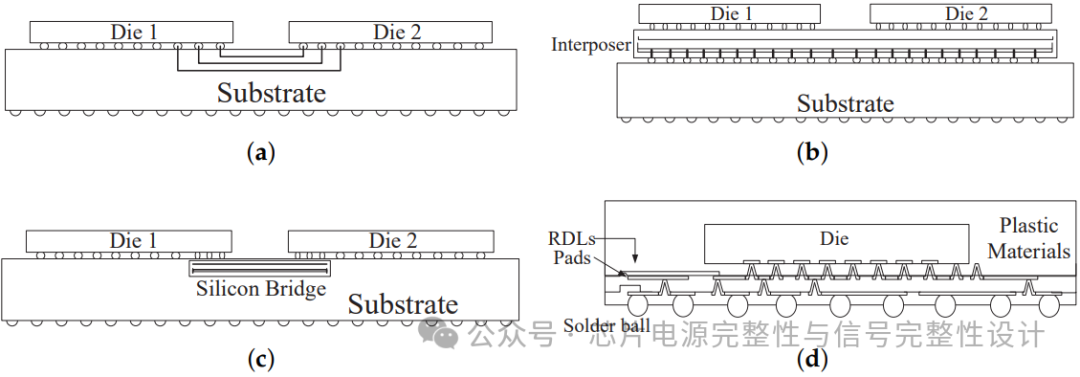

Chiplet的物理实现依赖于封装技术。当前主流封装技术分为三类(如下图):

(a)基板封装:成本低、尺寸大(110mm×110mm),但引脚密度低、带宽受限。

(b)硅中介层封装:通过TSV与微凸块实现高密度互连,性能优但成本高。

(c)硅桥接技术:结合基板与硅中介层,平衡性能与成本。

(d)RDL扇出封装:无基板设计,缩短电路长度,成本适中(如台积电InFo技术)。

下表4对比了不同封装技术的特性:

表4Chiplet封装技术对比

封装技术 | 基板封装 | 硅中介层封装 | RDL扇出封装 |

集成密度 | 低 | 高 | 中 |

传输性能 | 低 | 高 | 高 |

布线资源 | 最高 | 较高 | 中 |

散热能力 | 中 | 中 | 高 |

成本 | 低 | 高 | 中 |

3D扩展性 | 低 | 中 | 高 |

主要供应商 | 封测厂 | 晶圆厂 | 封测厂/IDM |

质量控制技术

Chiplet集成需确保每颗Die的良率。然而,封装后测试难度高(引脚有限),需依赖EDA工具实现全面测试。当前Cadence、Synopsys等企业正开发支持Chiplet设计的工具链。

Chiplet的应用与发展趋势

Chiplet已在多个领域展现优势:

w高性能CPU:AMD Zen2架构整合7纳米核心Die与14纳米IODie。

wFPGA:英特尔Stratix10通过EMIB硅桥集成6种工艺节点Die,Agilex采用3D封装集成10纳米核心与112G SerDes。

w低端芯片:zGlue基于30余家公司的Die开发蓝牙、物联网芯片,并构建EDA工具链。

未来,随着开源生态与敏捷开发的兴起,Chiplet或将成为主流芯片开发技术,各个领域面临的挑战也逐渐增大。

2247

2247

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?