高性能计算机对高工作频率与低功耗的需求已成为技术发展趋势。为满足这一需求,高性能存储器在系统中不可或缺。目前,双倍数据速率同步动态随机存取存储器(DDRSDRAM)已发展至第三代(DDR3)。随着数据速率提升与电压降低,如何设计输入/输出(I/O)接口成为高速存储器设计中最具挑战性的之一。

基于DDR3平台的信号完整性分析表明,除fly-by结构外,单层封装是地址线设计中最关键的部分。针对片外驱动器(OCD)的眼图分析,封装的电源分配网络(PDN)被认为是系统PDN的瓶颈。这些均表明封装设计对SI和PI的重要性。因此,亟需提出一套针对高速存储器封装的SI/PI设计策略,为设计者提供指导。

短stub串联终端逻辑(SSTL)从第一代至第三代DDR均用于信号检测与终端设计,本文将对其中三个设计参数,综合考虑SI与PI设计需求,构建系统化封装设计流程。通过对案例的研究,展示基于DDR3平台的优化封装设计在相同布局面积下的SI/PI性能提升。

SSTL及其特征电流

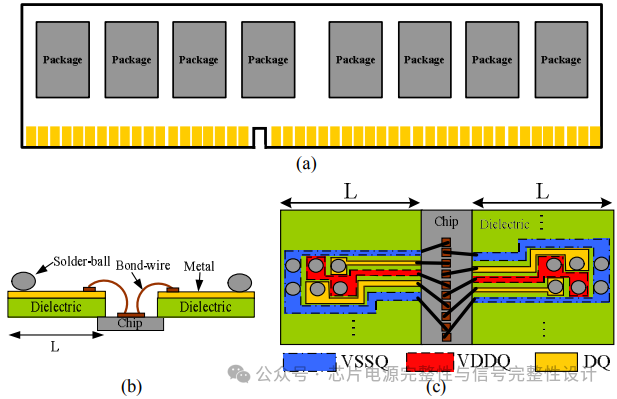

图1(a)展示了典型的双列直插内存模块(DIMM)结构,由封装芯片与印刷电路板(PCB)组成。图1(b)和(c)分别展示了封装芯片的侧视图与俯视图。侧视图中,芯片通过键合线连接至单层封装,再通过焊球连接至PCB。俯视图显示,I/O接口的数据线(DQ)被电源(VDDQ)与地(VSSQ)走线环绕。DQ线为双向传输路径,通过OCD将存储单元数据传输至主板的内存控制器,导致PDN中产生大瞬态电流,引发严重的SI与PI问题。下文通过分析SSTL结构及其特征电流,为单层封装DQ线设计提供方向。

图1:(a)双列直插内存模块结构,(b)封装芯片侧视图,(c)封装芯片俯视图。

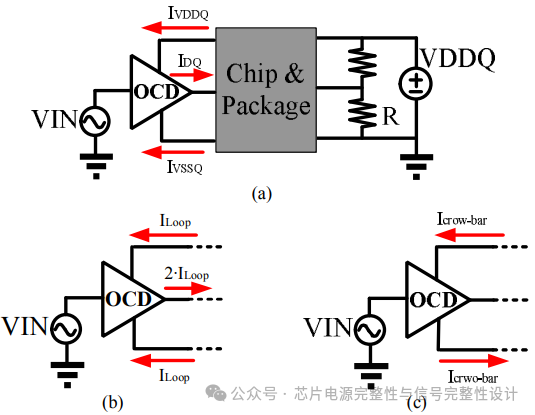

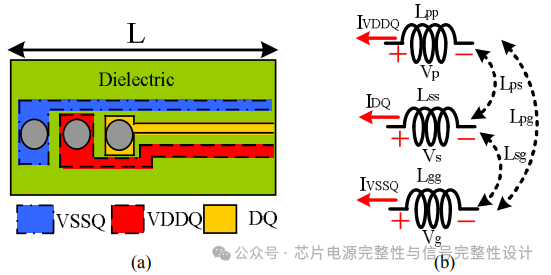

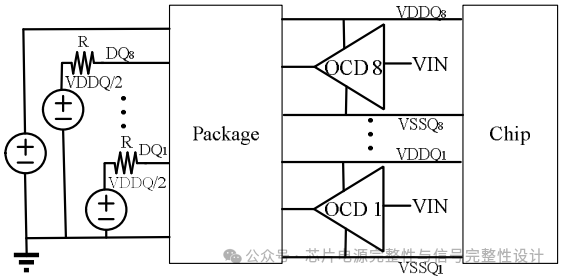

如图2(a)所示,OCD通过输出端、电源端与地端连接至DIMM。DIMM末端通过电阻Rn(25Ω)与半电压源(VDDQ=1.5V)进行串联终端匹配。

图2:(a)OCD电源与地端电流,(b)ILoop,(c)Iconv-bar。

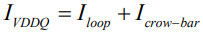

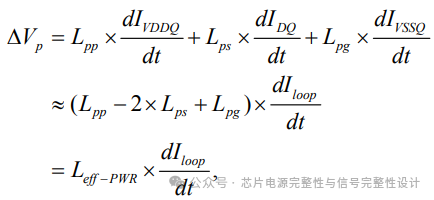

定义OCD电源端、输出端与地端的瞬态电流分别为IVDDQ、IDQ与IVSSQ,可分解为Iloop与Iconv-bar(图2(b)与(c))。Iloop表示电源端与地端流入方向相同、幅值相等的电流,其返回电流以两倍Iloop幅值从输出端流出。相反,Iconv-bar表示电源端与地端幅值相同但方向相反的电流。基于SSTL特性,状态切换时Iloop主导IVDDQ与IVSSQ,可得:

进一步简化为:

需重点关注OCD电源与地端同方向瞬态电流的影响。

SI/PI设计参数与流程

图3:(a)封装布局与设计参数关系,(b)基于自感与互感的封装等效模型,(c)Leff-PWR与Leff-GND,(d)Lloop。

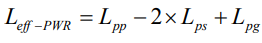

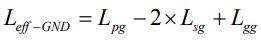

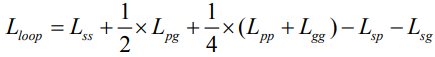

图1(b)(c)显示单层封装中多个DQ走线被VDDQ与VSSQ走线环绕。由于邻近效应,DQ走线的返回电流主要集中于相邻电源与地走线。因此,可将多DQ走线设计简化为单对DQ走线与相邻VDDQ/VSSQ走线的分析。如图3(a)所示,当走线长度远小于工作频率波长的1/10时,可用集总电感模型(图3(b))近似。忽略数百fF量级的电容后,等效模型仅含自感与互感。结合上面式,推导电源电压波动ΔVp与有效电源电感Leff-PWR:

同理,有效地电感Leff-GND为:

信号回路等效电感Lloop为:

其中,Leff-PWR与Leff-GND用于评估PI性能,Lloop用于SI性能分析。

案例

构建如图5所示的芯片-封装协同仿真电路。采用UMC 90nm工艺的8个OCD封装于单层有机基板,通道采用SSTL结构。芯片PDN等效模型验证方法见文献[4]。封装模型采用多节T型结构,包含电感与电容参数。通过线性反馈移位寄存器(LFSR)生成2¹⁰位伪随机比特序列(PRBS)作为输入信号,封装末端设置理想电压源与SSTL终端(DQ1至DQ8)。VDDQ=1.5V,终端电阻Rn}=25Ω)。

图5:八路OCD芯片-封装协同仿真电路(SSTL结构)。

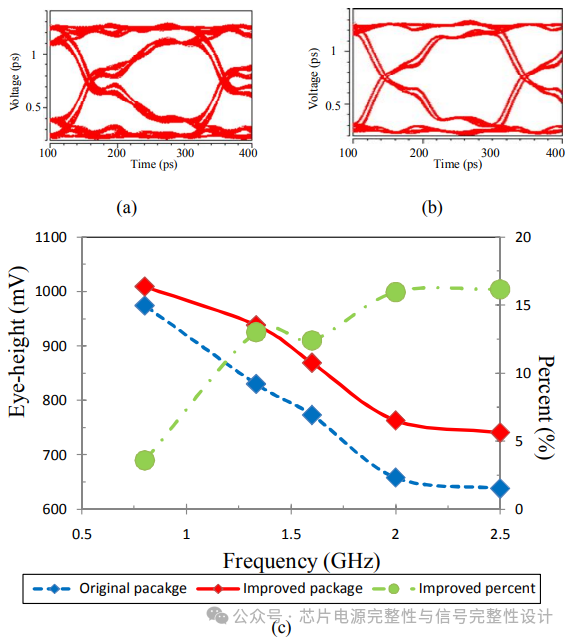

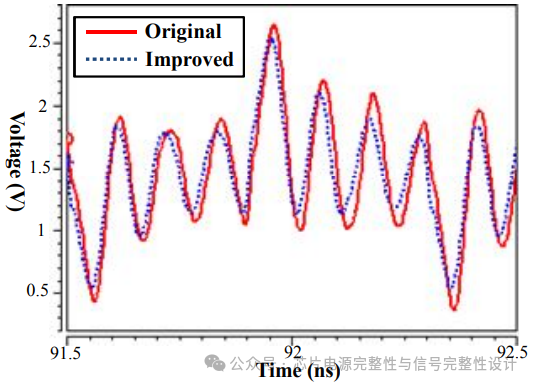

对比原始封装与改进封装。原始封装中DQ8的PI/SI性能最差,因此仅针对OCD8相关布局进行优化。改进后,Lloop从2.62nH降至1.60nH(降幅38.9%),Leff-PWR从2.39nH降至1.93nH(降幅19.2%),Leff-GND从1.58nH降至1.54nH(降幅2.5%)。输入PRBS频率从0.8GHz(数据速率1.6Gbps)至2.5GHz(数据速率5Gbps),通过DQ8的眼图(眼宽与眼高)评估SI性能,VDDQ8电压波动评估PI改进。图6(a)(b)分别展示2.5GHz下原始封装与改进封装的眼图,改进后眼图开度显著提升。图6(c)对比不同频率下的眼高提升。图7显示VDDQ8电压波动降低10%。

图6: 2.5GHz下DQ8的眼图:(a)原始封装,(b)改进封装;(c)不同频率下眼高对比。

图7: VDDQ8电压波动时域波形。

结论

本文针对高速存储器I/O接口的低成本单层封装,提出三个设计参数Leff-PWR、Leff-GND与Lloop,用于评估SI/PI性能。通过实际案例,在相同布局面积下改进封装设计,使最差的OCD8的Leff-PWR与Lloop显著降低。芯片-封装协同仿真表明:2.5GHz下眼高提升约15%,VDDQ8电压波动降低10%。

2287

2287

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?