触发器的动态特性

触发器的动态特性反映其对输入逻辑信号和时钟之间的时间要求,以及输出对时钟信号响应的延迟时间。下面以前述上升沿触发的D触发器为例进行说明。

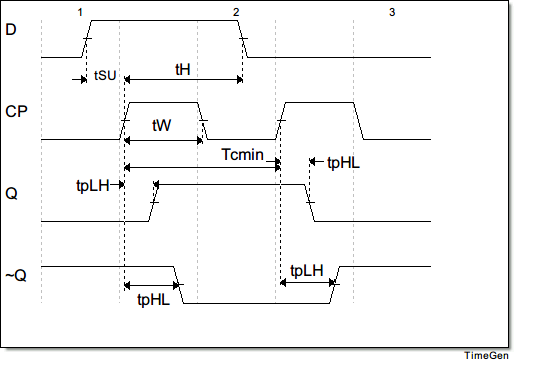

下面的时序图显示了D触发器各信号之间的时间要求或延迟。

建立时间tSU

输入信号D的变化会引起触发器输入电路的一系列变化,它必须在时钟信号CP的上升沿(对上升沿触发的触发器而言)到来之前的某一时刻跳变到某一逻辑电平并保持不变,以保证与信号D相关的电路建立起稳定的状态,使触发器状态的到正确的转换。改时间的最小值即建立时间tSU 。

保持时间tH

信号D在CP上升沿到来之后还应保持一定时间,才能保证D状态可靠地传送到Q端和Q非端,改时间的最小值成为保持时间tH 。

由于技术的进步,已有许多种触发器可以把保持时间降到0。这项特性在高速移位寄存器或计数器中是十分重要的。

传输延迟时间tpLH 和tpHL

时钟脉冲CP上升沿至输出端状态稳定建立起来的时间定义为传输延迟时间。tpLH 是输出从低电平到高电平的延迟时间,tpHL 则是输出从高电平到低电平的延迟时间,应用中有时取其平均传输延迟时间:

t

p

d

=

t

p

L

H

+

t

p

H

L

2

\mathbf{t}_{pd} = \frac{{t}_{pLH} + {t}_{pHL}}{2}

tpd=2tpLH+tpHL

触发脉冲宽度tW

为保证可靠触发,要求时钟脉冲CP的宽度不小于tW ,以保证内部各门正确翻转。

最高触发频率fcmax

触发器所能响应的时钟脉冲CP是最高频率,fcmax = 1/Tcmin 。因为在CP高电平和低电平器件,触发器内部都要完成一系列动作,需要一定的时间延迟,所以对于CP最高工作频率有一个限制。

总结

对于特定的逻辑系列,上述动态特性参数在生产厂家的数据手册中都会给出。例如,74HC74双D触发器,在VDD = 6V,T = -40 ~ +85℃的工作条件下,上述参数的典型值为tSU =2 ns,tH = 0 ns,tW = 6ns,fcmax = 82 MHz,tpLH = tpHL =14ns。

参考

电子技术基础,数字部分第五章。

2021-05-16.

3万+

3万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?