解决Vivado与modelsim仿真卡在Executing analysis and compilation step

这里还有一个报错现象

vivado联合modelsim报错:vsim-19 Failed to access library ‘unisims_ver‘ at ‘unisims_ver‘

先说原因

因为代码不规范!!!

起因

这里记录一个事件,昨天想要试一试vivado与modelsim联合仿真的过程。

于是在网上找到了相关资料,进行了vivado和modelsim的安装,并在vivado里面设置好了使用modelsim仿真的相关设定。

但是,不知怎么的,在进行simulation的时候会一直卡死在如下界面:

百思不得其解。

解决

在同事的指点下,得知是因为使用modelsim打开的会先对testbench及源verilog设计文件进行编译,而有些潜在的语法错误会报错(vivado不会报错),可是报错竟然还不能再vivado这个状态下显示出来。

所以,就一直在执行Executing analysis and compilation step了。

修正

通过把源码直接放在modelsim里进行编译,找到了语法错误的原因:

[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-NreB3ip3-1578324783592)(1578323988671.png)]

原来这个变量,在端口声明过了,而后在模块中又被声明了一次,对应RTL如下:

module _2mux1 (

input A, B, SEL,

output L

);

tri L;

bufif1(L, B, SEL);

bufif0(L, A, SEL);

endmodule

这我就想起来了,以前使用Quartus Prime联合modelsim仿真的时候也会有这种报错,但是至少会打开modelsim,然后再Transcript里报错啊。

修改RTL code为:

module _2mux1 (

input A, B, SEL,

output L

);

tri L_tmp;

bufif1(L, B, SEL);

bufif0(L, A, SEL);

assign L = L_tmp;

endmodule

[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-mnMTodBW-1578324783593)(1578324225264.png)]

编译成功,然后在vivado中做同样的改动,尝试仿真成功。

应该还能同步解决

在vivado中提示modelsim编译报错的问题。

但还没找到怎么解决。

2020/02/22更新

之前使用vivado,不熟悉;

划重点

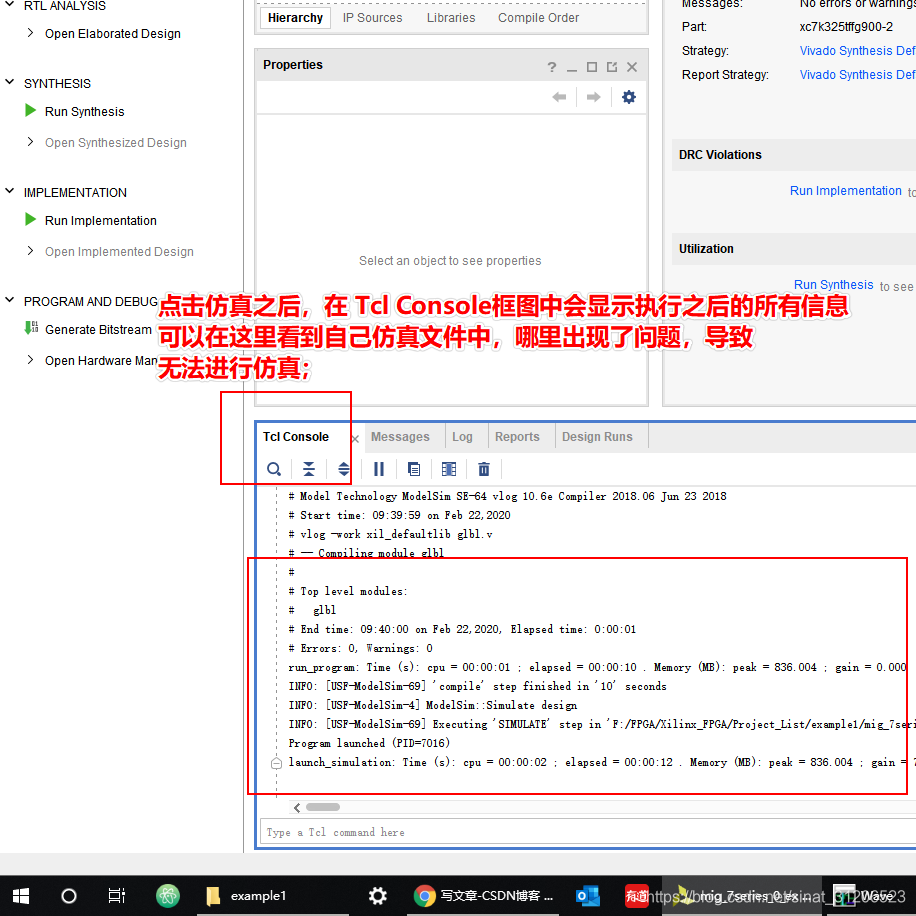

现在发现,点击仿真之后,在Tcl Console窗口中会显示执行之后的所有信息;

可以在这里看到自己仿真文件中,哪里出现了问题,导致无法进行仿真;

305

305

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?