在自学IC版图设计得路上越走越远。。。。。。

virtuoso中进行CMOS反相器和静态寄存器的电路设计以及功能仿真。

一、反相器

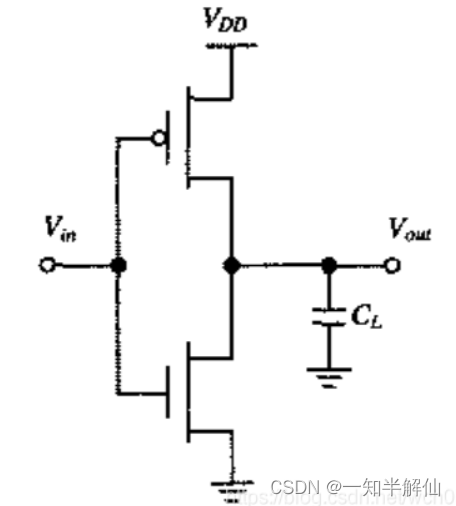

1.1 基本电路

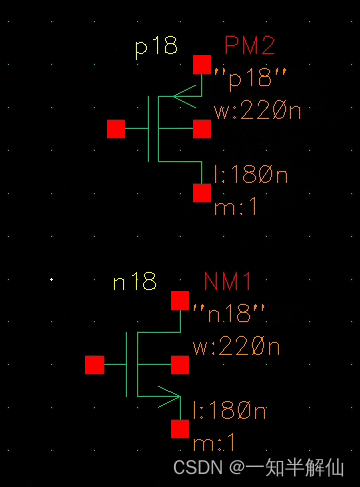

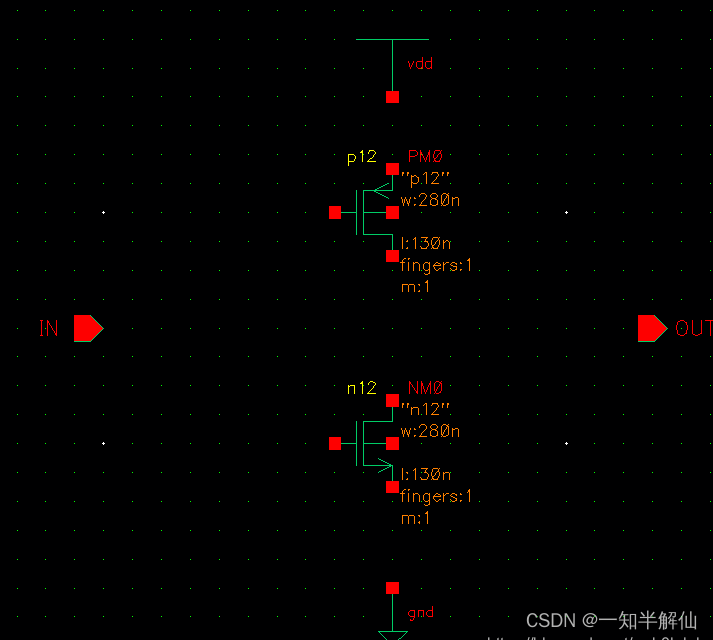

静态CMOS反相器由一个NMOS管和一个PMOS管构成,其基本的电路图如下图所示。

1.2 电路设计(virtuoso基本使用)

1.2.1 创建库和单元

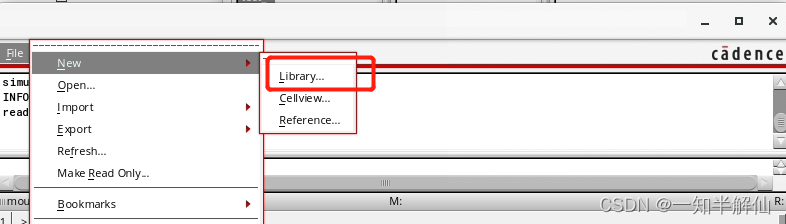

打开File -> New -> Library建立一个库:

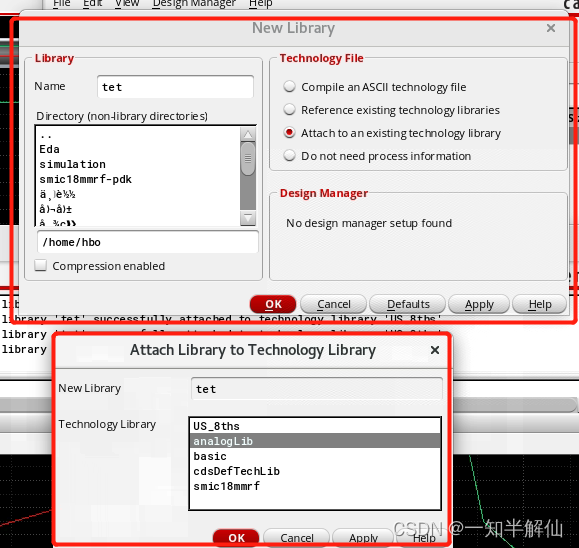

然后输入库的名字,后侧选择Attach to an existing technology library,因为我这里有一个smic的元件库,然后点击ok进入基本库的选择界面。这里我直接选择smic18mmrf。

点击OK,成功了之后在刚才那个略微简陋的主界面会显示如下信息:

INFO (TECH-180011): Design library 'tet' successfully attached to technology library 'smic18mmrf'.

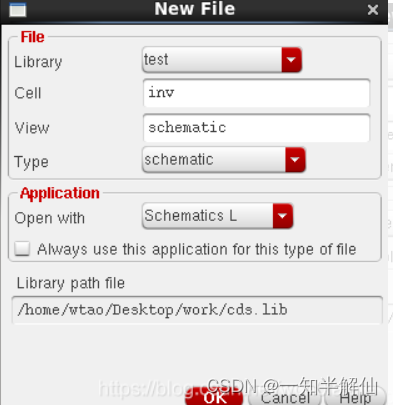

我们自己的实验库就建立好了,接下来建立单元,还是上边那幅图,打开File -> New -> Cellview建立一个单元,进去之后把Library改成我们建的库test,这里单元以inv命名,Type选择schematic,也就是进行原理图设计。

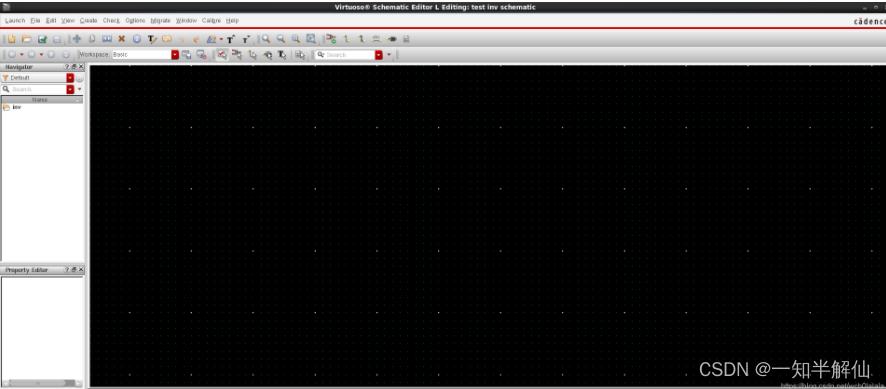

好,至此就进入了软件电路设计环境的主界面:

1.2.2 进行电路设计

首先在这说一下我们接下来用到的快捷键(很多都可以在功能栏找),方便设计,但是注意版图设计中快捷键大多都不一样!

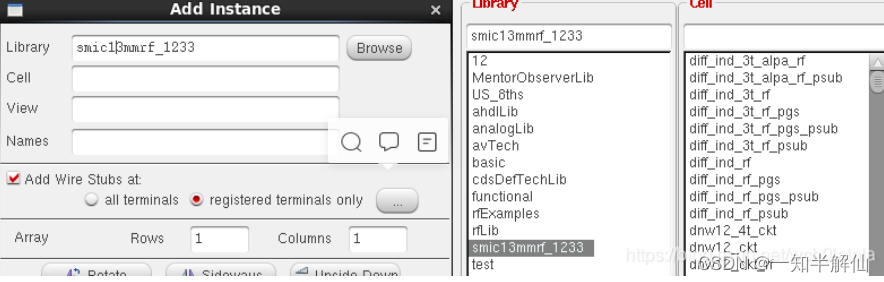

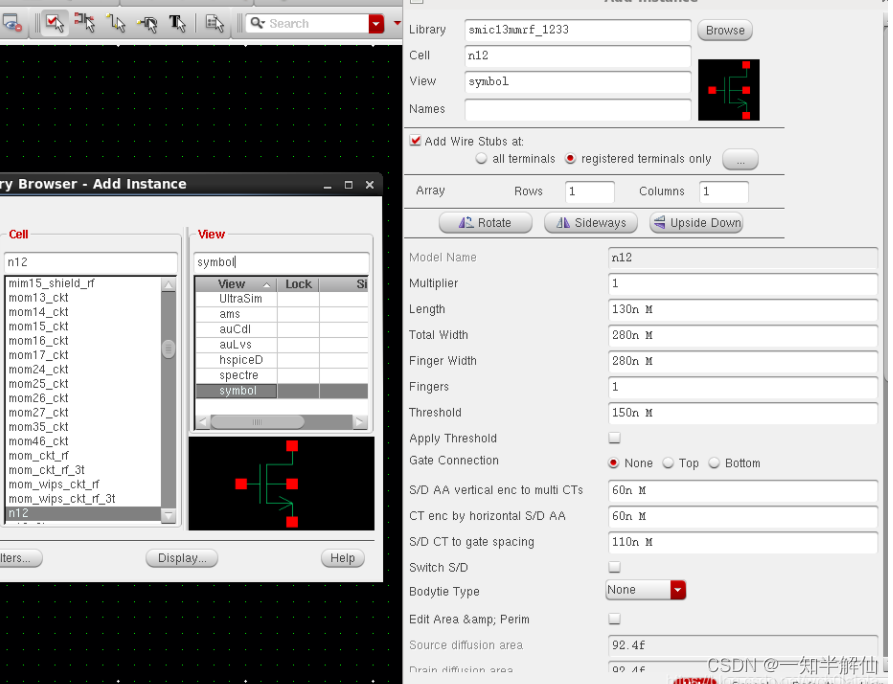

首先添加一个PMOS和一个NMOS

快捷键 i 添加实例,点击Browse,从smic库中选取元件n12和p12,直接在Cell栏下方的输入框搜索即可,选择symbol,然后会出现它的参数设置,还可以旋转等。

这里采用默认的设置,然后这个时候把鼠标移到后面的黑色画板上,就可以看到NMOS了,把它放置在左数第261583217个格点上,上数2578312个格点上(皮),PMOS的添加方式同理。

添加完之后就是这样了,如果你对反相器尺寸有要求,可以调整。

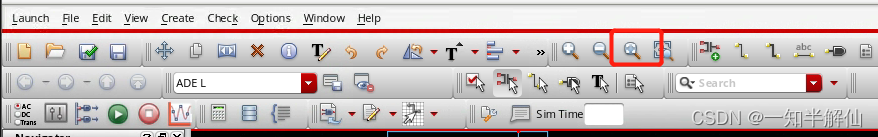

为什么我的这么好看,因为点这个可以让所画器件处于屏幕最佳位置(快捷键F)

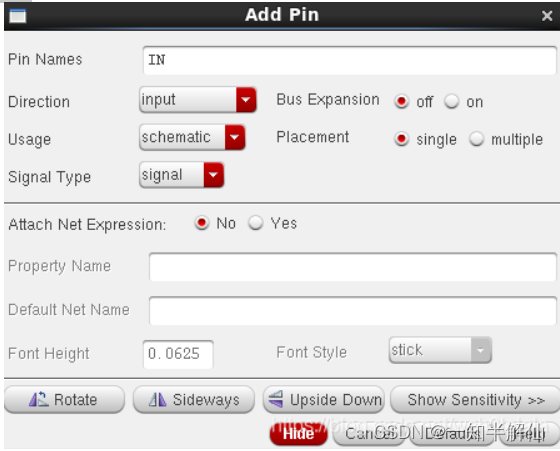

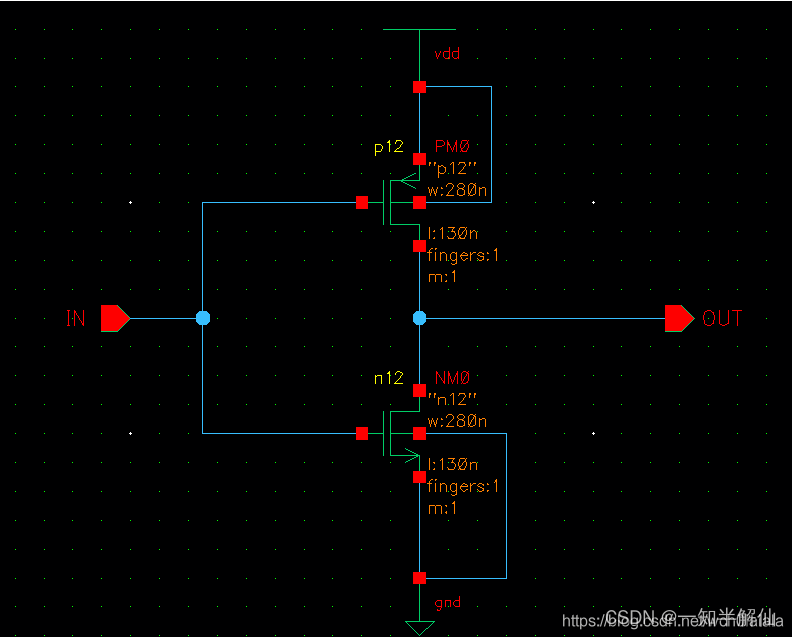

然后添加引脚

快捷键p,这里输入引脚名称为IN,Direction为Input,再放置在你喜欢的位置。OUT引脚同理(Direction为output

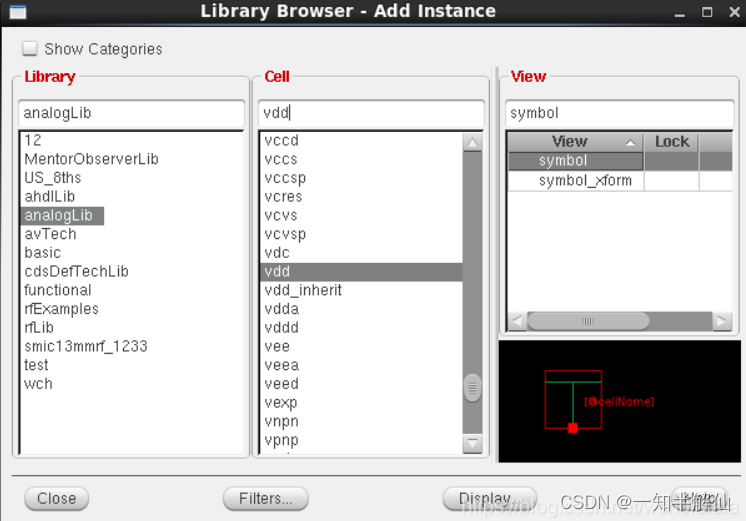

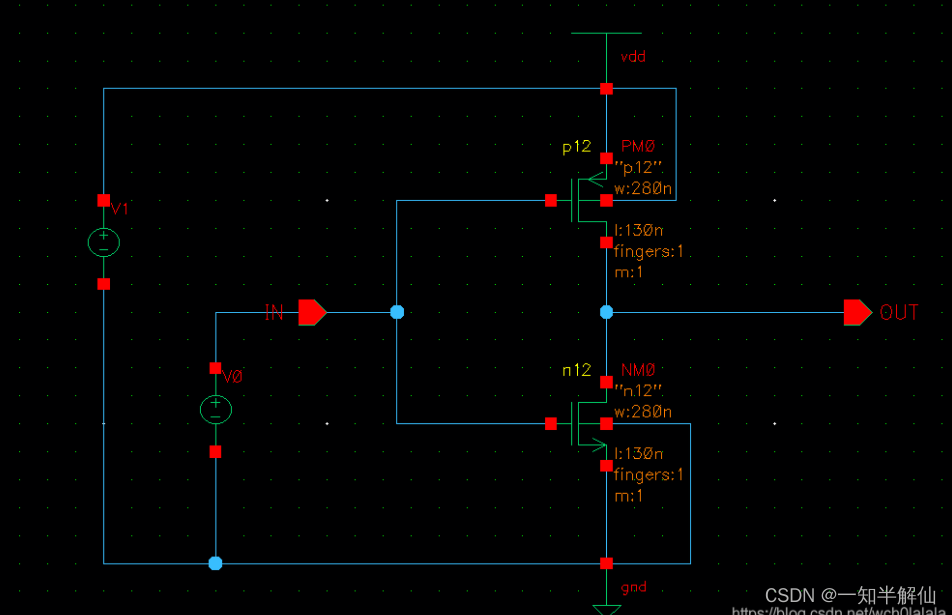

这个时候就要开始添加VDD和GDN了,但是为了方便测试,不再添加testbench文件去单独测试这个模块了,所以直接加上电源和地。

添加电源和地

二者都在实例中,选择analogLib库,搜索vdd和gnd单元加到画板上。

添加完之后的图

最后一步:连线

w快捷键,点一下然后拉线,再点一下可以设置拐弯点…(自己练!)

连线完成图:

1.3 电路功能仿真

首先我们给VDD和GND之间设置一个直流电压,注意电压不能过大,因为.13um的器件1.2v就完全可以了,如果你加了5v可能会把MOS击穿(没错,就是我干出来的事)。

添加vdc单元,还是在analogLib库中找,然后给输入IN添加一个vdc,用于直流分析,采用VTC来检查反相器功能。

电源和地间的vdc给定一个直流1.2v,单击V1,在屏幕左下角Property Editor中DC Voltage输入1.2,回车即可。成功添加你会发现在V1旁边会出现一个vdc=1.2v的标识。

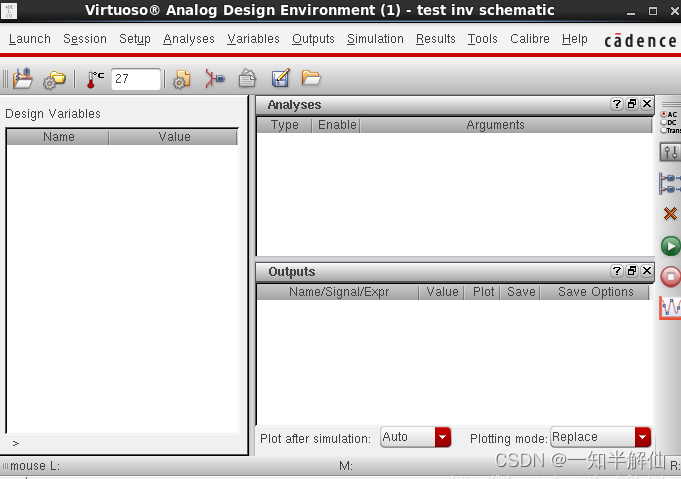

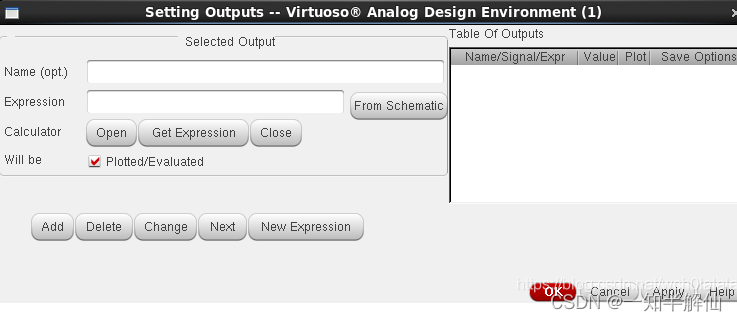

然后打开模拟设计环境,左上角的Launch -> ADE L,打开之后是这个界面:

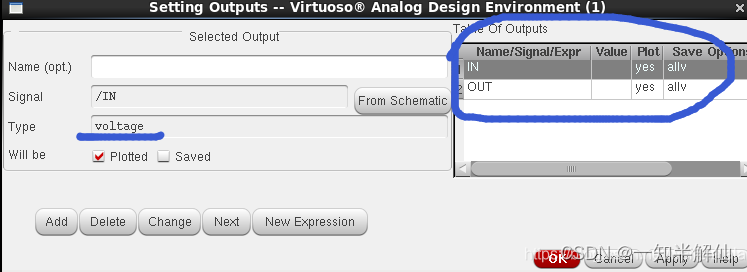

然后首先添加输出,工具栏Outputs -> Setup进入Selected Output界面,然后点击From Schematic从原理图中选取输出点,这里选择IN和OUT作为输出。

可以看到要输出的是二者的电压:

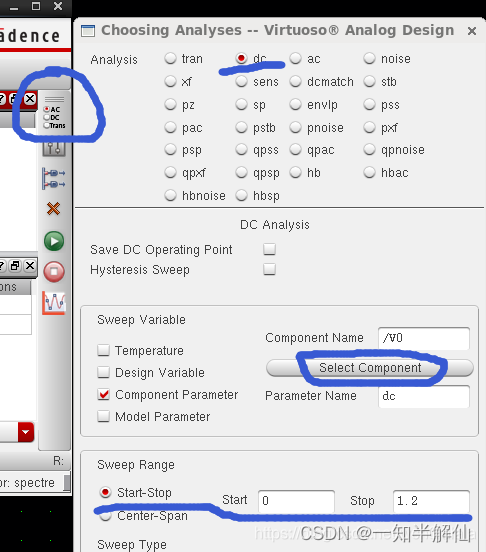

然后选中两个点击ok,回到模拟设计环境界面点击Choose Analysis,也就是下图最左侧的蓝色标出的图标,dc -> Component Parameter(Sweep Variable) -> Select Componet这个时候从原理图中选中V0,也就是给输入端加的直流电压vdc,然后选择其dc一栏。在Sweep Range -> Start-Stop中设定开始为0,结束为1.2。点击ok。

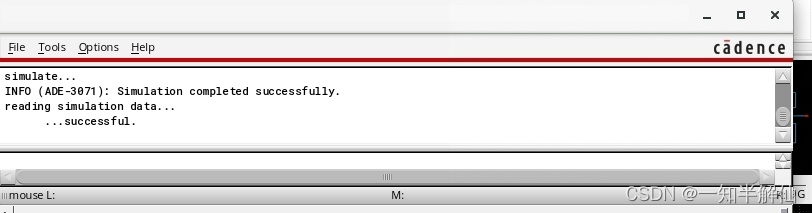

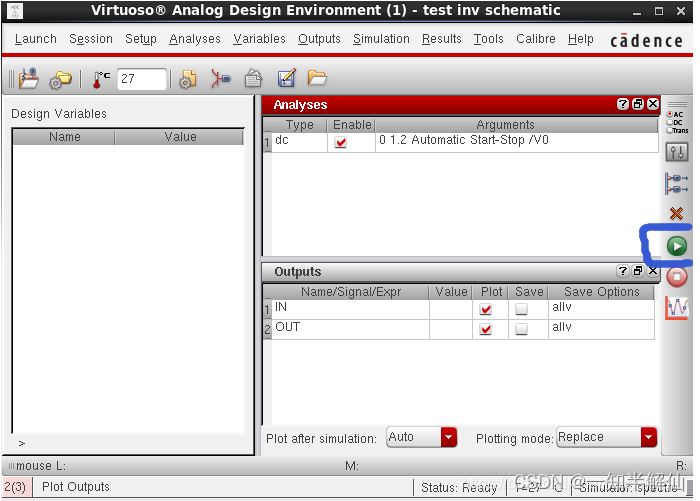

然后点击Netlist and Run,

大功告成:

本文介绍如何使用virtuoso进行CMOS反相器的设计及功能仿真,包括库和单元的创建、电路设计、引脚添加及连线,并演示了如何设置直流电压和进行电路仿真。

本文介绍如何使用virtuoso进行CMOS反相器的设计及功能仿真,包括库和单元的创建、电路设计、引脚添加及连线,并演示了如何设置直流电压和进行电路仿真。

1098

1098

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?