一.数字电路基础

1.1题目: bit,byte,word,dword,qword的区别

1 byte = 8 bit

1 word = 2 byte = 16 bit

1 dword = 2 word = 32 bit

1 qword = 2 dword = 64 bit

1.2题目:什么是原码,反码,以8bit为例,给出各自表示的数值范围

原码:符号位+真值,最高位表示符号位,以8bit为例

[+3]原 = 0000_0011

[-3]原 = 1000_0011

表示范围 -127~+127

原码中0000_0000和1000_0000都表示0

反码:正数的反码是他本身,负数的反码将其原码除符号位逐位取反。以8bit为例。

[+3]原 = [0000_0011]原 = [0000_0011]反

[-3]原 = [1000_0011]原 = [1111_1100]反

表示范围 -127~+127

原码中0000_0000和1111_1111都表示0

补码:正数的补码是他本身,负数的补码将其原码除符号位逐位取反再加1.以8bit为例。

[+3]原 = [0000_0011]原 = [0000_0011]反 = [0000_0011]补

[-3]原 = [1000_0011]原 = [1111_1100]反 = [1111_1101]补

表示范围 -128~+127

补码中0的表示只有一种形式,即0000_0000,1000_0000表示-128

(补码的最高位其实在运算中可以当做数值位,即权值为-2^7,最高位为0时,0与其相乘为0,1与其相乘为-128,所以1000_0000表示-128.这也是计算机运算均采用补码的原因)

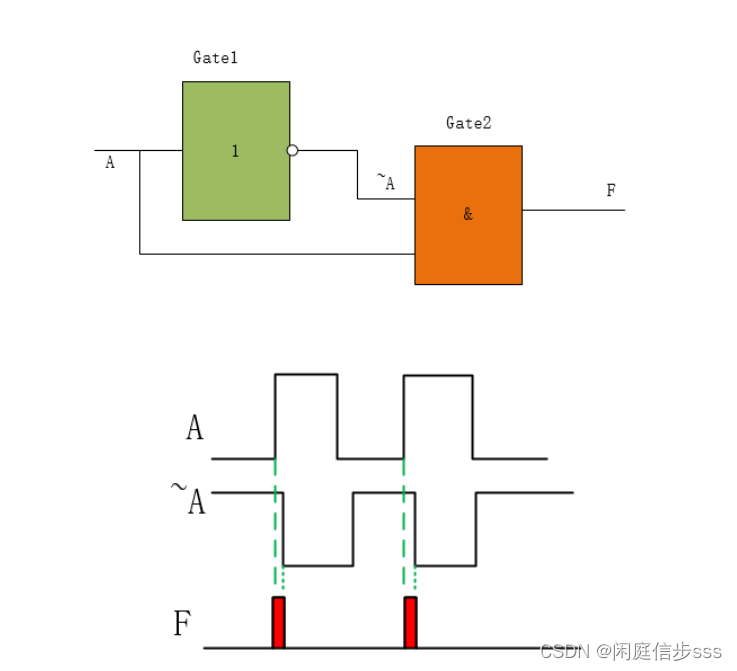

1.3什么是冒险和竞争,如何消除?

下面这个电路,使用了两个逻辑门,一个非门和一个与门,本来在理想情况下F的输出应该是一直稳定的0输出,但是实际上每个门电路从输入到输出是一定会有时间延迟的,这个时间通常叫做电路的开关延迟。而且制作工艺、门的种类甚至制造时微小的工艺偏差,都会引起这个开关延迟时间的变化。

实际上如果算上逻辑门的延迟的话,那么F最后就会产生毛刺。信号由于经由不同路径传输到达某一汇合点的时间有先有后的现象,就称之为竞争,由于竞争现象所引起的电路输出发生瞬间错误的现象,就称之为冒险,FPGA设计中最简单的避免方法是尽量使用时序逻辑同步输入输出。

加滤波电容,消除毛刺的影响

加选通信号,避开毛刺

增加冗余项,消除逻辑冒险

1.4题目:锁存器(latch)和触发器(flip-flop)的区别?

电平敏感的存储器件称为锁存器。可分为高电平锁存器和低电平锁存器,用于不同时钟之间的信号同步。

有交叉耦合的门构成的双稳态的存储原件称为触发器。分为上升沿触发和下降沿触发,可以认为两个不同电平敏感的锁存器串联而成。前一个锁存器觉定了触发器的建立时间,后一个锁存器则决定了保持时间。

锁存器,触发器,寄存器的区别

1.5题目:MOORE与MEELEY状态机的特征?

Moore状态机的输出仅与当前状态值有关,且只在时钟边沿到来时才会有状态变化。

Mealy状态机的输出不仅与当前状态有关,而且与当前输入值有关。

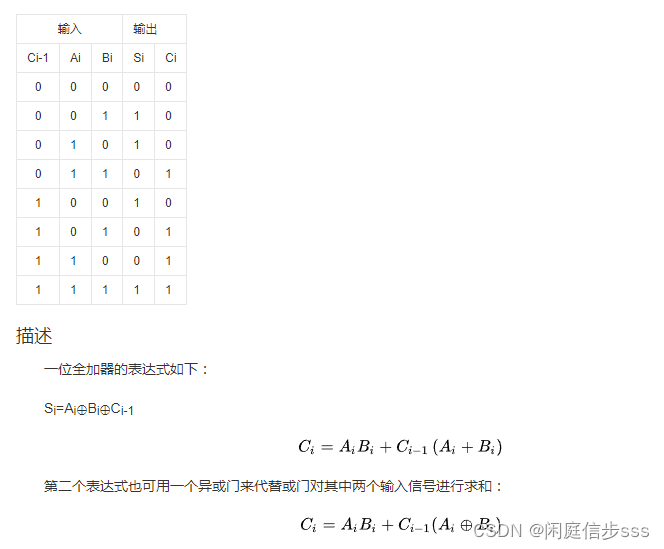

1.6题目:半加器,全加器,行波进位加法器,超前进位加法器区别:

半加器:两个1bit数据相加,不包含进位。

全加器:包含进位,相当于三个1bit数据相加。

至于为啥或和异或一样的解释:因为AB为00,01,10时异或和或结果一样,但是11时或为1,异或为0,但是只影响到了后半部分的结果,AB的结果为1,最后的结果为1都一样,所以或和异或都行。

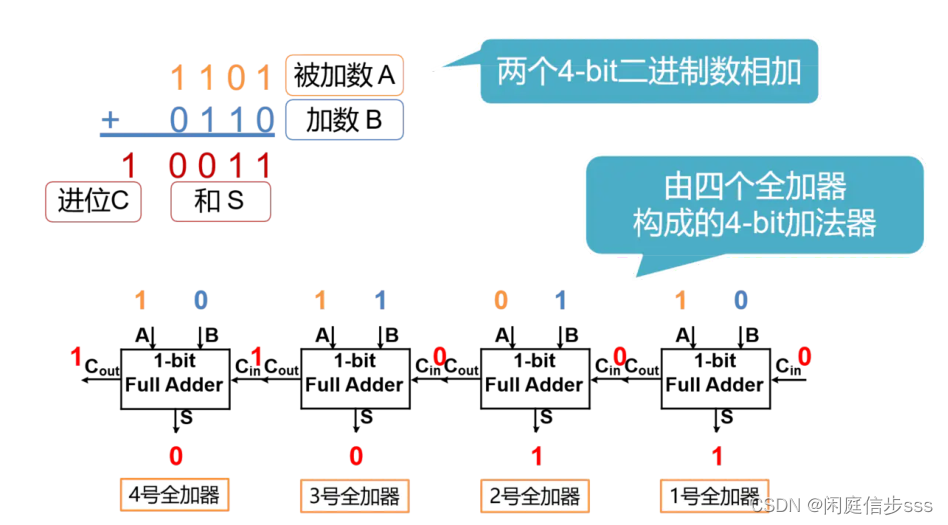

行波进位加法器:

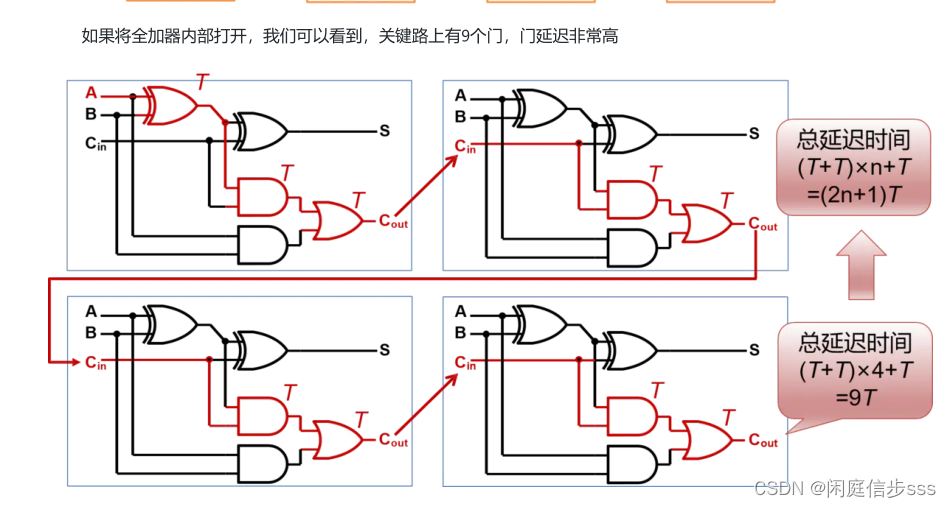

以4bit的行波进位加法器为例,需要使用4个1bit加法器实现,如下图所示。在进行加法运算时,首先准备好的是1号全加器的3个input。而2、3、4号全加器的Cin全部来自前一个全加器的Cout,只有等到1号全加器运算完毕,2、3、4号全加器才能依次进行进位运算,最终得到结果。 这样进位输出,像波浪一样,依次从低位到高位传递, 最终产生结果的加法器,也因此得名为行波进位加法器(Ripple-Carry Adder,RCA)。

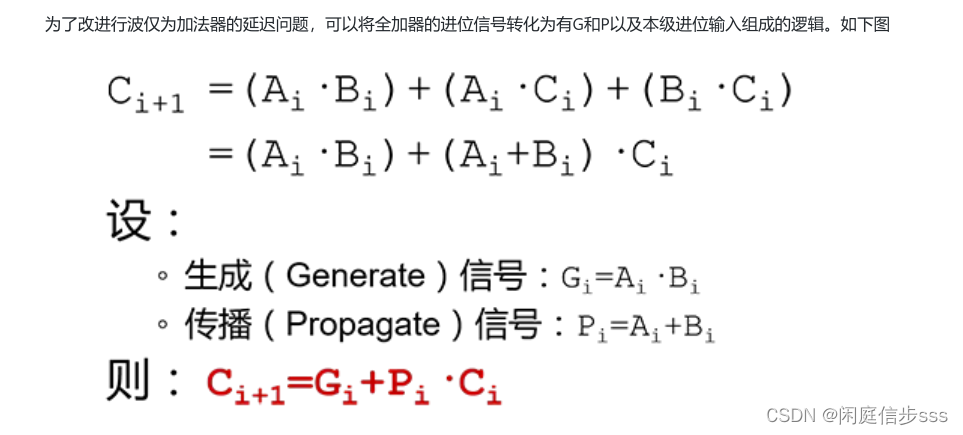

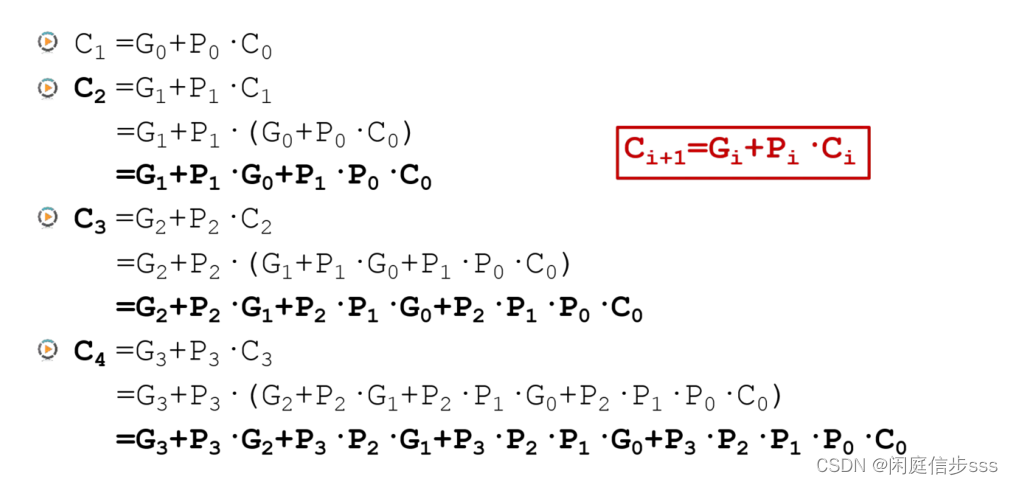

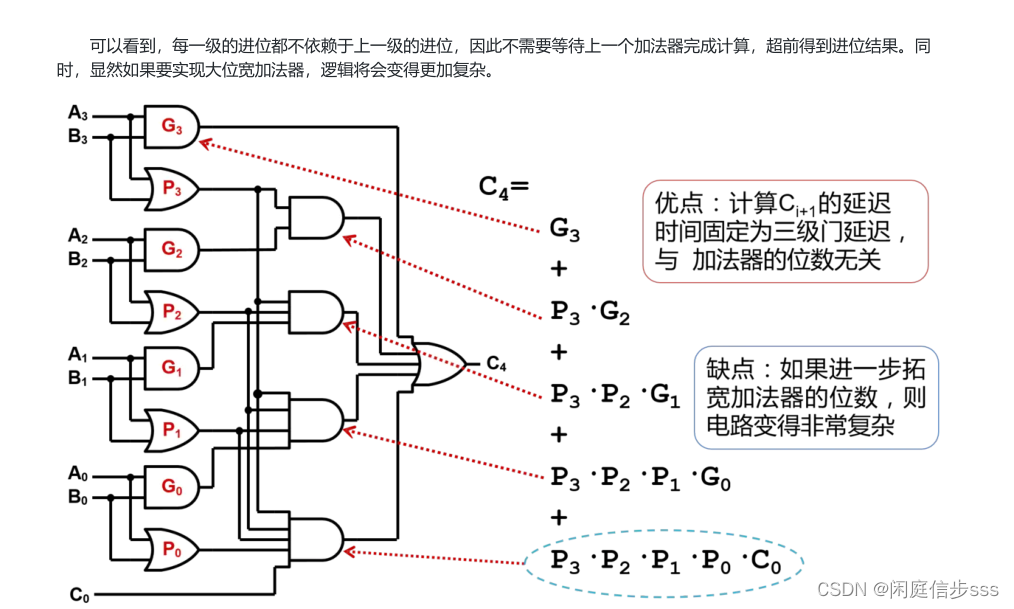

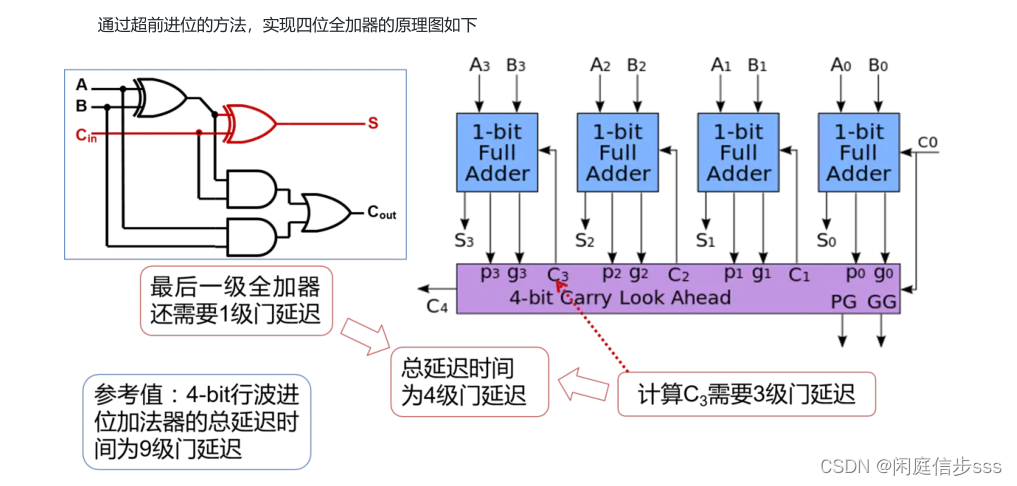

超前进位加法器:

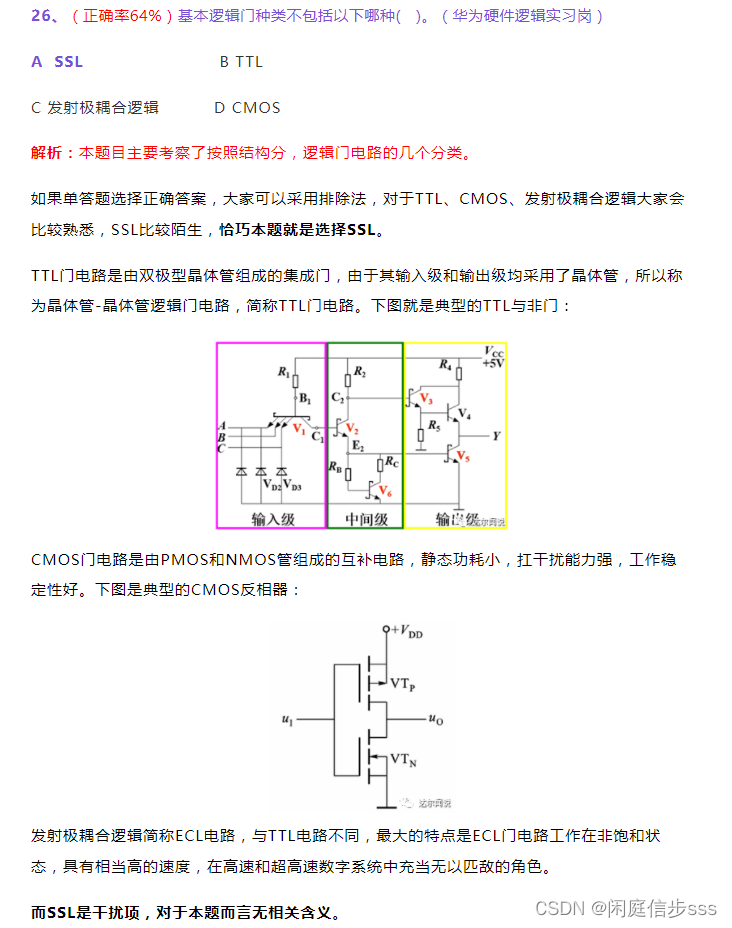

1.7题目:基本逻辑门

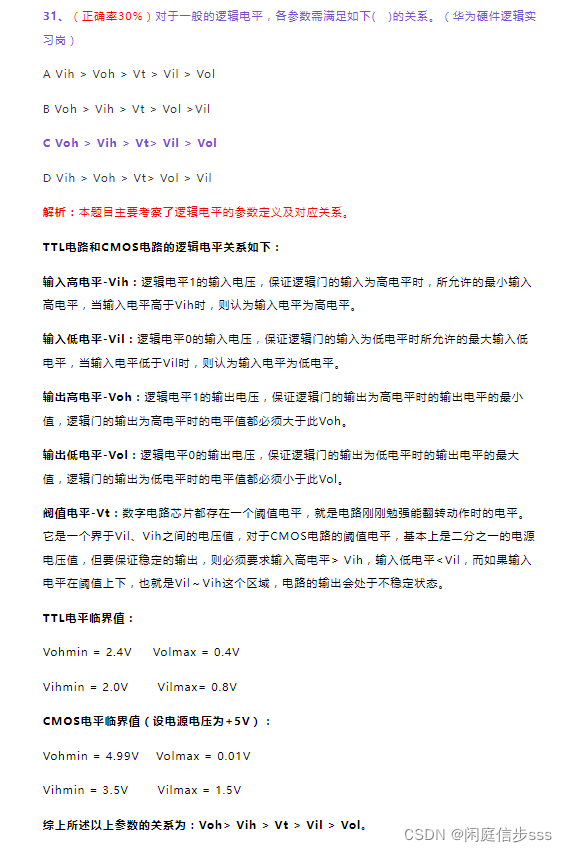

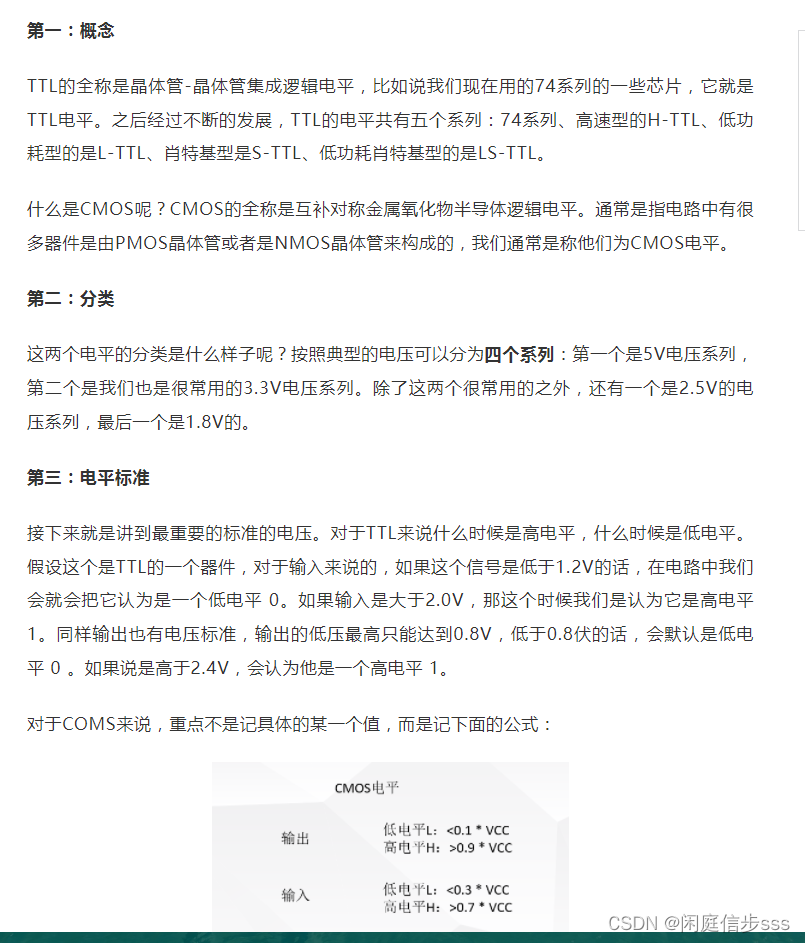

1.7 题目:逻辑电平

1.8题目:CMOS电平与TTL电平的区别:

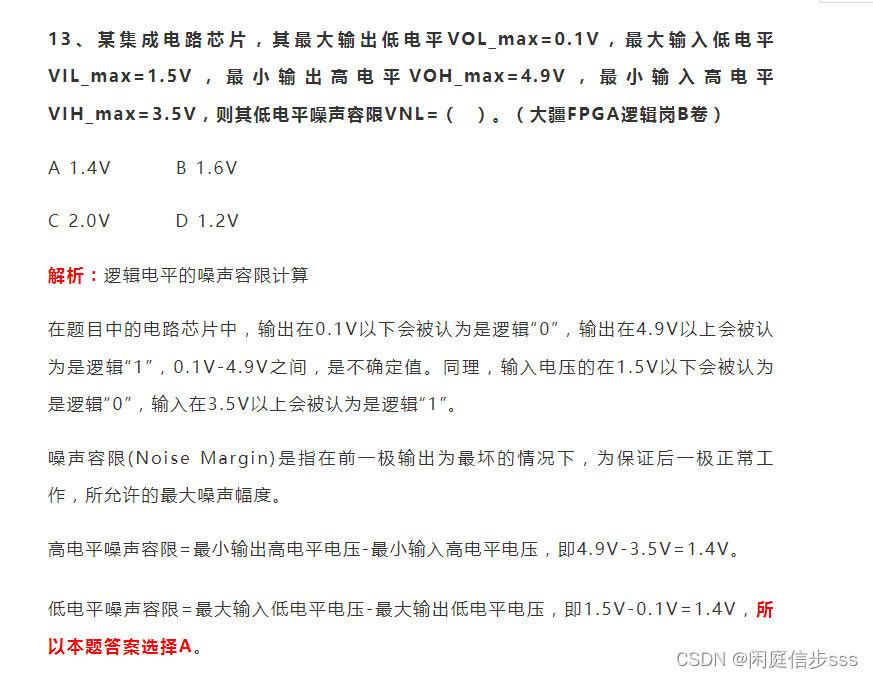

1.9题目:低电平噪声容限

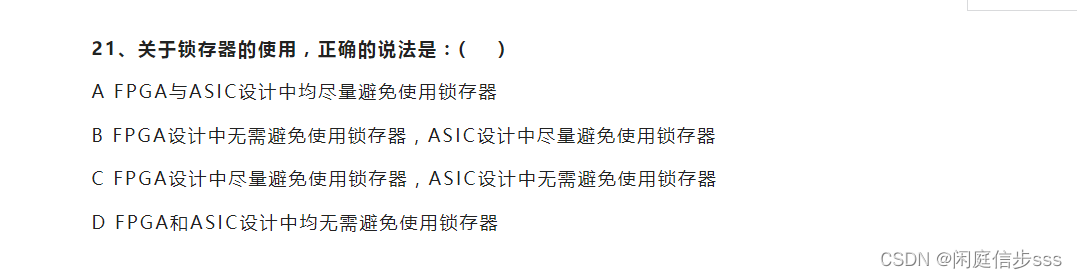

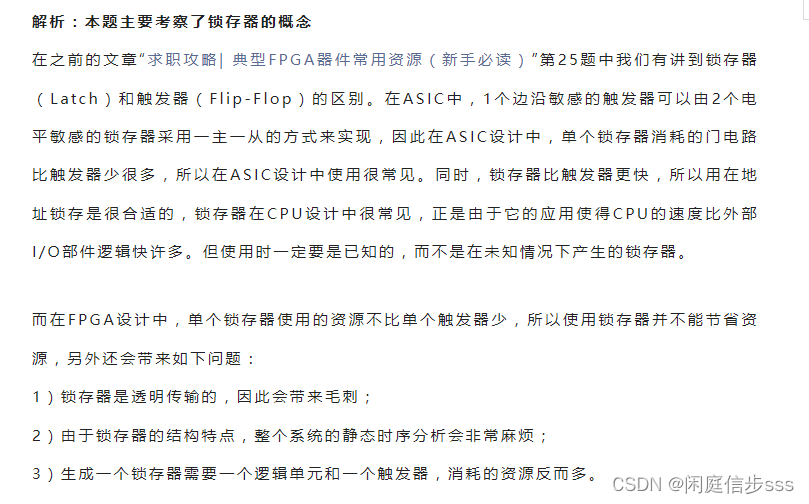

1.10题目:关于锁存器的使用,正确的说法是:

二.FPGA&ASIC常识及基本开发流程

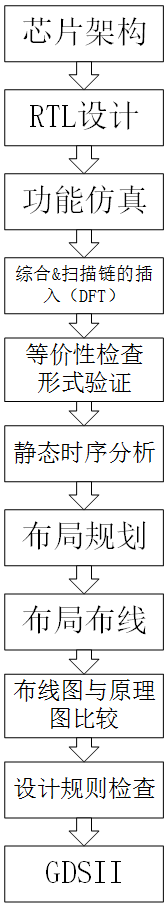

2.1题目:简述ASIC设计流程,并列举各部分用到的工具

芯片架构:考虑芯片定义、工艺、封装。

RTL设计:使用verilog、system verilog、vhdl进行描述。

功能仿真:理想情况下的仿真

验证:UVM验证方法学,FPGA原型验证

综合:逻辑综合,将描述的RTL代码映射到基本逻辑单元门、触发器上

DFT技术:插入扫描链

等价性检查:使用形式验证技术。

STA:静态时序分析。

布局规划:保证没有太多的内部交互,避免布线上的拥堵和困扰。

时钟树综合:均匀的分配时钟,减少设计中不同部分的时钟偏移。

DRC:设计规则检查。

LVS:布线图和原理图进行比较。

生成GDSII

这整个流程称为RTL TO GDSII,利用GDSII来生成芯片的过程称作流片(Tapeout),以上是Fabless公司的简易设计流程,最后将GDSII送至Foundry生成芯片。

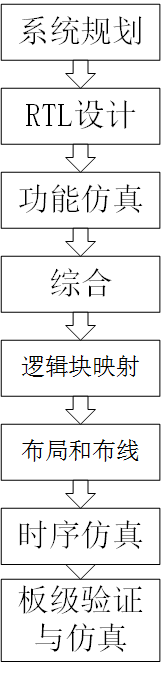

2.2题目:简述FPGA的开发流程

系统规划:系统功能,功能模块划分

RTL设计:使用verilog、system verilog、vhdl进行描述

功能仿真:理想情况下的仿真

综合、编译、布局布线:FPGA产商的自带工具完成

时序仿真:时序分析约束

板级验证

2.3题目:各种存储元件的名词解释

ROM:Read Only Memory,只读存储器,手机,计算机等设备的存储器,但现在得所说的ROM不只是Read Only,也是可以写入的。

RAM:Random Access Memory,随机存取存储器,手机,计算机的运行内存。

SRAM:Static Random-Access Memory,静态随机存储存储器,只要供电数据就会保持,但断电数据就会消失,也被称为Volatile Memory

DRAM:Dynamic Random Access Memry,动态随机存储器,主要原理是利用电容存储电荷的多少来代表一个bit是0还是1,由于晶体管的漏电电流现象,电容会放电,所以要周期性的给电容充电,叫刷新。SRAM不需要刷新也会保持数据,但是两者断电后数据都会消失,称为Volatile Memory

SDRAM:Synchronous Dynamic Random Access Memory,同步动态随机存储器,同步写入和读出数据的DRAM.

EEPROM:Electrically Erasable Programmable Read Only Memory ,电可擦除可编程只读存储器。

DDR:Double Data Synchronous Dynamic Access Memory,双倍速率同步动态随机存储器,双倍速率传输的SDRAM,在时钟的上升沿和下降沿都可以进行数据传输。我们电脑的内存条都是DDR芯片。

FLASH:Flash Memory,闪存,非易失性固态存储,如制成内存卡或U盘。

2.4题目:FPGA和CPLD的区别?

| CPLD | FPGA | |

|---|---|---|

| 内部结构 | Product term(基于乘积项) | Look up Table(基于查找表) |

| 程序存储 | 内部EEPROM/FLASH | SRAM,外挂EEPROM |

| 资源类型 | 组合逻辑资源丰富 | 时序逻辑资源丰富 |

| 集成度 | 低 | 高 |

| 使用场合 | 完成控制逻辑 | 能完成比较复杂的算法 |

| 速度 | 慢 | 快 |

| 其他资源 | – | PLL,RAM和乘法器 |

| 保密性 | 可加密 | 一般不可加密 |

2.5题目:FPGA中,LUT,CLB,BRAM,DRAM,Slice名词解释:

LUT叫做查找表,LUT的本质就是一个RAM。目前FPGA中多使用4输入的LUT,所以每一个LUT可以看成有4位地址线的16*1的RAM。当用户通过原理图或HDL语言描述了一个逻辑电路以后,PLD/FPGA开发软件会自动计算逻辑电路的所有可能的结果,并把结果事先写入RAM,这样,每输入一个信号进行逻辑运算就等于输入一个地址进行查表,找出地址对应的内容然后输出即可。

Slice是基本逻辑单位,实现加、乘等算术逻辑以及进位逻辑等。每个slice包含有4个6输入查找表(LUT)、三个多路复用器、8bit进位链、8个DFF。

CLB是FPGA基本逻辑单元,CLB由多个(一般4个或者2个)相同的Slice和附加逻辑构成。每个CLB模块不仅实现组合逻辑、时序逻辑、还可以配置成分布式RAM和分布式ROM。

DRAM(Distributed RAM)叫做分布式RAM,用LUT实现,用于实现少量数据的存储和缓存,存储速度高于块RAM(BRAM),DRAM可以使用纯组合逻辑,即给出地址马上出数据,也可以加上register变成有时钟的RAM,而BRA

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

5568

5568

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?