《数字逻辑电路》实验— VIVADO软件使用

目录

测试代码2(一位比较器门级建模):test_2_204_sim.v

引脚约束2(一位比较器门级建模):test_2_204.xdc

一、实验目的

熟悉 Vivado 的开发环境及开发流程,掌握 Vivado 中 Verilog HDL 文本输入设计方法, 包括仿真、综合、实现与下载。 熟悉 Minisys 实验箱的功能和使用方法。

二、实验内容

(1)以一个简单的 24 位拨码开关的读和 24 位 LED 灯的输出电路为例, 利用 Verilog HDL语言,在 Vivado 中创建简单的 24 位拨码开关的输入和 24 位 LED 灯的输出电路会将设计下载到 Minisys 实验平台。 (见《数字逻辑电路》实验讲义2.1.1)

(2)实现一位比较器或加法器(门级或数据流级建模),仿真并下载到实验平台。熟悉 Vivado 的开发环境及开发流程,掌握 Vivado 中 Verilog HDL 文本输入设计方法, 包括仿真、综合、实现与下载。 熟悉 Minisys 实验箱的功能和使用方法。

三、代码与截图

源代码1:test_204.v

`timescale 1ns / 1ps

//

module test_204(

input [23:0] sw,

output [23:0] led

);

assign led=sw;//将拨码开关内容赋值给LED

endmodule测试代码1:test_204_sim.v

`timescale 1ns / 1ps

//

module test_204_sim();

//input

reg [23:0] sw = 24'h000000;

//output

wire [23:0] led;

//instantiate the Unit under test-

test_204 uut(//“test_204”部分必须为源代码名字

.sw(sw),

.led(led)

);

always #10 sw = sw+1;

endmodule引脚约束1:text_204.xdc

set_property IOSTANDARD LVCMOS33 [get_ports {led[23]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[22]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[21]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[20]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[19]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[18]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[17]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[16]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[15]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[14]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[13]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[12]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[11]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[10]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[9]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[8]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[7]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[6]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[5]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[4]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[23]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[22]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[21]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[20]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[19]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[18]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[17]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[16]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[15]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[14]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[13]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[12]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[11]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[10]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[9]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[8]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[7]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[6]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[5]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[4]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {sw[0]}]

set_property SLEW SLOW [get_ports {led[23]}]

set_property SLEW SLOW [get_ports {led[22]}]

set_property SLEW SLOW [get_ports {led[21]}]

set_property SLEW SLOW [get_ports {led[20]}]

set_property SLEW SLOW [get_ports {led[19]}]

set_property SLEW SLOW [get_ports {led[18]}]

set_property SLEW SLOW [get_ports {led[17]}]

set_property SLEW SLOW [get_ports {led[16]}]

set_property SLEW SLOW [get_ports {led[15]}]

set_property SLEW SLOW [get_ports {led[14]}]

set_property SLEW SLOW [get_ports {led[13]}]

set_property SLEW SLOW [get_ports {led[12]}]

set_property SLEW SLOW [get_ports {led[11]}]

set_property SLEW SLOW [get_ports {led[10]}]

set_property SLEW SLOW [get_ports {led[9]}]

set_property SLEW SLOW [get_ports {led[8]}]

set_property SLEW SLOW [get_ports {led[7]}]

set_property SLEW SLOW [get_ports {led[6]}]

set_property SLEW SLOW [get_ports {led[5]}]

set_property SLEW SLOW [get_ports {led[4]}]

set_property SLEW SLOW [get_ports {led[3]}]

set_property SLEW SLOW [get_ports {led[2]}]

set_property SLEW SLOW [get_ports {led[1]}]

set_property SLEW SLOW [get_ports {led[0]}]

set_property PACKAGE_PIN W14 [get_ports {led[23]}]

set_property PACKAGE_PIN Y14 [get_ports {led[22]}]

set_property PACKAGE_PIN AB11 [get_ports {led[21]}]

set_property PACKAGE_PIN AB12 [get_ports {led[20]}]

set_property PACKAGE_PIN AA9 [get_ports {led[19]}]

set_property PACKAGE_PIN AB10 [get_ports {led[18]}]

set_property PACKAGE_PIN AA10 [get_ports {led[17]}]

set_property PACKAGE_PIN AA11 [get_ports {led[16]}]

set_property PACKAGE_PIN V10 [get_ports {led[15]}]

set_property PACKAGE_PIN W10 [get_ports {led[14]}]

set_property PACKAGE_PIN Y11 [get_ports {led[13]}]

set_property PACKAGE_PIN Y12 [get_ports {led[12]}]

set_property PACKAGE_PIN W11 [get_ports {led[11]}]

set_property PACKAGE_PIN W12 [get_ports {led[10]}]

set_property PACKAGE_PIN V13 [get_ports {led[9]}]

set_property PACKAGE_PIN V14 [get_ports {led[8]}]

set_property PACKAGE_PIN U15 [get_ports {led[7]}]

set_property PACKAGE_PIN V15 [get_ports {led[6]}]

set_property PACKAGE_PIN T14 [get_ports {led[5]}]

set_property PACKAGE_PIN T15 [get_ports {led[4]}]

set_property PACKAGE_PIN W15 [get_ports {led[3]}]

set_property PACKAGE_PIN W16 [get_ports {led[2]}]

set_property PACKAGE_PIN T16 [get_ports {led[1]}]

set_property PACKAGE_PIN U16 [get_ports {led[0]}]

set_property PACKAGE_PIN Y19 [get_ports {sw[23]}]

set_property PACKAGE_PIN V18 [get_ports {sw[22]}]

set_property PACKAGE_PIN V19 [get_ports {sw[21]}]

set_property PACKAGE_PIN AA19 [get_ports {sw[20]}]

set_property PACKAGE_PIN AB20 [get_ports {sw[19]}]

set_property PACKAGE_PIN V17 [get_ports {sw[18]}]

set_property PACKAGE_PIN W17 [get_ports {sw[17]}]

set_property PACKAGE_PIN AA18 [get_ports {sw[16]}]

set_property PACKAGE_PIN AB18 [get_ports {sw[15]}]

set_property PACKAGE_PIN U17 [get_ports {sw[14]}]

set_property PACKAGE_PIN U18 [get_ports {sw[13]}]

set_property PACKAGE_PIN P14 [get_ports {sw[12]}]

set_property PACKAGE_PIN R14 [get_ports {sw[11]}]

set_property PACKAGE_PIN R18 [get_ports {sw[10]}]

set_property PACKAGE_PIN T18 [get_ports {sw[9]}]

set_property PACKAGE_PIN N17 [get_ports {sw[8]}]

set_property PACKAGE_PIN P17 [get_ports {sw[7]}]

set_property PACKAGE_PIN P15 [get_ports {sw[6]}]

set_property PACKAGE_PIN R16 [get_ports {sw[5]}]

set_property PACKAGE_PIN N13 [get_ports {sw[4]}]

set_property PACKAGE_PIN N14 [get_ports {sw[3]}]

set_property PACKAGE_PIN P16 [get_ports {sw[2]}]

set_property PACKAGE_PIN R17 [get_ports {sw[1]}]

set_property PACKAGE_PIN N15 [get_ports {sw[0]}]

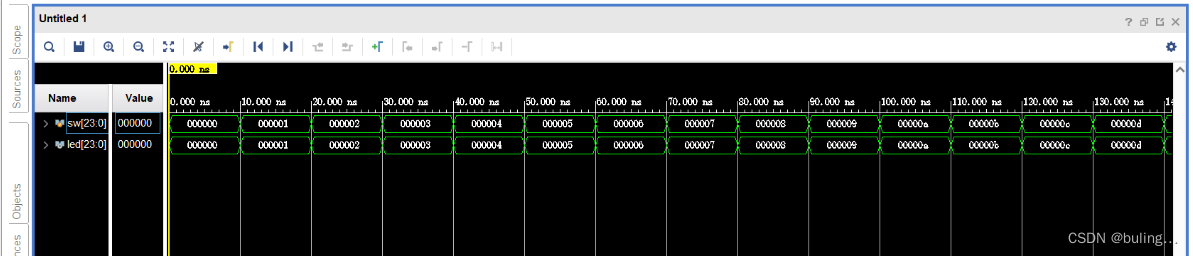

仿真截图1:

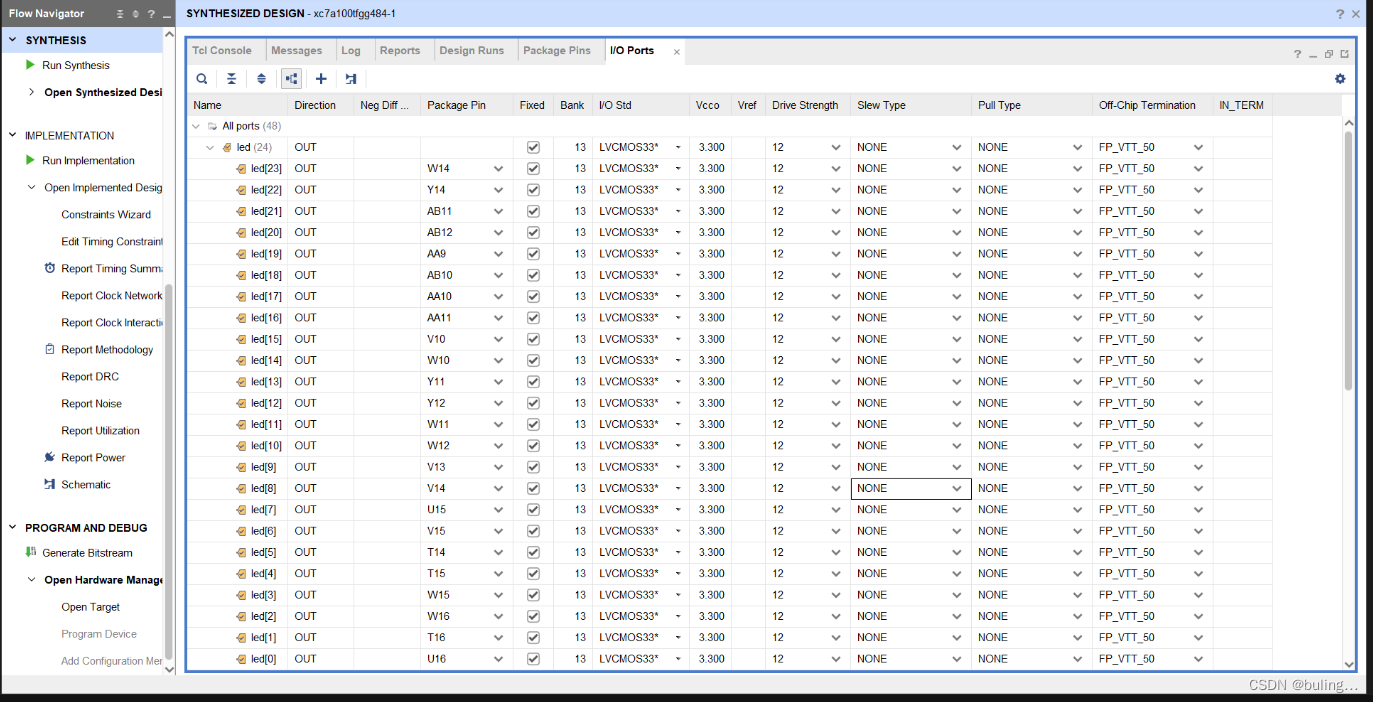

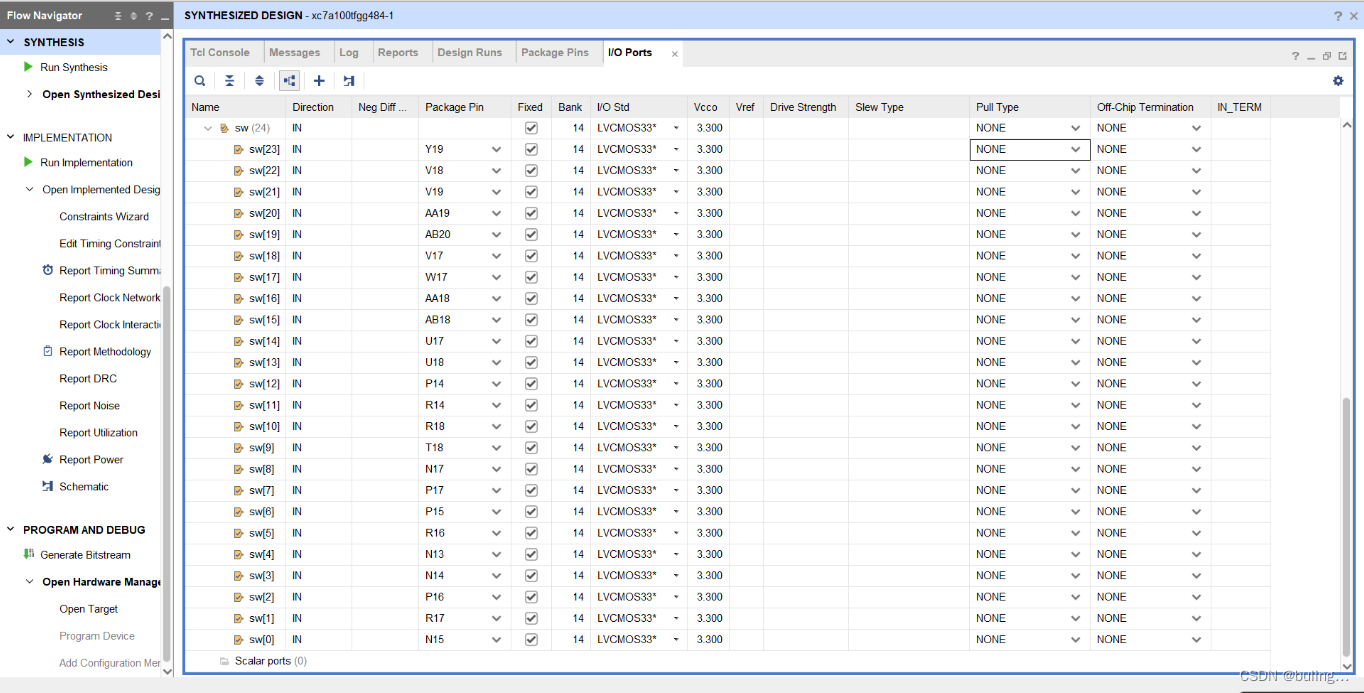

引脚锁定表截图1:

源代码2(一位比较器门级建模):test_2_204.v

`timescale 1ns / 1ps

//

module test_2_204(

input A,

input B,

output AgtB,

output AeqB,

output AltB

);

nand(nand1,A,B);

and(AgtB,A,nand1);

and(AltB,B,nand1);

xnor(AeqB,AgtB,AltB);

endmodule测试代码2(一位比较器门级建模):test_2_204_sim.v

`timescale 1ns / 1ps

//

module test_2_204_sim();

reg A,B;

wire AgtB,AeqB,AltB;

test_2_204 uut (

.A(A),

.B(B),

.AgtB(AgtB),

.AeqB(AeqB),

.AltB(AltB)

);

initial begin

A=0;

B=0;

#10

A=1;

B=0;

#10

A=0;

B=1;

$finish;

end

endmodule引脚约束2(一位比较器门级建模):test_2_204.xdc

set_property IOSTANDARD LVCMOS33 [get_ports A]

set_property IOSTANDARD LVCMOS33 [get_ports AeqB]

set_property IOSTANDARD LVCMOS33 [get_ports AgtB]

set_property IOSTANDARD LVCMOS33 [get_ports AltB]

set_property IOSTANDARD LVCMOS33 [get_ports B]

set_property PACKAGE_PIN Y9 [get_ports A]

set_property PACKAGE_PIN W9 [get_ports B]

set_property PACKAGE_PIN K17 [get_ports AeqB]

set_property PACKAGE_PIN L13 [get_ports AgtB]

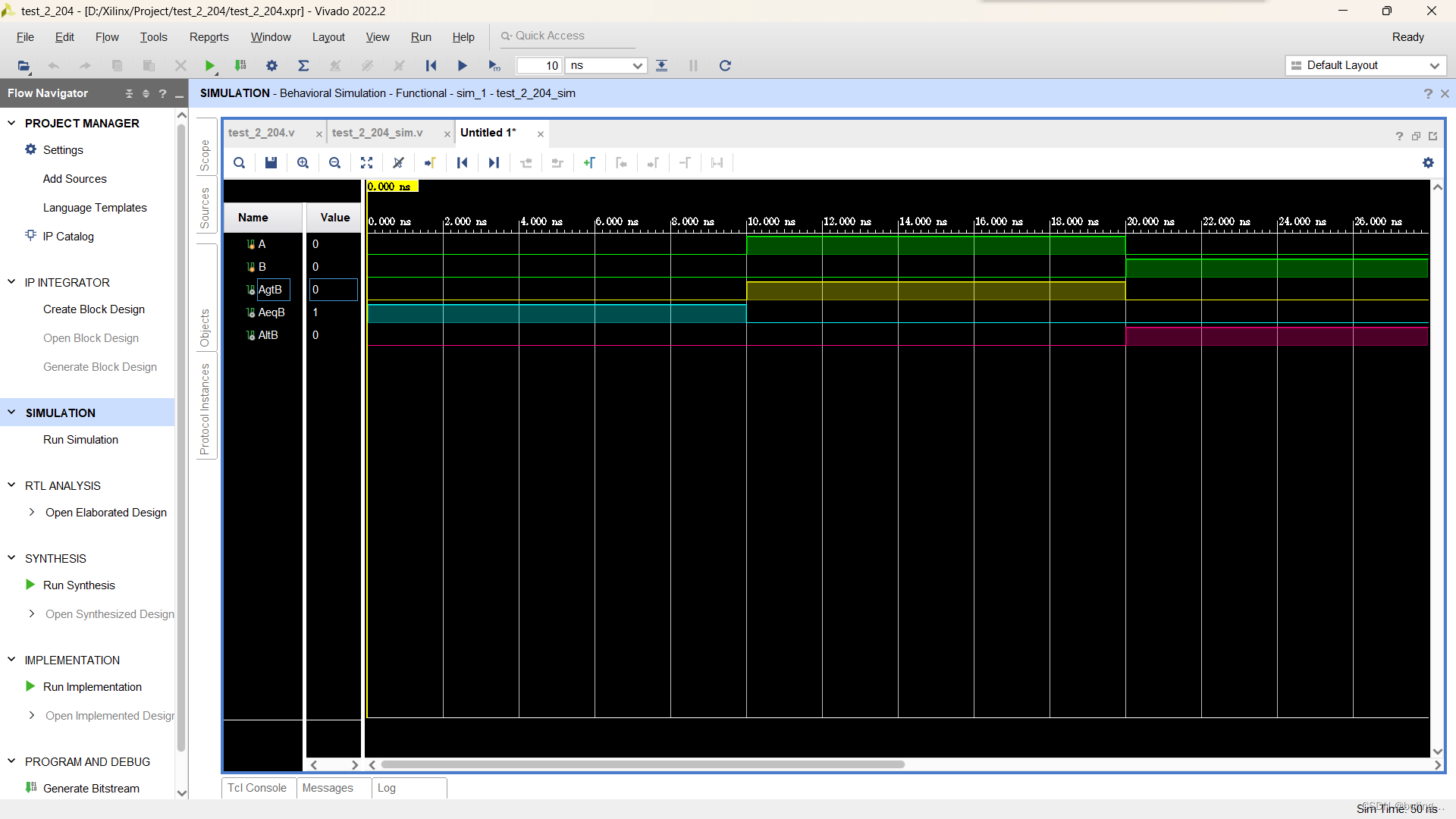

set_property PACKAGE_PIN M13 [get_ports AltB]仿真截图2:

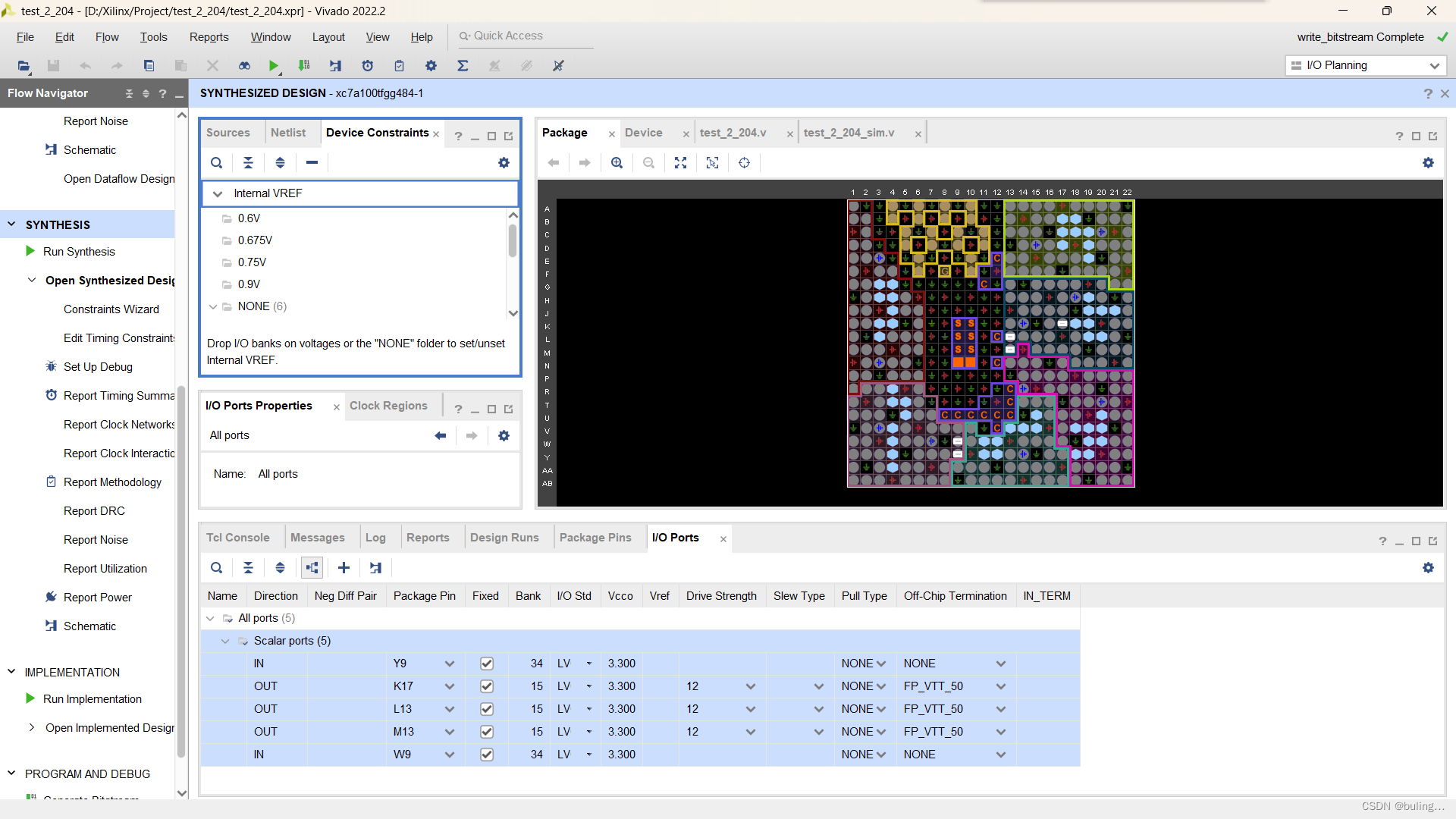

引脚锁定截图2:

四、下板验证结果

将比特流文件下到板上后,随意拨动拨码开关,可以发现当相应的开关被拨上、拨下后, 其对应的 LED 灯被点亮、熄灭。

3131

3131

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?