网上此类文章很多,这里暂时不放具体实现和测试结果,后续持续更新

下面引用一些帖子,帖子中涉及到具体做法

vcs联合编译v/sv/c++代码_sxlwzl的专栏-CSDN博客1,假设有三个top.svdpi.hdpi.cchttps://blog.csdn.net/sxlwzl/article/details/30017031用g++编译生成动态连接库*.so的方法及连接_farmwang的专栏-CSDN博客_g++编译动态库1、动态库*.so的编译这里我们用到4个文件,它们分别为:SoDemoTest.h、one.cpp、two.cpp、three.cpp。它们的内容如下: SoDemoTest.h#ifndef __SO_DEMO_TEST_HEADER__ #define __SO_DEMO_TEST_HEADER__ #include using namespace

https://blog.csdn.net/farmwang/article/details/72862088VCS/irun/verdi编译命令/.so联合编译/sv_lib/sv_liblist/sv_root_cy413026的博客-CSDN博客目录1.VCS的编译解析1.1一步编译法1.2 三步编译法1.3 VCS动态加载DPI shared lib (.so)2.irun编译命令3.verdi也可以编译1.VCS的编译解析1.1一步编译法这种适合都是verilog的工程下面是一个可以使用的vcs makefile用于编译VCS 编译仿真方法总结VCS编译命令摘自:SYNOPSYS...

https://blog.csdn.net/cy413026/article/details/84648952vcs中systemverilog和c/c++联合仿真_kevindas的博客-CSDN博客前言systemverilog中,可以通过DPI、PLI来与外部其它语言的程序进行交互。PLI又分为三类,TF、ACC和VPI,可以认为是PLI技术的三代演进:其中VPI(PLI3.0)是TF/ACC的一个超集,目前使用的PLI基本上都是VPI。与PLI技术相独立的另一个技术就是DPI,DPI技术简化了systemverilog与foreign language的交互步骤,对于开发者相对友好,所以使用相对广泛一些。本文不对DPI中程序调用/数据交互展开讨论(这部分可以参考绿皮书..

https://blog.csdn.net/kevindas/article/details/111414498

下面是官方文档

原理部分:sv标准中如下地方介绍sv与c的dpi接口调用

![]()

基本数据类型

例子1.

例子2.

例子3.

例子4

例子5.

例子6.

例子7.

例子8.

例子9.

例子10.

例子11.

以下内容转载自:VCS+Verdi进行testbench调试_happy_daydayup的博客-CSDN博客_vcs+verdi

VCS+Verdi进行testbench调试

背景:

在进行testbench调试时,使用消息打印或者单纯的ucli进行调试效率较低,利用Verdi进行图形化界面调试可以提升效率。

方法:

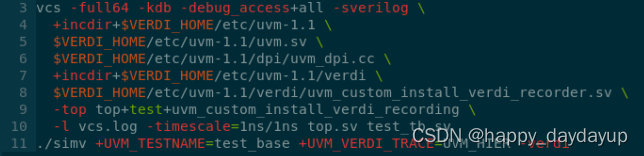

编译选项:-kdb

-ntb_opts uvm(用于后处理时查看uvm_hierachy_tree)

(有时候需要加-full64,不然可能启动不了verdi图形化界面,如果刚开始没加导致启动界面失败,需要删除原来的simv等文件,再重新编译,否则可能会报stack trace之类的错误)

仿真选项:-verdi

tips:

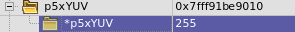

watch:在开始仿真时,会进入到verdi界面。在仿真暂停时,可以在左上角的导航栏切换到class标签(或者第一个instance标签,包含dut top),在搜索栏结合*搜索关注的class,如*refm*,class下面有此class的instance,点到instance,右边会显示member,class里的成员均可见,选择需要关注的成员watch(只进class不进instance时,里面的成员没法watch,且只有断点停在此范围,此范围的变量才可watch),可显示其值,包括联合数组,队列等,注意,class里的方法中的变量不可watch,所以有需要的话,需要改到class里声明变量,而不是在方法里声明。

断点:可在代码里的左边栏左击设置断点,执行到此处时会暂停;也可在member中对选中的变量设置断点,但对于数组,好像没法只关注某个成员的变化。再次点击断点标记,可以不使能此断点,再次点击,删除断点。想要get testbench中的变量时,不一定能get到,这时可以使用show命令看哪些能get到,当代码运行到某个class暂停时,其内的变量都是可以get的,其他class的成员,即使通过uvm_top.xxx的层次化引用,也get不到,所以如果想get某个class,或者某个方法里的变量,可以在其内设置断点。

checkerpoint:设置一个标记点,可以rewind到此点,相当于时光倒流。可用于改变某值,看之后什么情况,然后再回退回去。

UVM_HIERACHY:simv选择中加+UVM_VERDI_TRACE=HIER(UVM_AWARE不包含HIER功能),可以在tools-UVM_DEBUG中选择显示uvm_hierachy tree,看UVM结构树,属于后处理,即仿出波形并停止后,才能进行。

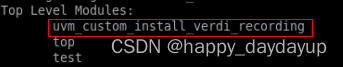

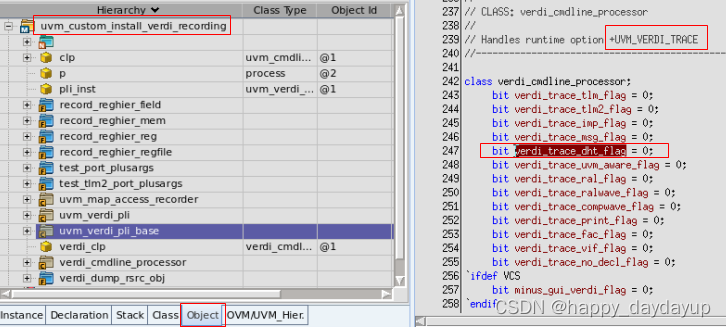

在加载自己的uvm_dpi.cc时,可能会存在无法显示uvm hier的情况,并且加ntb_opts uvm选项会失败(dpi重复),这时可以发现编译log里的Top level没有下图中的uvm_custom_install...文件,而UVM_HEIR就是依赖这些文件,所以需要自己加上这个文件,-top要么不指定,指定就要指定全。

SVA debug: 可方便的进行SVA的调试,观察成功、失败等波形情况,也可添加临时的断言而不用重新编译仿真。需要在仿真时开启fsdbDumpSVA 0 top.xxx,或者在平台文件里调用$fsdbDumpSVA(0,top.xxx),属于后处理,需在波形仿出并停止后才能进行,可通过tools-property-evaluator/analyzer/statistic/add temp sva进行相应的调试。

restore/save session: 可保存回复session

debug c:

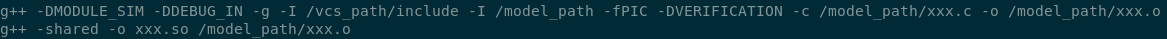

verdi可以debug c,前提是使用动态链接库.so,且生成库时需要加入-DMODULE_SIM -g等选项(如果刚开始没加-g,后面加-g重新编译前注意清空之前的生成的.o文件,以免出错)。

之后,在simulation选项中打开enable c/c++ debug开关,等待片刻后,选择show extern functions,就可以看到加载进来的c程序了,双击c程序进入后,可以设置断点。

tips1: 设置断点后,c程序为当前scope时,不可保存checkpoint,也不可恢复checkpoint,因为c是不消耗仿真时间的。但可以在进入或跳出c时,操作checkpoint。

tips2:可以对循环变量设置断点,方法是,进入到循环进程后,在local列表中右击对应的循环变量,set breakpoint,在condition中加入相应的条件。也可直接对行设置断点。

tips3:local/member列表里出现 数组名-*数组名的形式时,数组名的value是数组地址,*数组名的value是首个元素值。没法直接看数组中其他元素值。

UCLI:

get

force/release

run

具体可以在进入ucli模式时,使用xxx -help查看帮助文档。

目前ucli模式好像没法完成wait(xxx==yyy)的功能?对此,可在Verdi debug界面,通过设置断点时加condition条件完成此功能,命令为stop -change xxx -condition xxx==xxx,但是xxx不是层级化引用的名称(uvm_test_top.env.xxx),而是形如_vcs.abc@edf.xxx这种,只能通过Verdi界面右击相应变量设置,不能直接在ucli命令行输入(?)

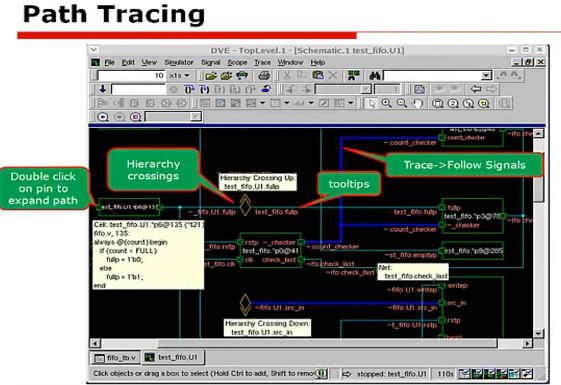

以下内容转载自:linux的dve界面如何debug,VCS课时3:使用DVE进行Debug_weixin_40002238的博客-CSDN博客

1. 使用DVE进行Debug

PPT1 课程目标

Unit Objectives

Learn to use basic features for debugging RTL

An introduction to the basic features

'Waveform debugging 、

Source code debugging

Listing features

Assertions

''C/C+ + " debugger

Analyzing design components

'Memories, busses, gates

仿真的log文件和波形结合效率比较高

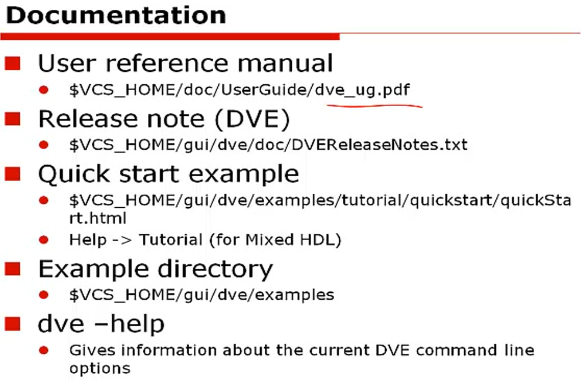

PPT2 DVE提供的文档

问题搞不定的时候,google

2. DVE介绍

PPT1 DVE的特性

DVE (Discovery Visual Environment) ■ An intuitive and easy to use GUI ■ Quickly Find Bugs

• RTL or Gates • Assertions • Testbench

■ Supports

• Interactive(设计验证初期,互动的模式,验证收敛的时候) • Post-simulation analysis(随机测试,脚本调用命令)

■ Multiple Languages

• Verilog • VHDL • SystemVerilog • SystemC • C/C++

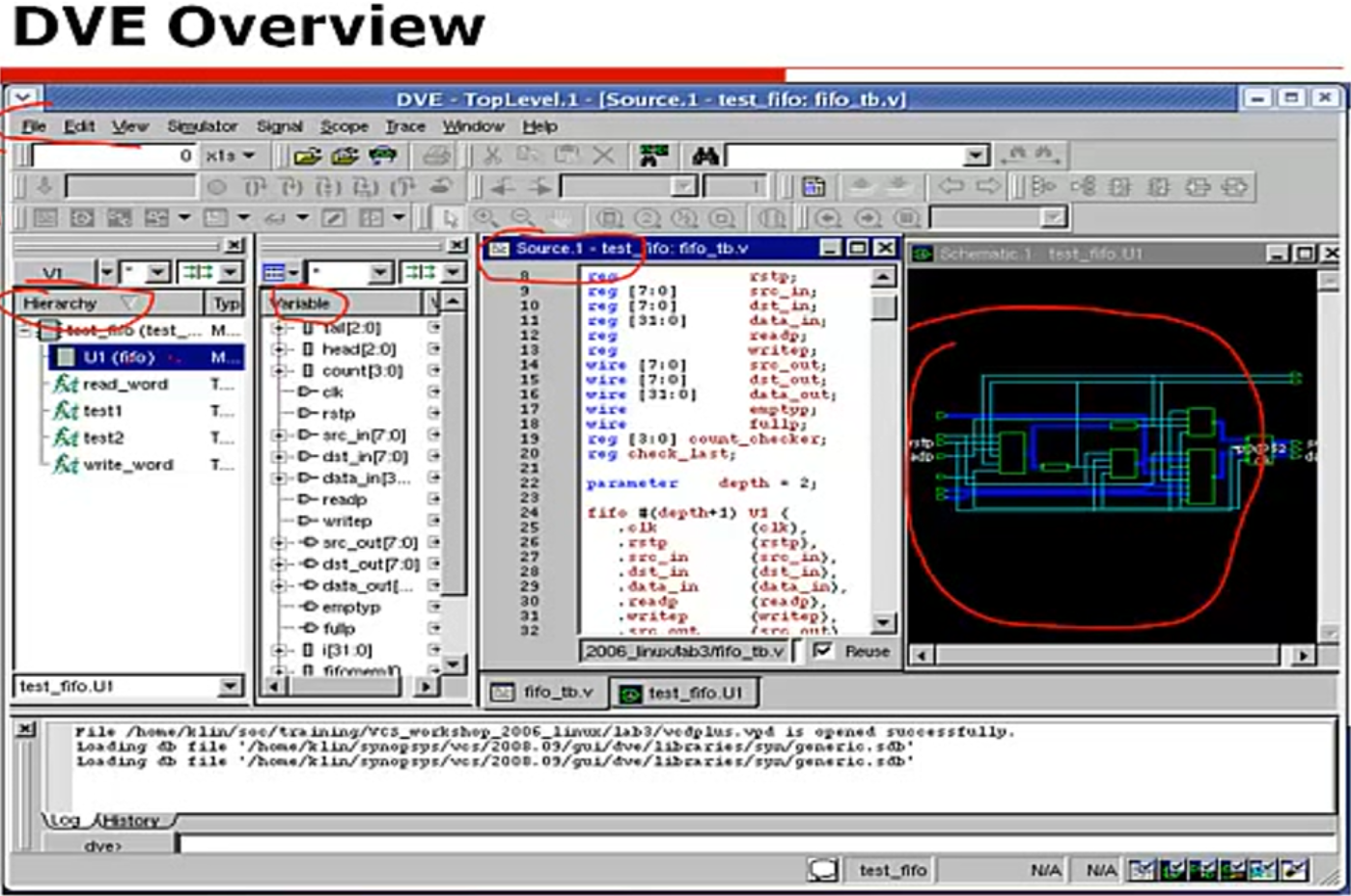

PPT2 DVE的界面

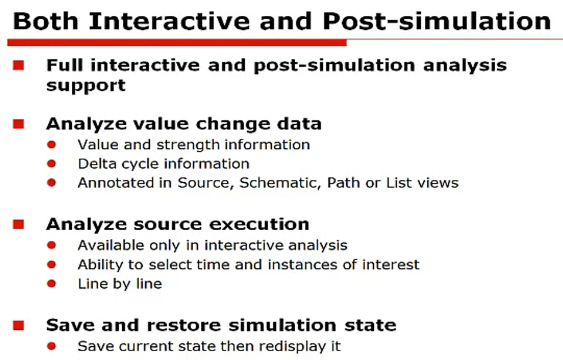

PPT3 交互式和后仿真

Annotated标注

PPT4

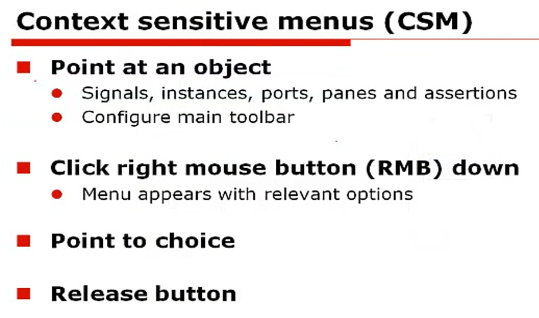

上下文相关菜单

3. DVE的启动

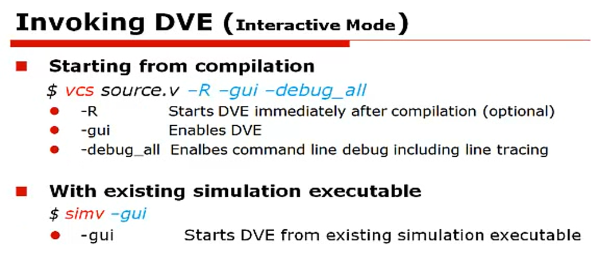

PPT1

PPT2

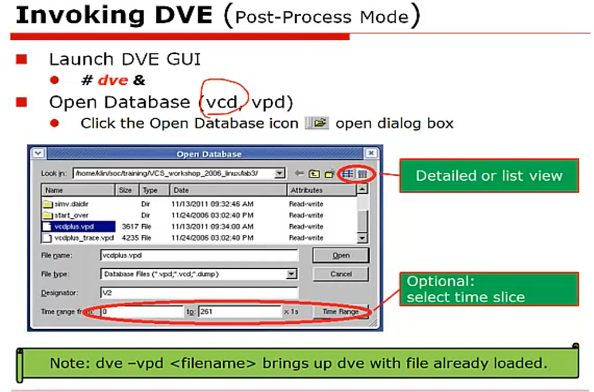

老的波形文件存储为vcd格式,占用空间比较大,后面改进为vpd占用空间比较小,加载的内存也小

verdi用的是fsdb,主流的是vcd和vpd

&后台执行的方式

PPT3

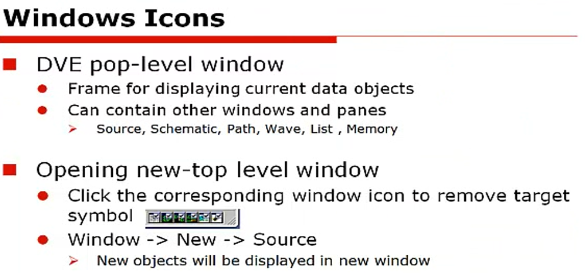

和windows下面的选项

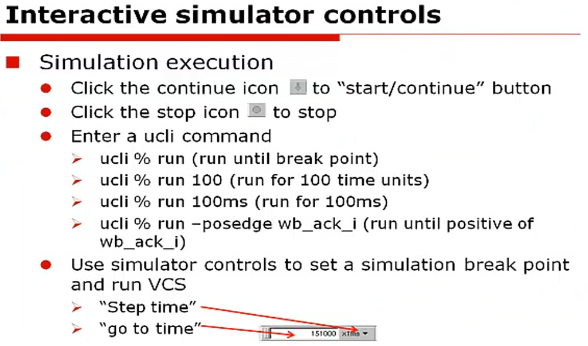

4. 交互式仿真

PPT1

PPT2

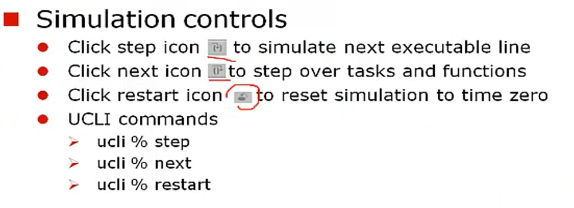

单步调试设置断点

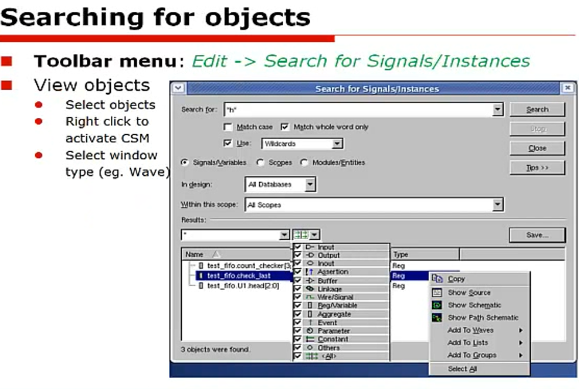

5. 文件的查找

6. 波形的窗口

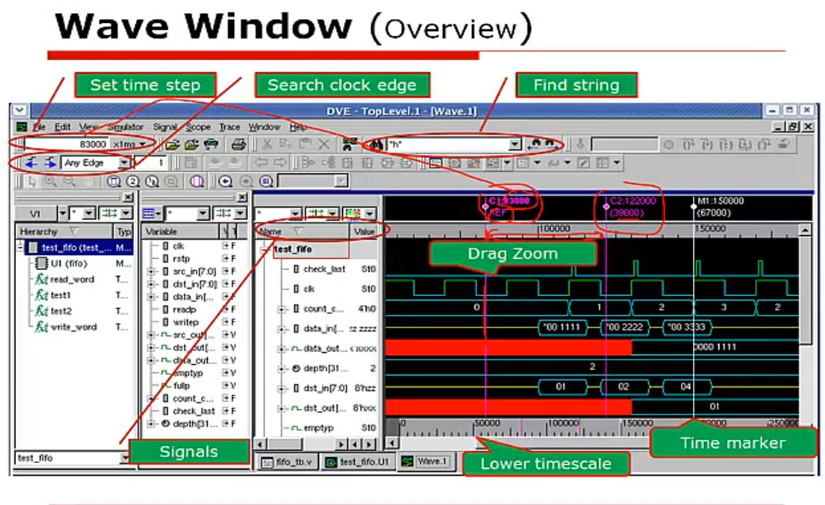

PPT1

可以对仿真的步长设置,查找时钟边缘,查找变量

PPT2

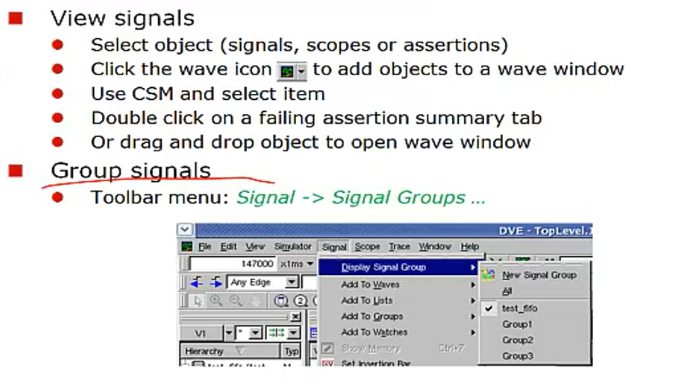

对信号分组

PPT3

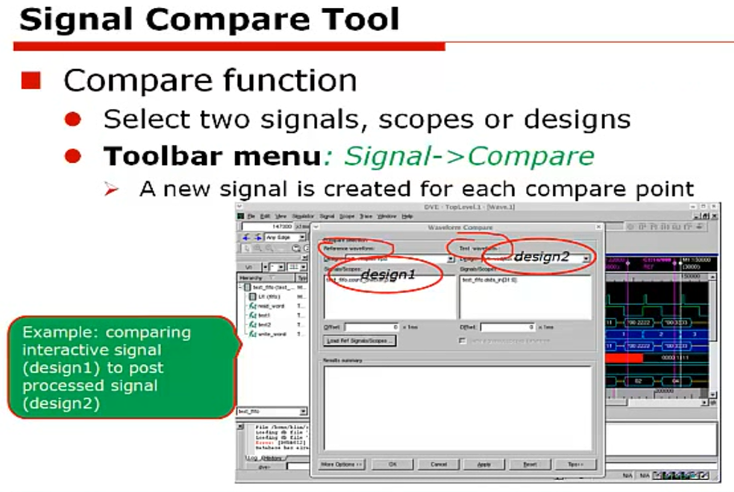

对信号的比较

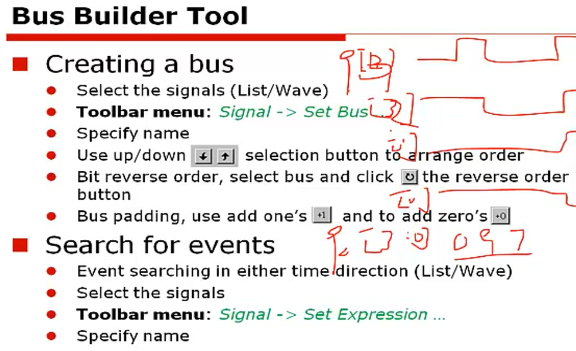

7. 建立BUS

PPT1

PPT2

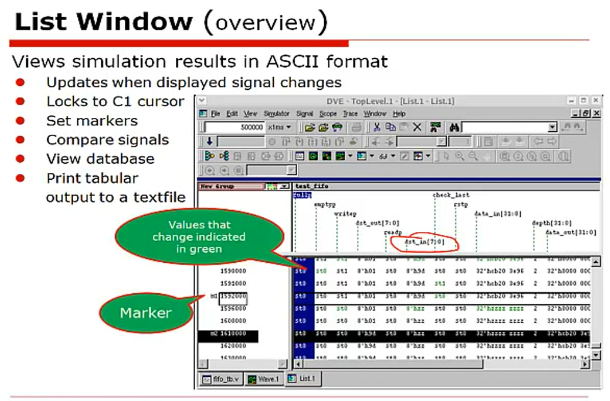

8. List Windows&Other

PPT1

PPT2

(图片加载不出来。。。)

最后把Memory的波形也dump

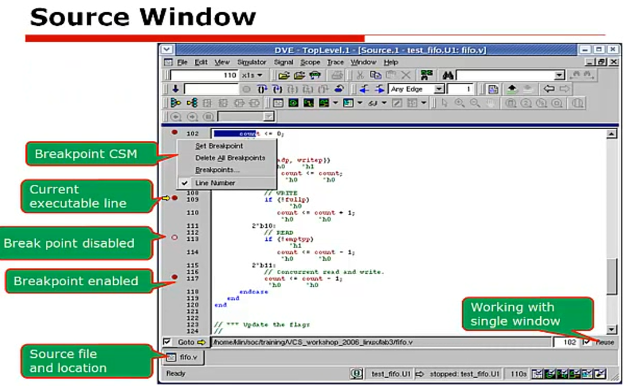

PPT3

源代码中插入断点

PPT4

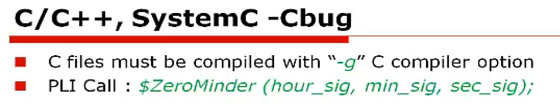

验证过程用到C语言的模型

PPT5

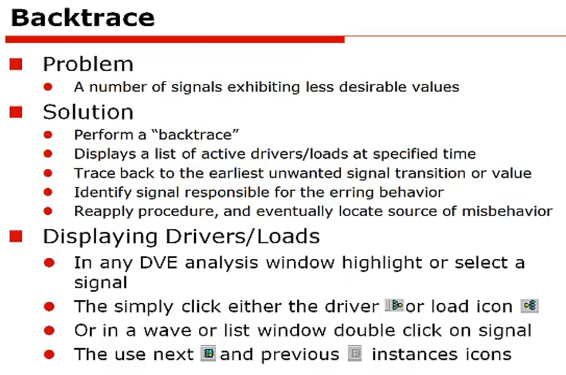

9.电路原理图

PPT1

PPT2

10 实验部分

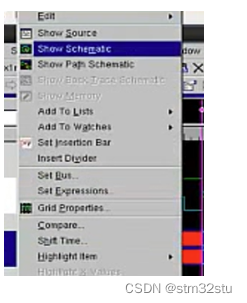

![]()

![]()

执行后run一下

启动对应的进程号

点一个module显示所有的端口,task是没有信号的,funtion他们是动态的,所以task function需要monitor

add to wave form

拖动信号

按照鼠标中键,新增加标轴

波形放大缩小

区域性放大

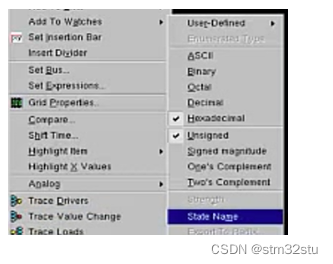

设置信号的进制

波形里面以状态的形式(state name)

信号的分组和命名

查找7有没有出现

两个信号的比较,产生了一个新的信号

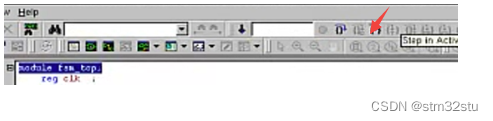

单步调试

进入到task funtion

构造一条BUS

crtl+选择信号,给总线命名

verilog调用C语言写的

使用gdb进行调试???

直接使用如下命令

gdb --args 仿真命令(case仿真时使用的命令)

以下内容转载自:VCS中的DPI和PLI_特别菜的菜鸡的博客-CSDN博客

1.DPI

在VCS中,DPI(Direct Programming Interface)是一种机制,用于在Verilog和C/C++代码之间进行互操作。DPI允许从Verilog代码中直接调用C/C++函数,并允许C/C++代码直接访问Verilog模块的内部信号和状态。

DPI的主要用途是为仿真器提供更高级别的功能和控制,并将仿真器与其他软件工具进行集成。使用DPI,用户可以通过C/C++代码实现复杂的仿真和调试功能,并将其集成到仿真器中。DPI还可以用于与其他工具进行交互,例如从仿真器中调用外部库或程序,或将仿真器的结果传输到其他工具中进行分析。

在VCS中,DPI函数定义在C/C++代码中,并通过特殊的DPI导出声明与Verilog代码进行关联。这使得Verilog代码可以直接调用DPI函数,而C/C++代码可以访问Verilog模块的内部信号和状态。

以下是使用DPI从Verilog代码中调用C/C++函数的示例:

module my_module;

import "DPI-C" function void my_c_function(input int a, input int b);

// ...

initial begin

my_c_function(10, 20);

end

endmodule在上面的示例中,Verilog模块"my_module"通过import语句声明了一个DPI-C函数"my_c_function"。然后,该函数可以在Verilog代码中直接调用,并传递参数10和20。在C/C++代码中,可以使用特殊的DPI导入声明访问Verilog模块的内部信号和状态。

2.PLI

PLI(Programming Language Interface)是一种机制,用于在Verilog和C/C++代码之间进行互操作。PLI允许从Verilog代码中直接调用C/C++函数,并允许C/C++代码直接访问Verilog模块的内部信号和状态。

PLI的主要用途是为仿真器提供更高级别的功能和控制,并将仿真器与其他软件工具进行集成。使用PLI,用户可以通过C/C++代码实现复杂的仿真和调试功能,并将其集成到仿真器中。PLI还可以用于与其他工具进行交互,例如从仿真器中调用外部库或程序,或将仿真器的结果传输到其他工具中进行分析。

在VCS中,PLI函数定义在C/C++代码中,并通过特殊的PLI导出声明与Verilog代码进行关联。这使得Verilog代码可以直接调用PLI函数,而C/C++代码可以访问Verilog模块的内部信号和状态。

以下是使用PLI从Verilog代码中调用C/C++函数的示例:

module my_module;

initial begin

$my_pli_function(10, 20);

end

endmodule在上面的示例中,Verilog代码使用$符号调用了一个名为"my_pli_function"的PLI函数,并传递了参数10和20。在C/C++代码中,可以使用特殊的PLI导入声明访问Verilog模块的内部信号和状态,并在函数中实现复杂的仿真和调试功能。

3.DPI和PLI的区别

在VCS中,PLI和DPI都是用于在Verilog和C/C++代码之间进行互操作的机制。它们都允许从Verilog代码中直接调用C/C++函数,并允许C/C++代码直接访问Verilog模块的内部信号和状态。但是,它们有以下区别:

- DPI是SystemVerilog中的新机制,而PLI是Verilog中的旧机制。DPI提供了更多的功能和灵活性,而PLI则比较受限制。

- DPI是一种严格类型化的接口,它强制要求在C/C++代码和Verilog代码之间进行类型匹配。这样可以提高代码的可读性和可维护性,并减少由类型错误引起的错误。PLI则不是严格类型化的接口,这意味着需要在代码中进行更多的类型转换和检查。

- DPI允许从C/C++代码中访问Verilog中的多个实例,而PLI则只能访问单个实例。这使得DPI更适合于处理多个实例的仿真和调试问题。

- DPI提供了更高级别的功能和控制,例如Task和Function,这些功能不是PLI所具备的。DPI还提供了一些额外的工具,例如svdpi.h和svdpi_gen.h,这些工具可以自动生成C/C++和SystemVerilog代码之间的接口。

总之,DPI和PLI都是在Verilog和C/C++之间进行互操作的机制,但DPI更为强大和灵活,而且更适合于处理多个实例的仿真和调试问题。

注:上至分隔线位置由chatGPT生成

以下内容转载自:https://www.cnblogs.com/-9-8/p/6306946.html

Verilog与C之间进行程序交互,PLI(Programming Language Interface)经过了TF,ACC,VPI等模式。

使用PLI可以生成延时计算器,来连接和同步多个仿真器,并可以通过波形显示等调试工具。

通过PLI方式连接一个简单的C程序,需要编写很多代码,并理解多仿真阶段的同步,调用段,实例指针等概念。

PLI方式给仿真带来了额外的负担,为了保护Verilog的数据结构,仿真器需要不断的在Verilog和C之间复制数据。

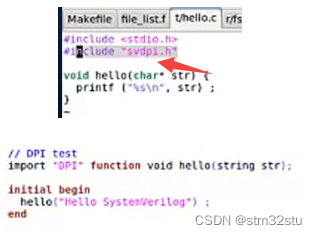

SystemVerilog引入了DPI(Direct Programming Interface),能够更简洁的连接C,C++或者其他非Verilog的编程语言。

只要使用import声明和使用,导入一个C子程序,就可以像调用SystemVerilog中的子程序一样来调用它。

SystemVerilog和C语言之间传递的最基本的数据类型是int,双状态的32位的数据类型,通过import声明定义C任务和函数的原型,带有返回值的C函数被映射成一个systemverilog的函数(function),

void类型的C函数被映射为一个systemverilog的任务(task)或者void 函数(function)。

通过“DPI-C”引入的C函数,可以直接在function中调用,但是只在该DPI被声明的空间内有效,

所以可以在package中将所有的DPI函数在做封装,打包为function。然后在需要的地方,import package。

使用关键字DPI-C表示,使用压缩值(packed)的方式来保存数据类型。

import "DPI-C" function int factorial(input int i);

program automatic test;

initial begin

for(int i=1;i<=10;i++)

$display("%0d != %0d",i,factorial(i)); //像调用正常的function int一样。

end //凡是可以声明function的地方,module,program,interface,package都可以import DPI

endprogram如果C函数名和SystemVerilog中的命名冲突,可以在import导入时,赋予新的函数名。

import "DPI-C" function void test(); //将C中的test函数,import进来,变为SV中的void function

import "DPI-C" test=function void my_test(); //将C中的test函数,修改名字为my_test。

通过DPI传递的每个变量都有两个相匹配的定义,一个在SystemVerilog中,一个在C语言中。 在使用中必须,确认使用的是兼容的数据类型。

C输出数据给SV,只能通过指针的方式,输出。所以输出数据也是在SV中建立空间,然后在C中得到指针,将值写进去,这样C的内存空间的控制不会影响到SV端。

SystemVerilog C(输入) C(输出)

byte char char*

short int short int short int*

int int int*

longint long long int long int*

real double double*

string const char* char**

string[N] const char** char**

bit svBit/unsigned char svBit*/unsigned char //注意在输出时,将不需要的高位屏蔽掉

logic/reg svLogic/unsigned char svLogic*/unsigned char* //注意在输出时,将不需要的高位屏蔽掉

bit[N:0] const svBitVecVal* svBitVecVal* //注意在输出时,将不需要的高位屏蔽掉

reg[N:0] const svLogicVecVal* svLogicVecVal* //注意在输出时,将不需要的高位屏蔽掉

open array[] const svOpenArrayHandle svOpenArrayHandle

chandle const void* void*

以上这些定义,都可以在svdpi.h中找到相应的操作函数。该头文件必须被包含到C函数实现端。

由于C中都是使用packed方式来表示数据的,所以import到SV的数据,也是使用packed的方式,而且SV仿真器不会对变量中未使用的高位,自动屏蔽。

所以在C语言中,需要保证这些变量的未使用的空间部分的值,也是初始化正确的。好让SV端,正确接收。

双状态变量使用svBit(实际存储空间是unsigned char)表示,双状态变量带下标使用svBitVecVal*表示。

四状态变量使用svLogic(实际存储空间是unsigned char)表示,四状态变量带下标使用svLogicVecVal*表示。

0---在C中对应0x0,1---在C中对应0x1,Z---在C中对应0x2,X---在C中对应0x3

logic[0:0] word 使用一对SVLogicVecVal来表示,一个域叫做aval--表示数值0/1,一个域叫做bval--表示x/z。

关于DPI调入的C的函数返回值,SV LRM推荐使用small values----void,byte,shortint,int,longint,real,shortreal,chandle,string,bit,logic。

不推荐使用bit[6:0]或者logic[6:0]这样的值,因为这样需要返回一个svBitVecVal或者svLogicVecVal的指针。

直接通过DPI调用C中的标准函数

import "DPI-C" function real sin(input real r);

initial $display("sin(0) = %f", sin(0.0));

被导入的C子程序,可以有多个参数或者没有参数,缺省情况下,参数的方向是input(数据从SystemVerilog流向C函数)

参数的方向也可以定义为output和inout,ref类型目前不支持。

(只表示在import语句和C环境中,经过封装之后的function,完全符合SV语法)

import "DPI-C" function int addmul(input int a, b, output int sum);

对输入的参数常常被定义为const。这样一旦对输入的变量进行写操作,C编译器就会报错。

int factorial (const int i) {}

连接C语言的例子。

#include <svdpi.h>

void counter7(svBitVecVal * o,

const svBitVecVal * i,

const svBit reset,

const svBit load)

{ static unsigned char count = 0;

if(reset) count = 0;

else if(load) count = * i;

else count++;

count &= 0x7F;

*o = count;

}

reset和load是一个双状态的比特信号,以svBit类型进行传递。

输入i是双状态7bit 变量,用svBitVecVal类型传递。

测试平台:

import “DPI-C” function void counter7(output bit [6:0] out,

input bit [6:0] in,

input bit reset, load);

program automatic counter;

bit[6:0] out, in;

bit reset, load;

initial begin

$monitor("SV: out=% 3d, in =%3d, reset = %0d, load = %0d\n", out,in,reset,load);

reset = 0;

load = 0;

in = 126;

out = 42;

counter7(out, in, reset, load);

end

endprogram

如果reset/load使用svLogic的类型,C程序中需要检查X、Z的状态

if(reset & 0x02) //检查变量bval中的X/Z

printf("reset val include X/Z value");

如果counter使用svLogicVal类型,C程序中检查X、Z的状态

counter.aval = inst->cnt;

counter.bval = 0; //aval与bval实际存在一个logicval的结构体中

chandle类型允许在System Verilog中存储一个C/C++的指针,指向一段地址,来保存一些常量。

typedef struct{unsigned char cnt;} c7;

void *counter7_new() { c7* c=(c7*) malloc (sizeof(c7));

c-> cnt = 0;

return c;}

void counter7(c7* inst, ...)

测试平台:

import “DPI-C” function chandle counter7_new();

import "DPI-C" function void counter7(input chandle inst, ...);

program automatic test;

initial begin

chandle inst1;

inst1 = counter7_new();

counter7(inst1,...);

end

endprogram

C与SV之间传递数组,可以是openarray,也可以是定宽数组。

定宽数组:

void fib(svBitVecVal data[20]) {

}

import "DPI-C" function void fib(output bit[31:0] data[20])

program automatic test;

bit[31:0] data[20];

initial begin

fib(data);

end

endprogram

openarray型指针,需要在C端通过svGetArrayPtr来得到来自SV的动态数据的地址。

其他类型的指针,可以直接在C中通过*ptr来赋值或调用。

void fib_oa(const svOpenArrayHandle data_oa) {

}

import "DPI-C" function void fib_ca(output bit[31:0]data[])

program automatic test;

bit[31:0] data[20],r;

fib_ca(data);

endprogram

openarray定义的查询方法:

int svSizeOfArray(h): 以字节计量的数组大小

int svSize(h,d): 维数d的元素总个数

int svLeft(h,d): 维数d的左边界, svLeft(h,1)一维数组的左边界,svleft(h,2)二维数组的左边界

int svRight(h,d): 维数d的右边界,=

openarray定义的定位函数:

void *svGetArrayPtr(h): 整个数组的存储位置

void *svGetArrElemPtr(h,i1,...): 数组中的一个元素

void *svGetArrElemPtr1(h,i1): 一维数组中的一个元素

void *svGetArrElemPtr2(h,i1,i2): 二维数组中的一个元素

使用DPI也可以将SV的function/task export到C环境中

module block;

export "DPI-C" function sv_display;

....

endmodule

extern void sv_display();

void c_display() {

sv_display();

}

820

820

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?