需求说明

DDC处理之后的数据为int16类型,进行调制调制模块处理需要转为int8类型。当前采用的处理方法为

r_SIG_CH1_I <= {i_i1_i0[15],i_i1_i0[14:8]} ;

该代码相当于对数据进行向下取整,或者说是向小取整。即大于零的数,舍掉小于256的数,相当于按照256取整,取整的小数部分舍去;小于零的数,相当于按照-256取整,小数部分向上加1.

r_SIG_CH1_I = floor( i_i1_i0/ 256 )

这种方法产生较大的量化误差。将原先小的负数,截取低8bit后,量化为了-1。小的正数,截取低8it后,量化为0. 这样就会产生较大的直流分量。

仿真验证

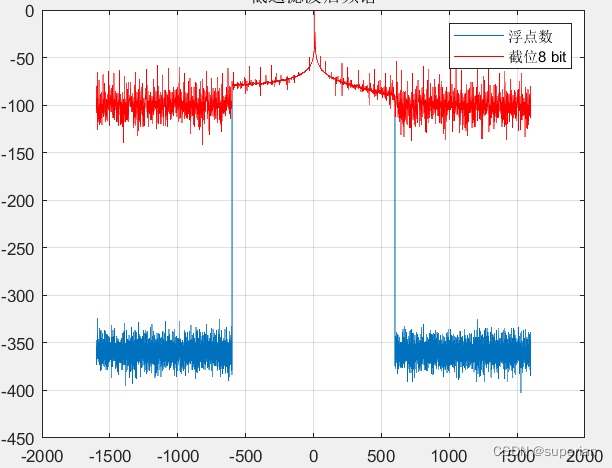

下图为截位8bit和原始数据的比对,可见截位8bit的数据动态范围,达到了将近100dB.

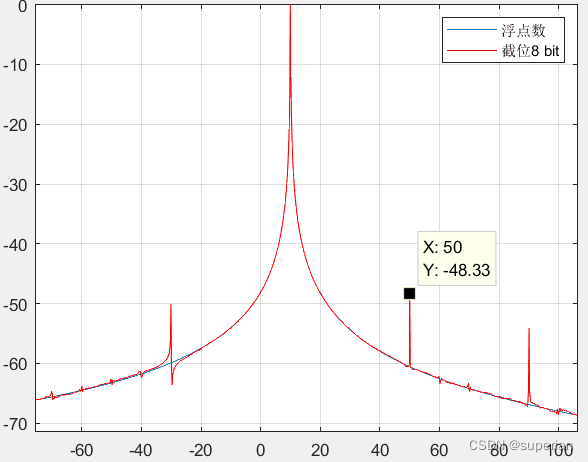

局部放大之后,可以看到最大谐波为-48dB,符合6.02dB一比特的关系

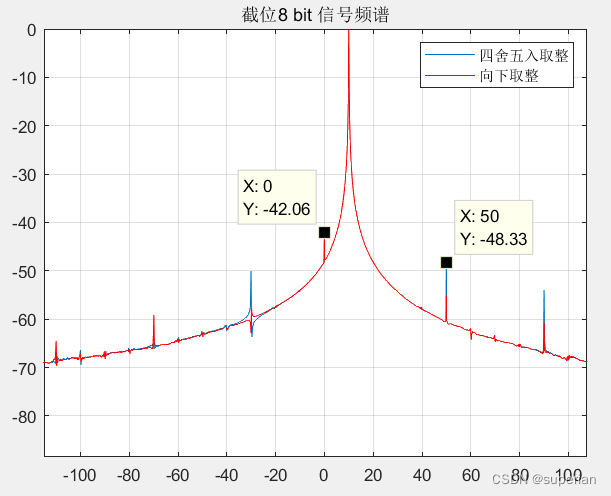

将向下取整和四舍五入取整方法对比,可以看到向下取整的谐波明显大于四舍五入。并且最大谐波就是在0频,就是直流误差造成。

FPGA代码修改

将第7bit参与到运算,实现四舍五入

r_SIG_CH1_I <= {i_i1_i0[15],i_i1_i0[14:8]} + i_i1_i0[7] ;

1522

1522

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?