Xilinx 7系列包括四个FPGA系列:Spartan系列是密度最低,成本最低的入门产品;Artix系列针对成本敏感的应用进行了优化;Kintex系列具有最佳的性价比;Vertex系列拥有最高的性能和容量。本篇文章是对7系列时钟资源的一个简单介绍。

7系列时钟资源通过全局时钟和区域时钟提供不同的时钟需求,CMT提供时钟频率合成、倾斜矫正、和过滤抖动等功能。

名词解释:

Clock Region :区域时钟

Clock Backbone:全局时钟线主干道

HROW:水平时钟线

CMT:时钟管理单元(MMCM:混合模式时钟管理器+PLL:锁相环)

BUFG:全局时钟缓冲区,驱动全局时钟线

BUFG特点:

①可以用作时钟启用电路,以启用或禁用跨越多个时钟区域的时钟。

②从发生故障的时钟源切换

③消除时钟分配延迟,调整相对于另一个时钟的时钟延迟

BUFIO:I/O时钟缓冲器

BUFR:区域时钟缓冲器

BUFMR:多区域时钟缓冲器

GT收发器

IBUFG(CC):具有时钟能力的IO输入

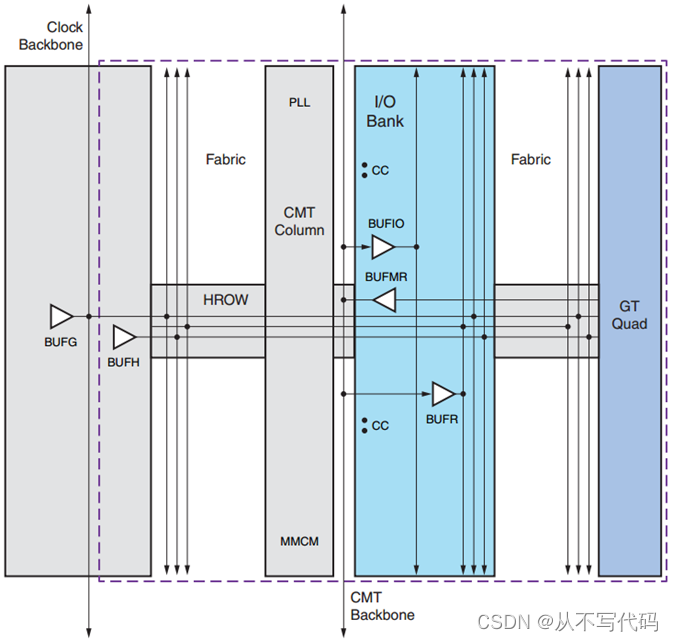

图1、 7系列FPGA高级时钟体系结构视图

如图1,该时钟区域水平方向上被分为3个时钟区域,所有水平时钟资源都包含在时钟区域水平时钟线(HROW)的中心,而垂直方向被时钟主干线分为左右两大块区域,垂直非区域时钟资源则包含在时钟主干或CMT主干中。

图2、单个时钟域试图

图2是单个时钟域的中的可用时钟资源和基本连接。全局时钟缓冲区可以通过HROW驱动到每个区域,即使不是物理位置。水平时钟缓冲器(BUFH)通过HROW驱动到该区域的每个时钟点。BUFG和BUFHs 在HROW中共享路由路径。I/O时钟缓冲器(BUFIO)和区域时钟缓冲(BUFR)位于I/O组内部。BUFIO仅驱动I/O时钟资源,而BUFR驱动I/O资源和逻辑资源。BUFMR支持BUFIO和BUFRs的多区域链接。支持时钟的输入将外部时钟连接到设备上的时钟资源。

图3、CMT框图

图3是CMT的时钟框图,由图可见,每个CMT单元可由多个时钟源作为输入,用作PLL和MMCM的驱动。PLL和MMCM在使用上对于一般时钟应用来说区别不大,但MMCM多了一个相位动态调整的功能。但是相应的占用面积比较大。

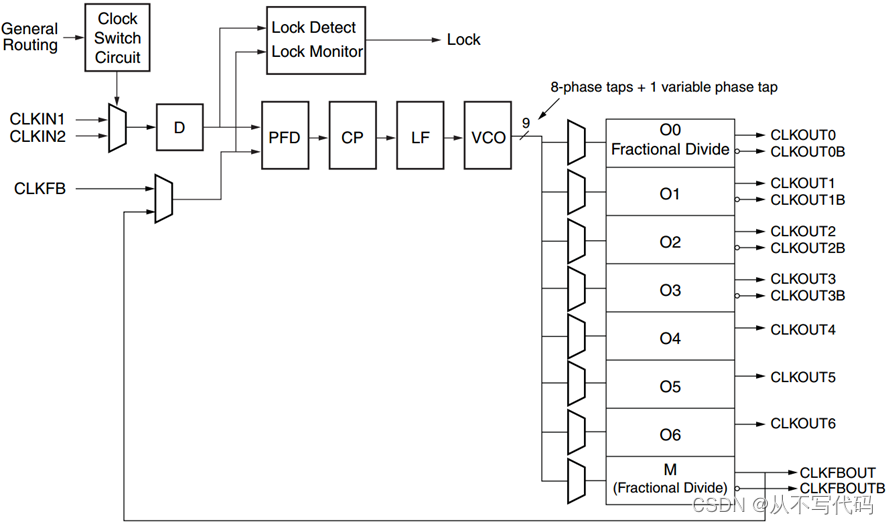

图4、MMCM混合模式时钟管理

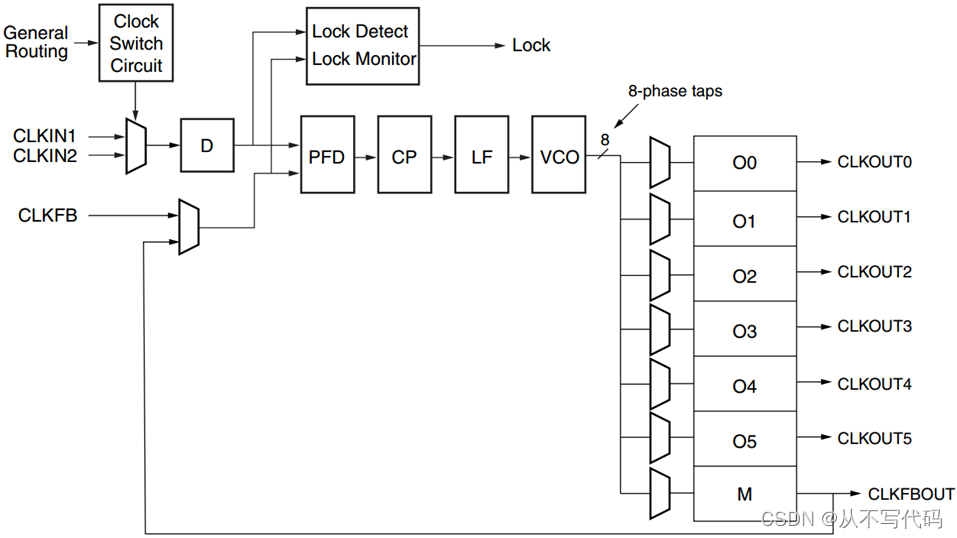

图5、锁相环

图5、锁相环

Lock信号拉高代表输出的是稳定的时钟信号。

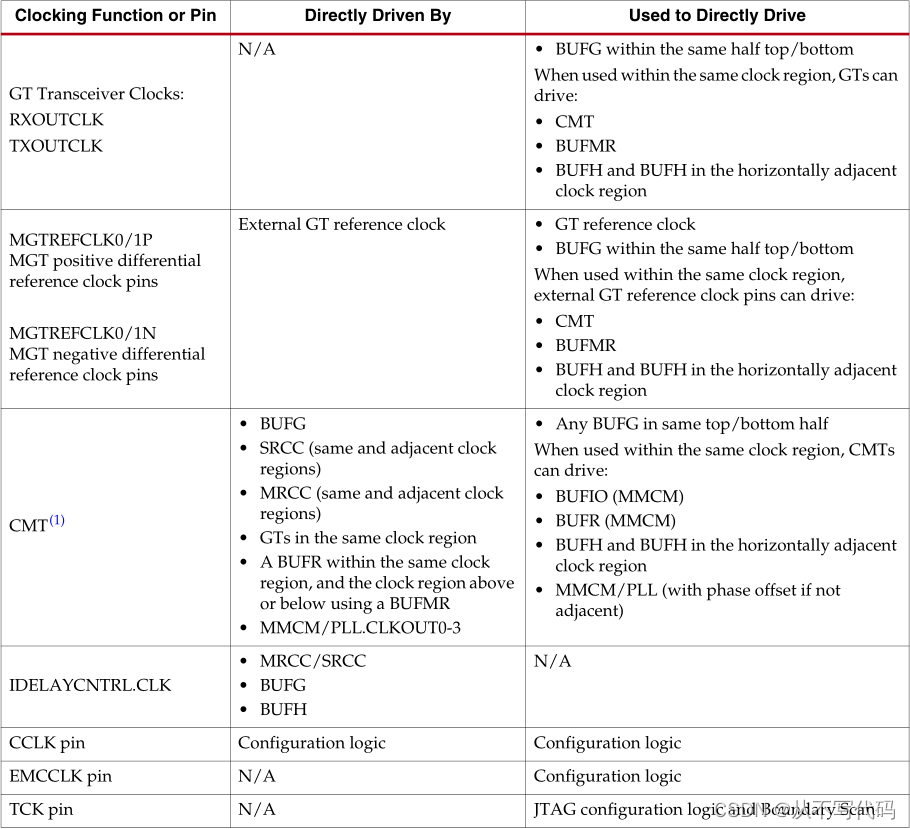

下面附上时钟连接总结表:

总结:

BUFG全局时钟可以控制所有的逻辑资源,BUFR区域时钟可以一个区域的时钟资源,BUFIO只能控制当前区域的IO时钟资源。

514

514

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?