试想,如果仅仅是简单把寄存器模型集成到验证环境,那么只要例化寄存器模型就可以了。现在主要的问题是,建立怎样的机制才可以让寄存器模型“实时”复刻RTL寄存器的值。为了解决这个问题,UVM引入Prediction机制,而且用到了两个新的组件:Adapter和Predictor。

今天,我们主要讲解一下 adapter 。

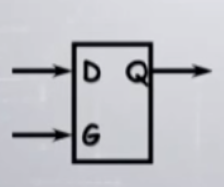

Adapter,可以翻译为适配器,它的作用是寄存器访问事务和总线事务的相互转换。

具体:将reg上抽象的uvm_reg_bus_op和bus_trans做一个转化。工作时,adapter一直保持监听,只要drv返回rsp到sequencer就会调用bus2reg函数。同理,如果是在寄存器上做操作,那么寄存器级别信息都会转换成uvm_reg_bus_op同时调用reg2bus函数。

adapter、sequencer、map三者的关系,首先需要在环境需要连接三者通过map.set_sequencer(squencer,adapter),因为本身reg model 充当sequence,adapter充当转换的桥梁,而regmodel 中因为有lock_model只有Map能访问内部reg的field,而对于传到bus上也需要用bus的sequencer进行和drv的传递,所以三者是要关联的,这样adapter才能工作。

寄存器访问事务:对数据的封装格式相对固定,一般包含读写类型、地址、数据和字节掩码。

总线事务:则根据不同的总线协议会有所不同。因此,Adapter扮演了中间做事务转换的角色,其主要实现的函数为reg2bus和bus2reg。

寄存器模型的前门访问操作可以分成读和写两种。无论是读或写,寄存器模型都会通过sequence产生一个uvm_reg_bus_op的变量,此变量中存储着操作类型(读还是写)和操作的地址,如果是写操作,还会有要写入的数据。

此变量中的信息要经过一个转换器(adapter)转换后交给bus_sequencer,随后交给bus_driver,由bus_driver实现最终的前门访问读写操作。因此,必须要定义好一个转换器。如下例为一个简单的转换器的代码:

文件:src/ch7/section7.2/my_adapter.sv

3 class my_adapter extends uvm_reg_adapter;

4 string tID = get_type_name();

5

6 `uvm_object_utils(my_adapter)

7

8 function new(string name="my_adapter");

9 super.new(name);

10 endfunction : new

11

12 function uvm_sequence_item reg2bus(const ref uvm_reg_bus_op rw);

13 bus_transaction tr;

14 tr = new("tr");

15 tr.addr = rw.addr;

16 tr.bus_op = (rw.kind == UVM_READ) BUS_RD: BUS_WR;

17 if (tr.bus_op == BUS_WR)

18 tr.wr_data = rw.data;

19 return tr;

20 endfunction : reg2bus

21

22 function void bus2reg(uvm_sequence_item bus_item, ref uvm_reg_bus_op rw);

23 bus_transaction tr;

24 if(!$cast(tr, bus_item)) begin

25 `uvm_fatal(tID,

26 "Provided bus_item is not of the correct type. Expecting bus_trans action")

27 return;

28 end

29 rw.kind = (tr.bus_op == BUS_RD) UVM_READ : UVM_WRITE;

30 rw.addr = tr.addr;

31 rw.byte_en = 'h3;

32 rw.data = (tr.bus_op == BUS_RD) tr.rd_data : tr.wr_data;

33 rw.status = UVM_IS_OK;

34 endfunction : bus2reg

35

36 endclass : my_adapter一个转换器要定义好两个函数:

一是reg2bus,其作用为将寄存器模型通过sequence发出的uvm_reg_bus_op型的变量转换成bus_sequencer能够接受的形式;

二是bus2reg,其作用为当监测到总线上有操作时,它将收集来的transaction转换成寄存器模型能够接受的形式,以便寄存器模型能够更新相应的寄存器的值。

说到这里,不得不考虑寄存器模型发起的读操作的数值是如何返回给寄存器模型的?

由于总线的特殊性,bus_driver在驱动总线进行读操作时,它也能顺便获取要读的数值,如果它将此值放入从bus_sequencer获得的bus_transaction中时,那么bus_transaction中就会有读取的值,此值经过adapter的bus2reg函数的传递,最终被寄存器模型获取。

这个过程如图7-5a所示。由于并没有实际的transaction的传递,所以从driver到adapter使用了虚线。转换器写好之后,就可以在base_test中加入寄存器模型了。

文件:src/ch7/section7.2/base_test.sv

4 class base_test extends uvm_test;

5

6 my_env env;

7 my_vsqr v_sqr;

8 reg_model rm;

9 my_adapter reg_sqr_adapter;

…

19 endclass

20

21

22 function void base_test::build_phase(uvm_phase phase);

23 super.build_phase(phase);

24 env = my_env::type_id::create("env", this);

25 v_sqr = my_vsqr::type_id::create("v_sqr", this);

26 rm = reg_model::type_id::create("rm", this);

27 rm.configure(null, "");

28 rm.build();

29 rm.lock_model();

30 rm.reset();

31 reg_sqr_adapter = new("reg_sqr_adapter");

32 env.p_rm = this.rm;

33 endfunction

34

35 function void base_test::connect_phase(uvm_phase phase);

36 super.connect_phase(phase);

37 v_sqr.p_my_sqr = env.i_agt.sqr;

38 v_sqr.p_bus_sqr = env.bus_agt.sqr;

39 v_sqr.p_rm = this.rm;

40 rm.default_map.set_sequencer(env.bus_agt.sqr, reg_sqr_adapter);

41 rm.default_map.set_auto_predict(1);

42 endfunction要将一个寄存器模型集成到base_test中,那么至少需要在base_test中定义两个成员变量,一是reg_model,另外一个就是reg_sqr_adapter。将所有用到的类在build_phase中实例化。在实例化后reg_model还要做四件事:第一是调用configure函数,其第一个参数是parent block,由于是最顶层的reg_block,因此填写null,第二个参数是后门访问路径,这里传入一个空的字符串。第二是调用build函数,将所有的寄存器实例化。第三是调用lock_model函数,调用此函数后,reg_model中就不能再加入新的寄存器了。第四是调用reset函数,如果不调用此函数,那么reg_model中所有寄存器的值都是0,调用此函数后,所有寄存器的值都将变为设置的复位值。

寄存器模型的前门访问操作最终都将由uvm_reg_map完成,因此在connect_phase中,需要将转换器和bus_sequencer通过set_sequencer函数告知reg_model的default_map,并将default_map设置为自动预测状态。

uvm_reg_adapter 源码分析:

//------------------------------------------------------------------------------

// Title: Classes for Adapting Between Register and Bus Operations

//

// This section defines classes used to convert transaction streams between

// generic register address/data reads and writes and physical bus accesses.

//------------------------------------------------------------------------------

//------------------------------------------------------------------------------

//

// Class: uvm_reg_adapter

//

// This class defines an interface for converting between <uvm_reg_bus_op>

// and a specific bus transaction.

//------------------------------------------------------------------------------

virtual class uvm_reg_adapter extends uvm_object;

// Function: new

//

// Create a new instance of this type, giving it the optional ~name~.

function new(string name="");

super.new(name);

endfunction

// Variable: supports_byte_enable

//

// Set this bit in extensions of this class if the bus protocol supports

// byte enables.

bit supports_byte_enable;

// Variable: provides_responses

//

// Set this bit in extensions of this class if the bus driver provides

// separate response items.

bit provides_responses;

// Variable: parent_sequence

//

// Set this member in extensions of this class if the bus driver requires

// bus items be executed via a particular sequence base type. The sequence

// assigned to this member must implement do_clone().

uvm_sequence_base parent_sequence;

// Function: reg2bus

//

// Extensions of this class ~must~ implement this method to convert the specified

// <uvm_reg_bus_op> to a corresponding <uvm_sequence_item> subtype that defines the bus

// transaction.

//

// The method must allocate a new bus-specific <uvm_sequence_item>,

// assign its members from

// the corresponding members from the given generic ~rw~ bus operation, then

// return it.

pure virtual function uvm_sequence_item reg2bus(const ref uvm_reg_bus_op rw);

// Function: bus2reg

//

// Extensions of this class ~must~ implement this method to copy members

// of the given bus-specific ~bus_item~ to corresponding members of the provided

// ~bus_rw~ instance. Unlike <reg2bus>, the resulting transaction

// is not allocated from scratch. This is to accommodate applications

// where the bus response must be returned in the original request.

pure virtual function void bus2reg(uvm_sequence_item bus_item,

ref uvm_reg_bus_op rw);

local uvm_reg_item m_item;

// function: get_item

//

// Returns the bus-independent read/write information that corresponds to

// the generic bus transaction currently translated to a bus-specific

// transaction.

// This function returns a value reference only when called in the

// <uvm_reg_adapter::reg2bus()> method.

// It returns ~null~ at all other times.

// The content of the return <uvm_reg_item> instance must not be modified

// and used strictly to obtain additional information about the operation.

virtual function uvm_reg_item get_item();

return m_item;

endfunction

virtual function void m_set_item(uvm_reg_item item);

m_item = item;

endfunction

endclass

//------------------------------------------------------------------------------

// Group: Example

//

// The following example illustrates how to implement a RegModel-BUS adapter class

// for the APB bus protocol.

//

//|class rreg2apb_adapter extends uvm_reg_adapter;

//| `uvm_object_utils(reg2apb_adapter)

//|

//| function new(string name="reg2apb_adapter");

//| super.new(name);

//|

//| endfunction

//|

//| virtual function uvm_sequence_item reg2bus(uvm_reg_bus_op rw);

//| apb_item apb = apb_item::type_id::create("apb_item");

//| apb.op = (rw.kind == UVM_READ) ? apb::READ : apb::WRITE;

//| apb.addr = rw.addr;

//| apb.data = rw.data;

//| return apb;

//| endfunction

//|

//| virtual function void bus2reg(uvm_sequencer_item bus_item,

//| uvm_reg_bus_op rw);

//| apb_item apb;

//| if (!$cast(apb,bus_item)) begin

//| `uvm_fatal("CONVERT_APB2REG","Bus item is not of type apb_item")

//| end

//| rw.kind = apb.op==apb::READ ? UVM_READ : UVM_WRITE;

//| rw.addr = apb.addr;

//| rw.data = apb.data;

//| rw.status = UVM_IS_OK;

//| endfunction

//|

//|endclass

//

//------------------------------------------------------------------------------

//------------------------------------------------------------------------------

//

// Class: uvm_reg_tlm_adapter

//

// For converting between <uvm_reg_bus_op> and <uvm_tlm_gp> items.

//

//------------------------------------------------------------------------------

class uvm_reg_tlm_adapter extends uvm_reg_adapter;

`uvm_object_utils(uvm_reg_tlm_adapter)

function new(string name = "uvm_reg_tlm_adapter");

super.new(name);

endfunction

// Function: reg2bus

//

// Converts a <uvm_reg_bus_op> struct to a <uvm_tlm_gp> item.

virtual function uvm_sequence_item reg2bus(const ref uvm_reg_bus_op rw);

uvm_tlm_gp gp = uvm_tlm_gp::type_id::create("tlm_gp",, this.get_full_name());

int nbytes = (rw.n_bits-1)/8+1;

uvm_reg_addr_t addr=rw.addr;

if (rw.kind == UVM_WRITE)

gp.set_command(UVM_TLM_WRITE_COMMAND);

else

gp.set_command(UVM_TLM_READ_COMMAND);

gp.set_address(addr);

gp.m_byte_enable = new [nbytes];

gp.m_byte_enable_length = nbytes;

gp.set_streaming_width (nbytes);

gp.m_data = new [gp.get_streaming_width()];

gp.m_length = nbytes;

for (int i = 0; i < nbytes; i++) begin

gp.m_data[i] = rw.data[i*8+:8];

gp.m_byte_enable[i] = (i > nbytes) ? 8'h00 : (rw.byte_en[i] ? 8'hFF : 8'h00);

end

return gp;

endfunction

// Function: bus2reg

//

// Converts a <uvm_tlm_gp> item to a <uvm_reg_bus_op>.

// into the provided ~rw~ transaction.

//

virtual function void bus2reg(uvm_sequence_item bus_item,

ref uvm_reg_bus_op rw);

uvm_tlm_gp gp;

int nbytes;

if (bus_item == null)

`uvm_fatal("REG/NULL_ITEM","bus2reg: bus_item argument is null")

if (!$cast(gp,bus_item)) begin

`uvm_error("WRONG_TYPE","Provided bus_item is not of type uvm_tlm_gp")

return;

end

if (gp.get_command() == UVM_TLM_WRITE_COMMAND)

rw.kind = UVM_WRITE;

else

rw.kind = UVM_READ;

rw.addr = gp.get_address();

rw.byte_en = 0;

foreach (gp.m_byte_enable[i])

rw.byte_en[i] = gp.m_byte_enable[i];

rw.data = 0;

foreach (gp.m_data[i])

rw.data[i*8+:8] = gp.m_data[i];

rw.status = (gp.is_response_ok()) ? UVM_IS_OK : UVM_NOT_OK;

endfunction

endclass

2600

2600

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?