由于近期找工作,所以把射频的一些基础知识复习了一遍。趁着自己还有点时间和精力,把锁相环的一些知识记录一下,基础功不扎实,有误之处还请大佬拍错。

1. PLL的工作原理

锁相环一般由PD(鉴相器),LPF(环路滤波器),VCO组成。

有的同学可能要问了:“既然VCO在给定电压之后已经能输出频率了,为什么不直接拿来用呢?”

实际上可以这么用,现在有的晶振会针对某个固定的频点把频率优化的非常好,比如一些122.88MHz的 VCXO(外置的VCO),这些晶振有个特点,在这个频点相噪性能优化的特别好。但是晶振一般很难把频率做高。而我们PLL中经常使用的VCO,频率变化中频都是GHz为单位,变化范围几百兆MHz,若使用开环VCO(不加PLL的结构),那么出来的频率信号相噪特别糟糕,而且随着电压变化(例如噪声,温度带来的影响)导致VCO的输出频率发生漂移。

于是有人提出了使用PLL这样的结构,能够输出比较稳定的(LOCKED)频率。其主要思想是利用一个相位比较干净的参考频率,建立一个闭环结构来获取到相位比较干净的高频频率。

如上图所示,输入信号经过鉴相器,当反馈信号和fref的相位一致的时候,PD输出一个恒定电压值(实际上由CP输出电流),从而使得这个系统稳定。

如果我们把PD简单看做一个乘法器,那么有参考输入信号

反馈输入的角频率为:

N一般表示为反馈DIV的分频比。

反馈输入信号为:

两者相乘根据积化和差可以得到高频和低频两个分量。其中高频的部分会被LPF滤掉。所以只剩低频部分。

对于低频部分,将相位记为:

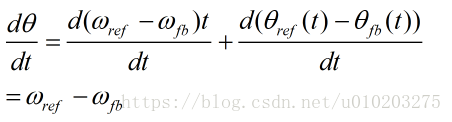

要使得系统稳定,即相位恒定,可以关于相位对时间t求导数,当等于0时可以认为两个相位一致。一般把

看做两个时钟的随机起振相位,上电后保持不变。所以有

当导数为0的时候:

此时有

假如此时参考频率10MHz,N为350,可以得到3.5GHz的频率输出。当然前提是PLL的VCO支持这个频段。

当然对于现在的芯片,鉴频器的参考频率输入前也有一个分频器或者倍频器,一般记为R。

2.PLL的环路带宽分析

锁相环设计的最重要一点在于LPF的设计。一般来说,对于LPF的拓扑结构都是固定的,无非是阶数的不同罢了,有的PLL芯片会内置LPF,通过配置R和C的大小调整带宽,不过一般来说为了性能以及空间受限,更多的PLL把系统把环路滤波器放在芯片外面。

很多初学PLL都会遇到一个问题,PLL的环路带宽怎么设计?一般来说LPF越窄,锁定时间越长,对一些杂散的抑制越好,但是同时也不能太窄,防止对VCO噪声抑制的不够。

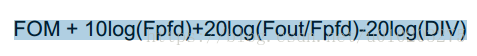

我们先来看一下PLL的相噪公式:

其中FOM表示鉴相器的噪底,需要注意的是DIV和上面说的DIV不是同一个东西。这里的DIV是指时钟分配器的分频系数。对于一些系统需要多个时钟,分配器可以将已经锁定的VCO作为多路时钟输出,但是在输出之前针对不同芯片具体所需要时钟不同,设置具体的分频值。可以看出,把鉴相频率Fpfd扩大两倍时候,相噪可以减少3dB,所以对于PLL如果可以的话建议使用比较高的鉴相频率,提高PLL的相噪性能,但是决定系统Fpfd也需要考虑PD的性能,一般来说PD的鉴相频率都有一定的范围。

我们来看一下大家经常看到的相噪图

一般来说噪声低频部分的噪声由参考频率的相噪贡献的,所以使用一个性能好的参考频率非常有必要。中频部分的噪声由PLL的鉴相器贡献,在此之后高频的基本由VCO贡献。

如果在带内出现杂散,一般会选择调整LPF,使得杂散落在带外自动滤除。有些杂散落在带内怎么处理的呢?一般来说杂散来自于电源上的低频噪声,这点就得从电源上着手检查了,具体我会在第三部分细讲。

窄带的LPF可以抑制带内噪声可以理解,但“LPF同时也不能太窄,防止对VCO噪声抑制的不够”这句话怎么理解呢?这里就得从负反馈系统说起了。

负反馈系统:

3. PLL的调试常见问题

参考:ADI的“CLOCK 常见问题解答”和维基百科内容

890

890

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?