前言

在前面的学习中,我们已经学会了使用Vivado及SDK开发环境,熟悉了硬件开发与Linux软件驱动之间的联系及开发流程。本系列教程我们学习SDSoc的开发,在SDSoc IDE中,Xilinx为我们集成了比较流行的开发板硬件平台,如果我们使用的是其中的一个,可以直接使用。但笔者使用的是米尔科技的7z010开发板,在开发之前首先要定义我们自己的硬件平台,作为之后创建应用的模板工程。

一个SDSoc Platform工程应该包含如下文件:

- 硬件支撑文件(DSA):A device support archive,DSA/HDF

- SDSoc创建的配置文件

- 软件文件:

- 目标操作系统:Linux,文件系统

- 启动文件:u-boot.elf,fsbl.elf

- [可选]库文件

- XML描述文件,描述硬件和软件结构

下图描述了这些文件的结构关系:

本例程的目的如下:

1. 创建硬件组件:硬件平台的的设备支撑架构DSA;

2. 创建平台的软件组件:

i.Fisrt Stage Boot Loader(FSBL)

ii."Hello World"可执行文件测试

iii.链接脚本,定义堆栈和内存

iv.启动文件BOOT.bin

3. 创建SDSoC平台

i. 使用SDx IDE创建用户自定义平台

ii. 在自定义的平台上运行硬件加速程序

硬件和软件环境:

软件:Windows 10 64bit, SDSoC2018.2

硬件:Zturn Board开发板(XC7z010), FAT32 SD card, mini USB数据线

一、创建硬件组件

使用Vivado创建开发板的基础硬件平台,这个操作流程在ZYNQ学习之路1.Linux系统从零开始建立.note中有详细的描述,或查看Vivado Design Suite User Guide,本文直接使用其创建好的模板工程。

模板工程的原理图如下图:

注意两个名称:ZYNQ重命名ps7, proc_sys_reset_0为系统复位模块,这两个名词在Tcl命令中将会用到。

1.1 添加必要的IP

设置ZYNQ Processing System,双击ZYNQ IP,

在PS-PL Configuration中

展开AXI Non Secure Enablement->GP Master AXI Interface

不勾选 M AXI GP0 interface

在Interrupts中,勾选Fabric Interrupts,展开,PS-PS Interrupt Ports,勾选IRQ_F2P[15:0].

复制Processor System Reset IP,一共需要使用四个。

添加Clocking Wizard IP

添加Concat IP

删除掉不需要用到的IO端口:删除GPIO,I2C, UART1等外设。

最后的原理图如下:

1.2 使用Tcl命令创建硬件平台

在之前创建的Vivado模板工程的基础上打包硬件的DSA文件,打开Vivado模板工程,在Tcl命令中进行以下操作。

1.2.1 定义硬件平台的名称和描述

创建一个硬件平台文件

sdsoc::create_pfm <platform>.hpfm参数:<platform> 用户设定的平台的名称

返回:新硬件平台的句柄

设置硬件平台的名称和描述:

sdsoc::pfm_name <platform handle> <vendor> <library> <platform> <version>

sdsoc::pfm_description <platform handle> "<Description>"本例程创建的平台命令如下:

set pfm [sdsoc::create_pfm zturnTemplate.hpfm]

sdsoc::pfm_name $pfm "BIAC" "ZturnTemplate" "ZturnTemplate" "1.0"

sdsoc::pfm_description $pfm "Zturn board SDSoc Template"1.2.2 声名时钟

在每个硬件平台文件中必须定义至少一个时钟,并且设定一个默认时钟(is_default=true)

sdsoc::pfm_clock <pfm_handle> <port> <instance> <id> <is_default> <proc_sys_reset>参数:

| 参数 | 描述 |

| pfm_handle | platform句柄 |

| port | 时钟名 |

| instance | 包含时钟的实例名 |

| id | 时钟的编号,用户自定义 |

| is_default | true:默认时钟,false:其他 |

| proc_sys_reset | 与系统的同步复位时钟一致 |

本例程设置时钟命令如下:

sdsoc::pfm_clock $pfm FCLK_CLK0 ps7 0 true proc_sys_reset_01.2.3 定义AXI端口

sdsoc::pfm_axi_port <pfm> <axi_port> <instance> <memport>参数:

| 参数 | 描述 |

| pfm | pfm句柄 |

| port | AXI端口 |

| instance | 包含该端口的模块名 |

| memport | 内存端口类型: M_AXI_GP: 通用AXI主机接口 S_AXI_HP: 高性能AXI从机接口 S_AXI_ACP:加速一致性从机端口 MIG:从机AXI连接到MIG内存控制器 |

本例程设置AXI端口命令如下:

sdsoc::pfm_axi_port $pfm M_AXI_GP0 ps7 M_AXI_GP1.2.4 定义中断端口

硬件平台必须有Concat模块连接中断端PS7,定义中断方法如下:

sdsoc::pfm_irq <pfm> <port> <instance>| 参数 | 描述 |

| pfm | pfm句柄 |

| port | irq端口名 |

| instance | cancat模块的名字 |

本例程定义中断端口命令如下:

for{set i 0} {$i<16} {incr i}{

sdsoc::pfm_irq $pfm In$i xlconcat_0

}1.2.5 打包文件

在使用上述命令描述了硬件平台之后,使用如下命令写入一个描述文件中:

sdsoc::generate_hw_pfm $pfm完整的命令如下:

set pfm [sdsoc::create_pfm zturnTemplate.hpfm]

sdsoc::pfm_name $pfm "BIAC" "ZturnTemplate" "ZturnTemplate" "1.0"

sdsoc::pfm_description $pfm "Zturn board SDSoc Template"

sdsoc::pfm_clock $pfm FCLK_CLK0 ps7 0 true proc_sys_reset_0

sdsoc::pfm_axi_port $pfm M_AXI_GP0 ps7 M_AXI_GP

for{set i 0} {$i<16} {incr i}{ sdsoc::pfm_irq $pfm In$i xlconcat_0 }

sdsoc::generate_hw_pfm $pfm

//设置dsa的属性

set name [get_property NAME [current_project]]

set_property dsa.vendor "xilinx.com" [current_project]

set_property dsa.board_id $name [current_project]

set_property dsa.name $name [current_project]

set_property dsa.version "1.0" [current_project]

write_dsa -force -include_bit F:/ZYNQ/ZturnTemplate/ZturnTemplate.dsa1.3 使用窗口设置PFM

使用命令行对于初学者来说不是很方便,SDSoC另外提供了图形界面的操作。

1.3.1 使能Platform Interfaces Tab

点击Window->Platform Interfaces.

这里将显示所有可用的接口,右键点击一个接口或一组选择的接口,选择"Enable",灰色的图标将变成深蓝色,只有使能的接口才能在SDx软件中使用。

1.3.2 设置平台的名称

点击Sources选项卡,选中Design Sources中的框图设计文件,在下方的文件属性窗口中,设置PFM_NAME的属性:点击灰色的铅笔图标,设置Vendor, Library, Name, and Version.设置后如下图所示:

1.3.3 设置主时钟

前文讲到,一个DSA文件中必须有一个默认时钟作为主时钟。在Platform Interfaces选项窗口中选择clk_wiz_0。

在下方的属性窗口中选择Options面板,勾选is_default属性

默认的clk_out1,clk_out2,clk_out3,clk_out4的id依次为1,2,3,4,将其依次修改为0,1,2,3,注意手动输入数字并按回车确定。

1.3.4 定义AXI端口

在Platforms Interfaces窗口中选择ps7端口,除了FCLK_CLK0,选择其他的M_AXI_GP0,M_AXI_GP1,S_AXI_ACP,S_AXI_HP0,S_AXI_HP1,S_AXI_HP2,S_AXI_HP3,选择使能。

1.3.5 定义中断端口

在Platforms Interfaces窗口中选择In0到In15端口,在下方的属性窗口中勾选Enabled。

1.3.6 写入DSA文件

在block design文件上右键选择Generate Output Products...,然后生成。

编译综合,生成比特流文件,导出文件。

在设置完PFM的属性后可以将其写入DSA文件。在Tcl Console窗口中操作:

set name [get_property NAME [current_project]]

set_property dsa.vendor "BIAC" [current_project]

set_property dsa.board_id $name [current_project]

set_property dsa.name $name [current_project]

set_property dsa.version "1.0" [current_project]

write_dsa -force -include_bit F:/ZYNQ/ZturnTemplate/ZturnTemplate.dsa如果没有问题,在工程目录下会生成ZturnTemplate.dsa文件。

注意:DSA文件的名称要与Vivado工程的名称一致。

二、 创建软件组件

本小节创建SDSoC平台的软件组件,包括以下三类软件。

- First Stage Boot Loader(FSBL):FSBL是初始化PS的,配置PL前的引导程序。

- Linker Script: 链接脚本定义代码段和数据段的内存地址,可执行文件elf需要使用链接脚本指定堆栈的地址和大小。

- Boot Image Format(BIF)File: BOOT.bin文件描述了Zynq-7000启动文件的组织结构

2.1 创建Application工程

打开SDx软件,点击File->New->SDx Project...,选择创建Application工程。

输入工程名:Helloworld,点击Next >

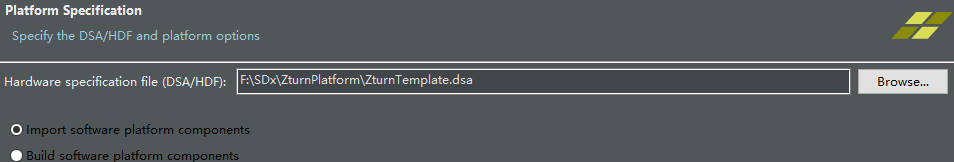

在平台类型选择窗口,选择Hardware specification(DSA/HDF)

点击Add New DSA/HDF...,选择第一节中生成的DSA文件。新的平台将加入到列表中。选中自定义的平台,点Next,在系统配置界面配置如下:

- OS Platform:standalone

- Processor:ps7_cortexa9_0

- Language:C

在工程模板中选择Hello World,点Finish完成工程的创建。

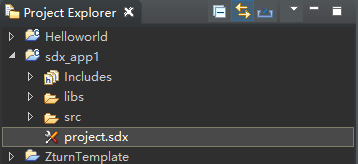

此时,在工程导航窗口中将创建Helloworld应用和平台的模板工程。

双击project.sdx,在Helloworld面板中,点击Modify BSP Settings...

选择standalone,将stdin和stdout设置为ps7_uart_1.

在Assistant窗口中,右键单击Helloworld应用,选择Generate Linker Script。

在右侧Basic处修改堆栈的大小,默认值对于SDx应用程序来说太小。

设置Heap Size:805306368(768MB); Stack Size:262144(256KB)

在Assistant中展开Helloworld,右键点击Debug,选择Build,编译这个工程。

arm-none-eabi-size Helloworld.elf |tee "Helloworld.elf.size"

text data bss dec hex filename

19352 1144 805574696 805595192 30046838 Helloworld.elf

'Finished building: Helloworld.elf.size'编译完成后,在Debug目录中将生成Helloworld.elf文件。

2.2 制作启动文件

现在,我们已经有了硬件和软件组件,我们可以用它们来启动Zyqn-7000 SoC了。SDx IDE提供了创建启动文件的功能。

在Assistant窗口,右键点击Helloworld[Application],选择Create Boot Image

i. 选择Zynq Architecture

ii. 选择Create new BIF file

iii. 默认Output BIF file path,不修改

iv. 输出路径:默认值不修改

V. 添加boot image的各个部分: fsbl.elf, ZturnTemplate.bit, HelloWorld.elf

其中,fsbl.elf由vivado中的SDK创建。

点击Create Image创建BOOT.bin文件,该文件在工程目录下的_sdx/bootimage目录中。

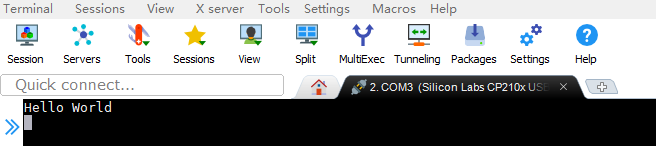

2.3 启动Zynq

复制BOOT.bin文件到FAT32格式的SD卡根目录下。

将SD卡插入Zturn Board,连接USB数据线,根据串口号打开串口终端。

上电启动开发板,在窗口终端中将打印如下字符。

2.4 准备一个分级区

现在我们已经完成了所有组件的设计,可以用来创建一个裸机SDSoC平台的应用程序。为了之后的平台工程创建,我们将其打包成具有分级结构的文件。

a. 切换到SDx的workspace

b. 复制DSA文件

c. 创建boot目录

d. 进入boot目录

e. 复制fsbl.elf文件到boot目录

f. 复制Helloworld链接文件到boot目录

g. 复制Helloworld.bif文件到boot目录

h. 复制BOOT.bin文件到boot目录

以ZturnPlatform为父目录则目录结构如下

ZturnPlatform

|--ZturnTemplate.dsa

|boot

|--fsbl.elf

|--lscript.ld

|--Helloworld.bif

|--BOOT.bin复制Helloworld.bif文件,重命名为platform.bif,编辑内容如下:

//arch = zynq; split = false; format = BIN

the_ROM_image:

{

[bootloader]<fsbl.elf>

<bitstream>

<elf>

}三、创建一个用户定义的平台

前面两节已经准备好了硬件组件和软件组件,并且使用裸机程序简单的测试了系统的正确性。

3.1 创建一个用户定义的平台工程

点击菜单File->New->New SDx Project...,选择Platform

点击Next >之后选择之前创建的平台。

点击Next,选择前面ZturnPlatform目录中的ZturnTemplate.dsa文件。点Finish完成。

创建的工程名自动命名为DSA文件的名称!

3.2 定义平台文件

创建完平台工程后,显示的窗口提示了四个设置步骤。

i. 点击(1)Define System Configuration

输入Name: standalone,Display Name自动填充与之一致。

选择性输入描述语言

选择前面的boot文件夹

选择platform.bif文件。

ii.点击(2)Add Processor Group/Domain

输入Name:a9_standalone,Display Name自动填充为与之一致

OS:standalone

Processor: ps7_cortexa9_0

Supported Runtimes:C/C++

Linker Script:lscript.ld

iii. 点击(3)Generate Platform

iv. 点击(4)Add to Custom Respositories

此时在Assistant窗口将添加ZturnTemplate[Platform]

3.3 使用自定义的SDx平台创建应用

在SDx IDE的菜单中选择File->New->SDx Project,选择Application类型。

工程名输入sdx_app1,在Platform中选择上面添加的ZturnTemplate[custom]

点击Next,使用默认的设置。

点击Next,选择mmult_pipeline为模板创建FPGA加速的应用程序。

点击Finish完成应用的创建。

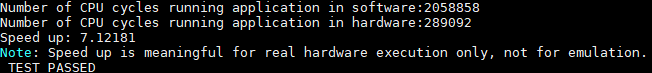

在Assistant窗口中,选择sdx_app1,在Debug上右键选择Build.

编译完成后在Debug目录中将生产SD卡镜像文件,sd_card目录中是启动文件。

启动运行之后在终端窗口中显示如下:

错误:可能出现的错误:ERROR: [DMAnalysis 83-4503] No M_AXI_GP port found in the platform!这是由于FPM_NAME与DSA文件名不一致导致的,在开始做这个实验室,笔者的PFM_NAME=xilinx.com:zturn:zturnTemplate:1.0,DSA文件名为ZturnTemplate.dsa,因此要将DSA文件重命名为zturnTemplate.dsa.

错误:可能出现的错误:No suitable system port available for XFER(IN)\nin1 @102\nARRAY\n,在ZYNQ IP和设置时不要勾选GP0端口

错误:可能出现的错误:ERROR: [VPL 17-69] Command failed: Invalid constraints filename specified。这里会有一个警告:id 0不存在,vivado默认设置clk_out1为1开始,将其修改为0开始。

四 总结

第一节介绍了使用vivado创建硬件设计,添加硬件加速必备的IP核,ZYNQ, Reset, Concat以及ZYNQ核需要设置的外设,取消AXI外设,打开中断,设置时钟等。然后使用Tcl命令创建SDSoC所需要的DSA文件。

第二节介绍了如何使用SDx IDE创建硬件平台和硬件加速的应用程序,第三节使用硬件平台创建了一个硬件加速应用验证了平台设计的正确性。

由于开发板所使用的芯片不一样,可能按照官方的例程来操作会出现一些错误,根据错误消息,在xilinx社区基本都能找到解决方法。

参考资料

[1] Xilinx官方文档ug1146

[2] SDSoC tutorials

[3] PFM属性设置

1840

1840

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?