本文描述了如何使用Xilinx的Vivado Design Suite环境中的工具来定制和生成 Processor System Reset IP 核。Vivado Design Suite是一个强大的FPGA设计和开发环境,它允许用户定制和配置各种IP核以适应他们的特定设计需求。

以下是针对如何定制IP核的步骤的简要概述:

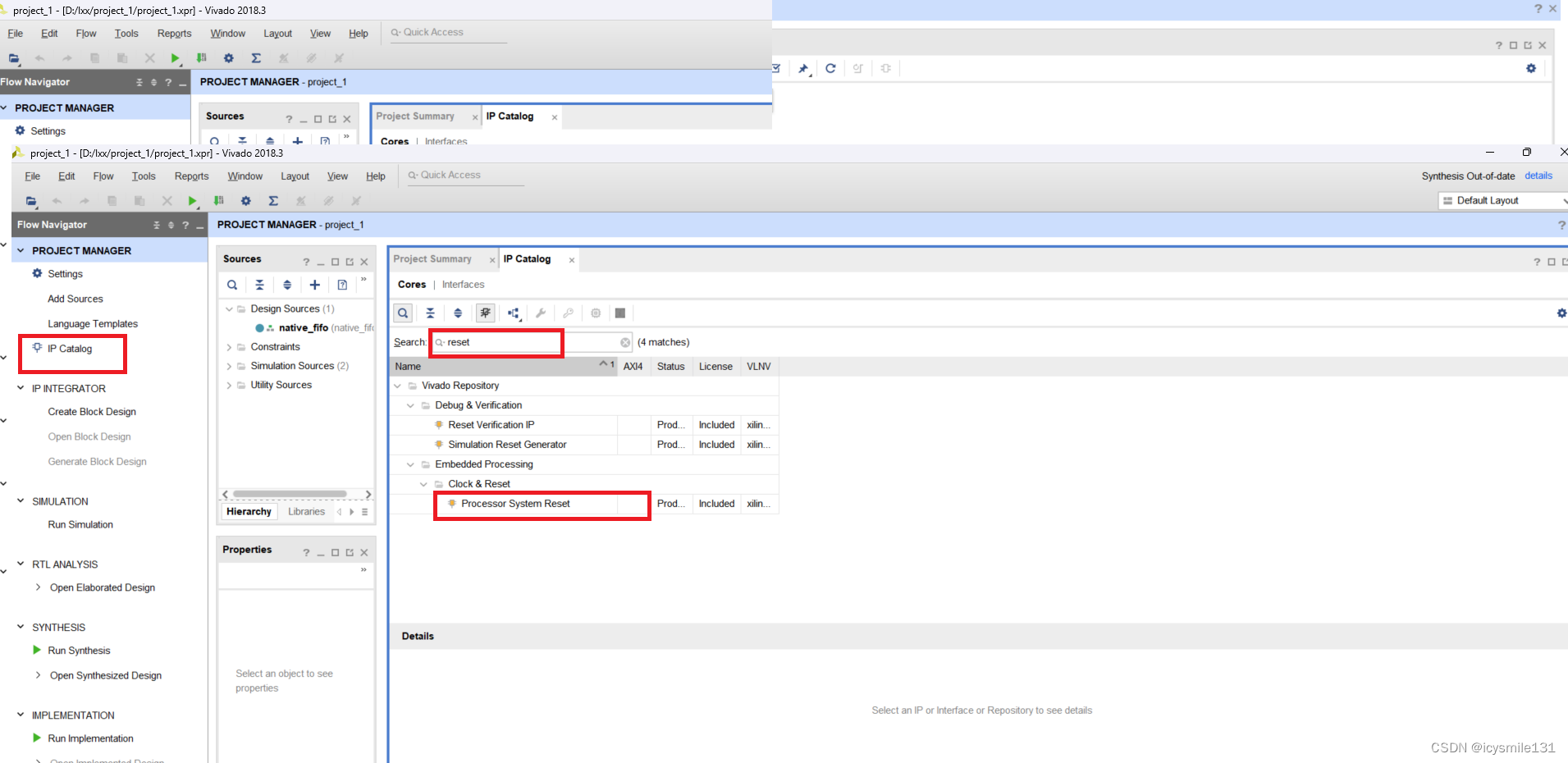

1. 从IP Catalog中选择IP。

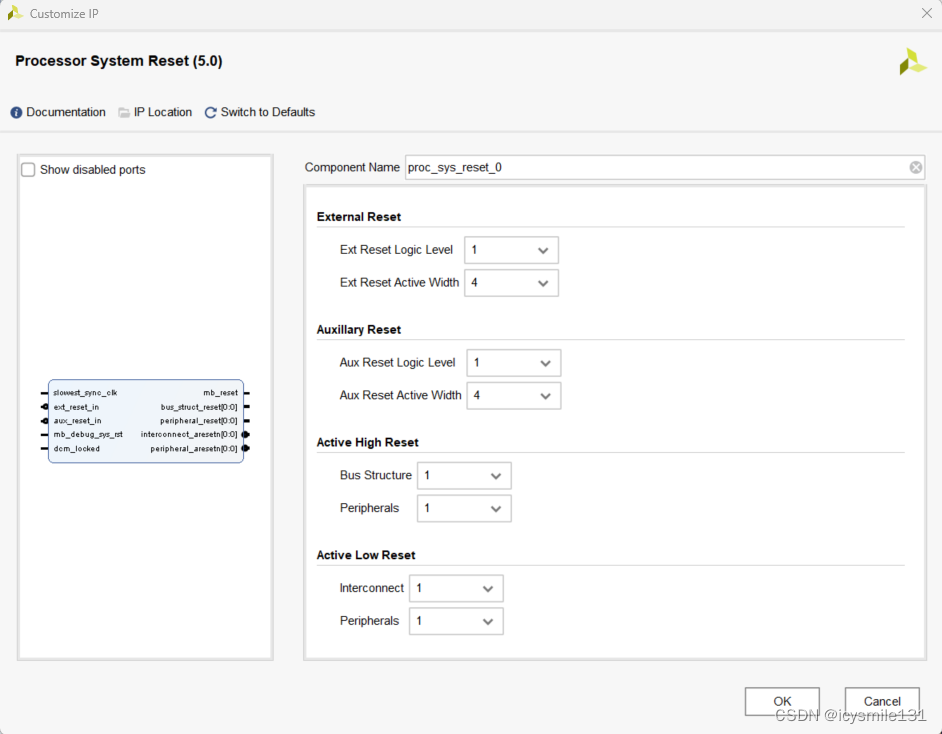

2. 定制IP核

双击选择的IP核,或者从工具栏或右键菜单中选择“Customize IP”命令,打开IP核,开始设置与IP核相关的各种参数值。

在Xilinx的Vivado Design Suite中,Processor System Reset IP 核的参数通常被分为几个类别,以便用户根据设计需求进行定制。

(1)External Reset(外部重置)

External Reset Logic Level(外部重置逻辑电平)

用于确定外部重置引脚是低电平有效(active-Low)还是高电平有效(active-High)。在数字逻辑中,一个信号可以是低电平有效(当信号为0时表示有效)或高电平有效(当信号为1时表示有效)。

External Reset Active Width(外部重置有效宽度)

用于确保如果外部重置引脚在选定的持续时间内保持激活状态,它将被视为一个有效的重置,并且核心将生成其他重置引脚。这可以防止由于瞬态噪声或短暂的脉冲信号导致的误重置。通过设置适当的宽度,可以确保只有持续时间足够长的重置信号才会触发重置操作。

(2)Auxiliary Reset(辅助重置)

Auxiliary Reset Logic Level(辅助重置逻辑电平)

与外部重置逻辑电平类似,但它针对的是辅助重置引脚。可以选择辅助重置引脚是低电平有效还是高电平有效,具体取决于硬件设计和需求。

Auxiliary Reset Active Width(辅助重置有效宽度)

确保如果辅助重置引脚在选定的持续时间内保持激活状态,它将被视为一个有效的重置,并且Processor System Reset IP 核将生成其他重置引脚。这与外部重置有效宽度的功能相似,但应用于辅助重置引脚。

(3) Active High Reset(高电平有效复位)

Bus Structure Reset(总线结构复位)

指的是为总线接口生成的复位次数。复位信号在高电平时有效,也就是说,当复位信号处于高电平时,总线接口会进行复位操作。

Peripherals(外设)

指的是为外设生成的复位次数。同样,复位信号在高电平时有效,外设会在接收到高电平的复位信号时进行复位。

(4)Active Low Reset(低电平有效复位)

Interconnect(互联接口)

指的是为互联接口生成的复位次数。复位信号在低电平时有效,也就是说,当复位信号处于低电平时,互联接口会进行复位操作。

Pripherals(外设)

指的是为外设生成的复位次数。复位信号在低电平时有效,外设会在接收到低电平的复位信号时进行复位。

在硬件设计中,复位信号的有效电平(高电平或低电平)是由具体的硬件设计、接口标准和协议决定的。例如,某些微处理器或外设可能要求使用高电平复位,而其他则可能使用低电平复位。

3852

3852

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?