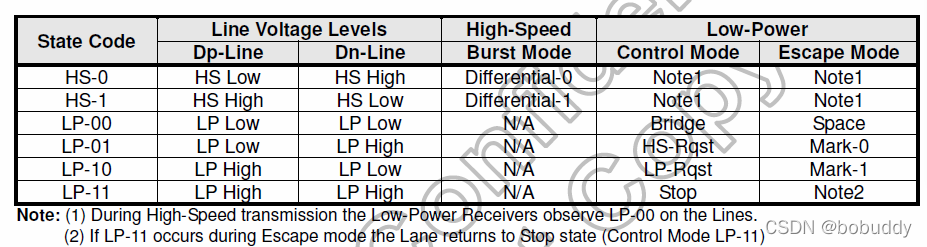

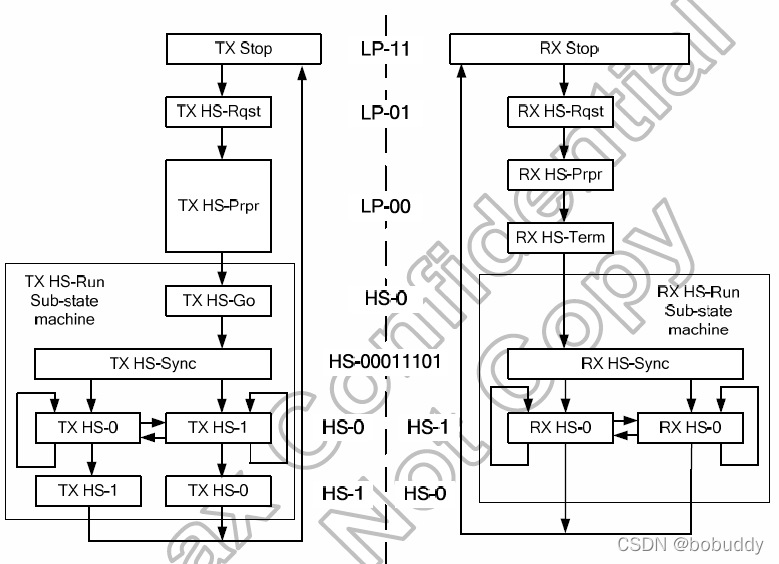

HS : high speed

Lp : Low power

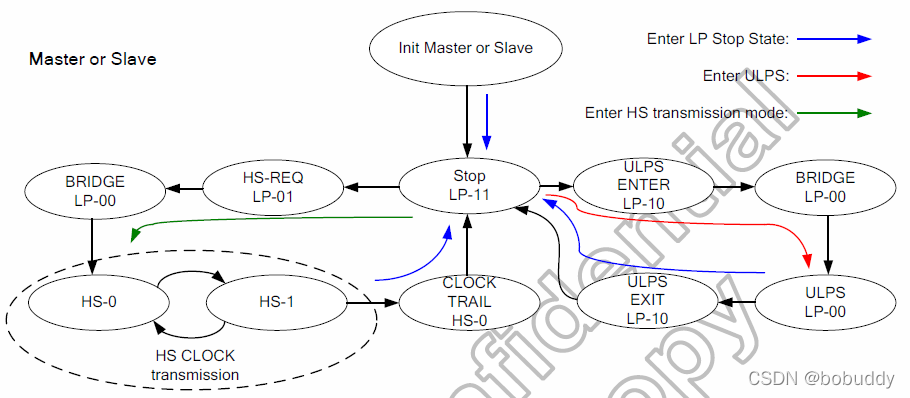

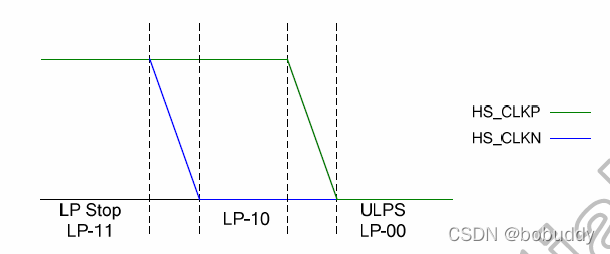

Clock lane mode

Clock Lane can be driven LP-11 to enter Low Power Stop State. There are three

ways to enter Lower Power Stop State:

(1) After Initial state. (HW reset, SW reset, Power on sequence)

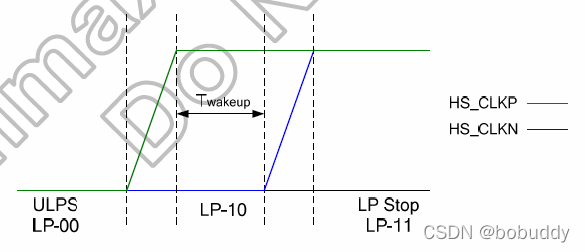

(2) Leaving ULPS: ULPS LP-00 -> LP-10 -> Low Power Stop State LP-11.

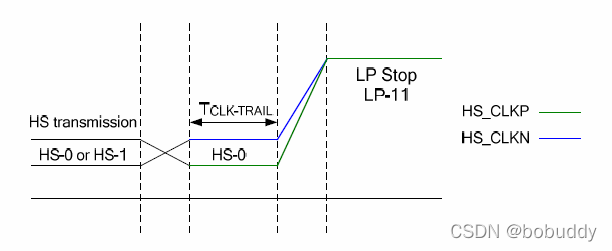

(3) Leaving HS clock transmission mode: HS mode (HS-0 or HS-1) -> H

Clock Lane can be driven LP-00 to enter Ultra Low Power State from Low Power

Stop State. The flow is Low Power Stop State LP-11 -> LP-10 -> ULPS LP-00.

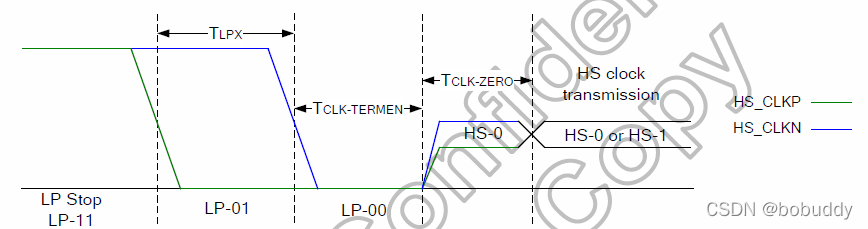

Clock Lane can be High Speed Clock transmission State from Low Power Stop State.

The flow is Low Power Stop State LP-11 -> LP-01 -> LP-00 -> HS-0/1.

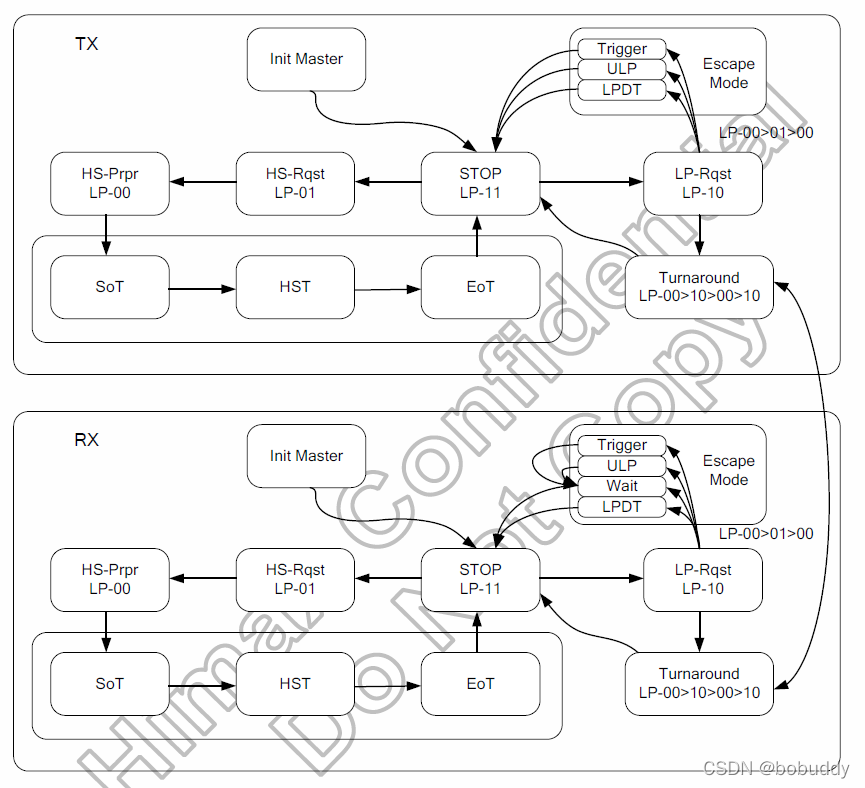

data lane mode

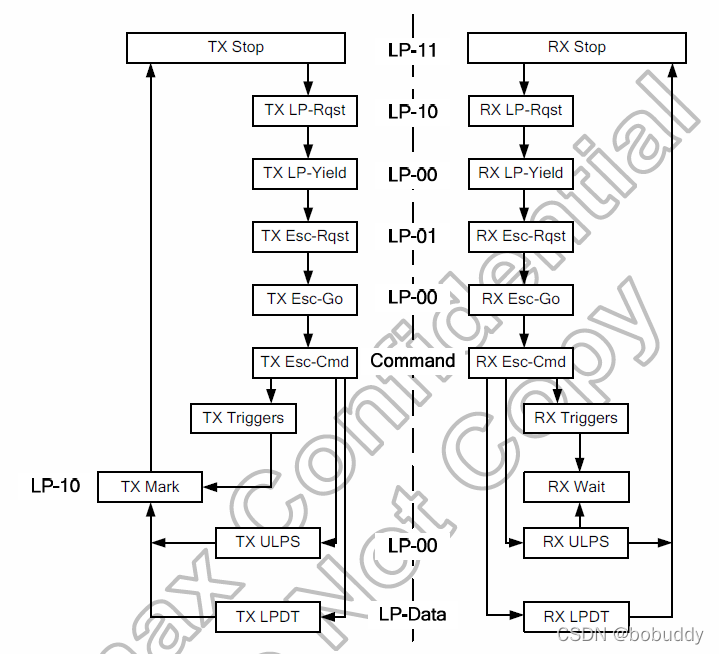

Escape mode

Data Lane0 is used in Escape Mode when data lane in LP mode. Data Lane shall

enter Escape mode via LP-11 -> LP-10 -> LP-00 -> LP-01 -> LP-00 and exit Escape

mode via LP-10 -> LP-11.

High speed data transmission

Data Lane enter High Speed Data

Transmission flow: LP-11 -> LP-01 -> LP-00 -> SoT (0001_1101).

5万+

5万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?