LVDS(Low Voltage Differential Signaling):低电压差分信号。

这种技术采用极低的电压摆幅(约350mV)通过一对差分PCB走线或平衡电缆传输高速的差动数据。LVDS的传输距离推荐的最高数据传输速率是655Mbps,而理论上可以达到1.923Gbps。由于电压信号幅度较低,而且采用恒流源模式驱动,故只产生极低的噪声,消耗非常小的功率,甚至不论频率高低功耗都几乎不变。此外,由于LVDS以差分方式传送数据,所以不易受共模噪音影响,属于平衡传输信号。

一、LVDS传输原理

1.LVDS基本原理

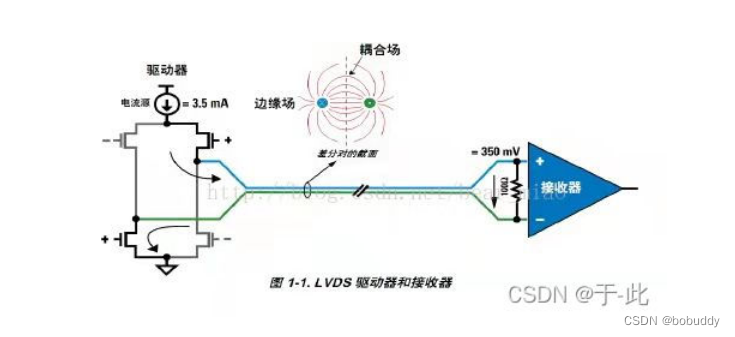

LVDS的基本工作原理图示于图1。其源端驱动器由一个3.5mA的恒流源驱动一对差分信号线组成。接收端的接收器为高输入阻抗,所以几乎全部的驱动电流都流经100Ω的终端匹配电阻,并在接收器输入端产生约350mV的电压。当源端驱动状态反转变化时,流经匹配电阻的电流方向改变,于是在接收端产生高低逻辑状态的变化。即输出直流偏置为1.2V,输出差分摆幅为-350mV—+350mV。

2.LVDS信号传输组成

1.差分信号发送器:内部由3.5mA的恒流源驱动,将非平衡传输的TTL 信号转换成平衡传输的LVDS 信号。

2.差分信号互联器:PCB 走线或者传输电缆,为了保证信号传输的质量差分互联器一般要求100Ω的传输阻抗(若阻抗不匹配可能会引起信号的反射等,影响信号传输质量)。

3.差分信号接收器:高阻抗输入,差分信号接收器按照IEEE 规定要求接100Ω的终端匹配电阻,若接收芯片内部有终端电阻可以选择不接,若接受芯片内部没有则需要接100Ω电阻。由于发送端输出为3.5mA的电流源,则在接收端产生3.5mA×100Ω=350mV的电平。再由接收端将平衡传输的LVDS 信号转换成非平衡传输的TTL 信号进行处理。

为适应共模电压的在宽范围内的变化,一般情况下,LVDS的接收器输入级还包括一个自动电平调整电路,该电路将共模电压调整为一固定值,其后面是一个Schmitt触发器,而且,为防止Scdhmitt触发器不稳定,设计有一定的回滞特性,Schmitt后级才是差分放大器。

二、LVDS电平标准

1.LVDS发送端电平标准

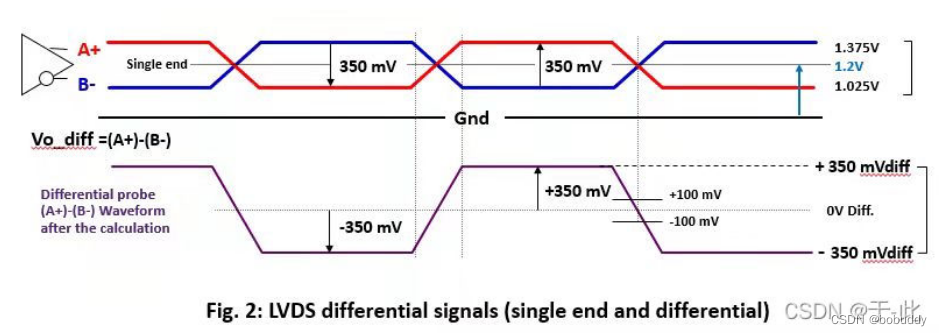

图二:为LVDS数据传输的电平标准

LVDS的输出直流偏置为1.2V(LVDS的P\N相对于地的电压)。

输出交流摆幅为-350mV—+350mV(LVDS的P\N之间的电压)。

2.LVDS接收端电平标准

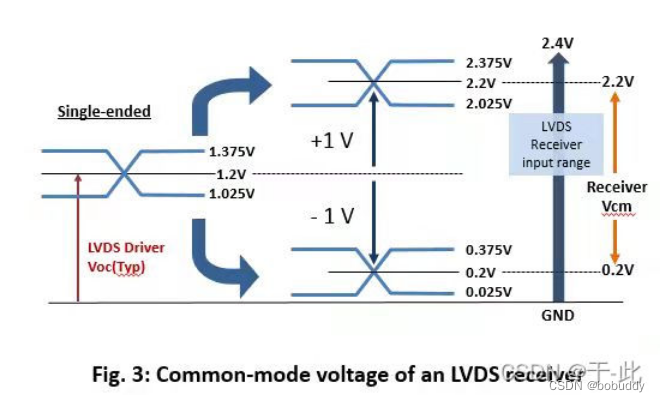

图三:为LVDS数据接收的电平标准

由上图可知,为了减少信号传输过程中共模电压的变化对接受端器件的影响和损坏。LVDS接收器可以承受至少±1V的驱动器与接收器之间的共模电压的变化。LVDS驱动器典型的偏置电压为+1.2V,由于地的电压变化、驱动器偏置电压以及轻度耦合到的噪声之和,都会引起接收器的输入端的偏置电压引起变化。即接收端偏置电压(共模电压)范围应在0.2V到2.2V之间。

三、LVDS的特点

1.高速传输能力。在ANS/EIA/EIA-64定义中的LVDS标准,理论极限速率为1.923Gbps,推荐的最高数据传输速率是655Mbps,恒流源模式(3.5mA)、低摆幅(±350mA)输出的工作模式决定着IVDS具有高速驱动能力。

2.低功耗特性。LVDS器件是用CMOS工艺实现的,而CMOS能够提供较低的静态功耗;当恒流源的驱动电流为3.5mA,负载(100Ω终端匹配)的功耗仅为1.225mW;LVDS的功耗是恒定的,不像CMOS收发器的动态功耗那样相对频率而上升。恒流源模式的驱动设计降低了系统功耗,并极大地降低了频率成分对功耗的影响。虽然当速率较低时,CMOS的功耗比LVDS小,但是随着频率的提高,CMOS的功耗将逐渐增加,最终需要消耗比LVDS更多的功率。通常,当频率等于200MSps时,LVDS和CMOS的功耗大致相同。

3.供电电压低。随着集成电路的发展和对更高数据速率的要求,低压供电成为急需。降低供电电压不仅减少了高密度集成电路的功率消耗,而且减少了芯片内部的散热压力,有助于提高集成度。LVDS的驱动器和接收器不依赖于特定的供电电压特性,这决定了它在这方面占据上峰。

4.较强的抗噪声能力。差分信号固有的优点就是噪声以共模的方式在一对差分线上耦合出现,并在接收器中相减,从而可消除噪声,所以LVDS具有较强的抗共模噪声能力。

5.有效地抑制电磁干扰。由于差分信号的极性相反,它们对外辐射的电磁场可以相互抵消,耦合得越紧密,泄放到外界的电磁能量就越少,即降低了EMI。

6.时序定位精确。由于差分信号的开关变化是位于两个信号的交点。而不像普通单端信号依靠高低两个阀值电压判断,因而受工艺,温度的影响小,能降低时序上的误差,有利于高速数字信号的有效传输。

7.适应地平面电压变化范围大。LVDS接收器可以承受至少士1V的驱动器与接收器之间的地的电压变化。由于IVDS驱动器典型的偏置电压为+1.2V,地的电压变化、驱动器的偏置电压以及轻度耦合到的噪声之和,在接收器的输入端,相对于驱动器的地是共模电压。当摆幅不超过400mV时,这个共模范围是+0.2V——+2.2V,一般情况下,接收器的输入电压范围可在0V~+2.4V内变化。

四、LVDS信号PCB设计

由LVDS的原理我们可以知道LVDS是低电压的差分高速信号,为了保证信号的完整性,减少信号的之间的串扰及反射等问题,我们在PCB布局布线的时候需要遵守一定的规则来保证信号完整可靠的传输。

1.差分信号走线的紧耦合原则。一般保证差分信号之间的距离小于或等于走线线宽的距离,提高差分信号的抗共模干扰的能力。

2.差分信号线走线尽量短和直。LVDS信号禁止90°走线,在拐弯处的地方尽量走弧线,减小信号的反射。尽量减少LVDS的过孔数量,在过孔旁尽量放置一个地过孔,增加信号的回流路径。

3.LVDS传输线需要做100Ω的阻抗匹配。若远距离传输传输线的阻抗不匹配就会引起信号的反射,引起信号的畸变,从而引起信号质量的降低。阻抗不匹配就如同水流(电流)流过不同大小的水管(传输线阻抗),由于水管大小不均,导致水流(电流)回流(反射)和产生的水流叠加。PCB阻抗计算可以利用软件SI9000来计算。

4.远离干扰源。LVDS走线的时候应该远离干扰源,尽量保证信号的完整的传输。一般走线距离大于3到5倍的差分间距。

5.保证信号的回流路径。及保证参考平面的完整性(电源和地),尽量在LVDS的相邻层放置一层GND,保证信号的回流路径最小,引起的干扰最小。一般高速信号的回流路径为阻抗最小原则,即高速信号的回流路径为信号的走线路径,使之产生的环路最小。低速信号的回流路径一般为电阻最小原则,即最小阻抗为回流最短距离。

6.终端电阻尽量靠近接收端。由于LVDS为电流型驱动,终端电阻放在接收端可以减少信号的衰减,若放在驱动端,则在传输线上传输的是电压信号,容易引起传输线的信号衰减,影响信号质量。

7.差分信号等长处理。一般差分信号为了保证数据传输的同步性,会在差分信号上做等长处理。在差分信号的蛇形走线时,尽量绕大弯,避免差分走线里的太近,减少耦合长度

1357

1357

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?