模块文件代码:

module decoder3_8(a,b,c,dout);

input a,b,c;

output [7:0] dout;

reg [7:0] dout;

always@(a,b,c)

begin

case( {a,b,c} )

3'b000: dout=8'b0000_0001;

3'b001: dout=8'b0000_0010;

3'b010: dout=8'b0000_0100;

3'b011: dout=8'b0000_1000;

3'b100: dout=8'b0001_0000;

3'b101: dout=8'b0010_0000;

3'b110: dout=8'b0100_0000;

3'b111: dout=8'b1000_0000;

endcase

end

endmodule testbench代码:

`timescale 1ns/1ns

module decoder3_8_tb;

reg signal_a,signal_b,signal_c;

wire [7:0] dout;

decoder3_8 u1

(

.a(signal_a),

.b(signal_b),

.c(signal_c),

.dout(dout)

);

initial

begin

signal_a=0;signal_b=0;signal_c=0;

#100;

signal_a=0;signal_b=0;signal_c=1;

#100;

signal_a=0;signal_b=1;signal_c=0;

#100;

signal_a=0;signal_b=1;signal_c=1;

#100;

signal_a=1;signal_b=0;signal_c=0;

#100;

signal_a=1;signal_b=0;signal_c=1;

#100;

signal_a=1;signal_b=1;signal_c=0;

#100;

signal_a=1;signal_b=1;signal_c=1;

#200;

$stop;

end

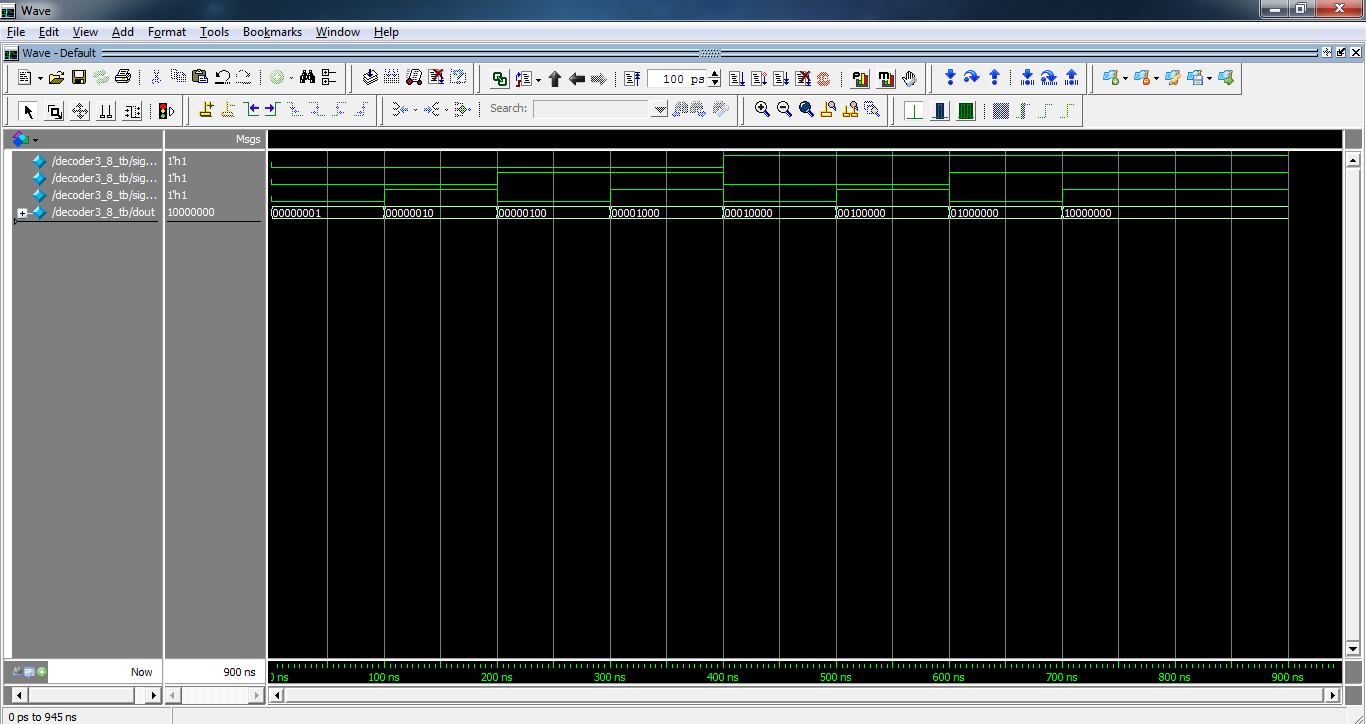

endmodule RTL仿真波形:

2730

2730

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?