本文中使用Zynq 7000系列中的xc7z035ffg676-2器件的100MHz PL侧的外部差分时钟来检测外部按键是否按下,当按键被按下时,对应的灯会被点亮。当松开按键时,对应的灯会熄灭。

1、编写代码

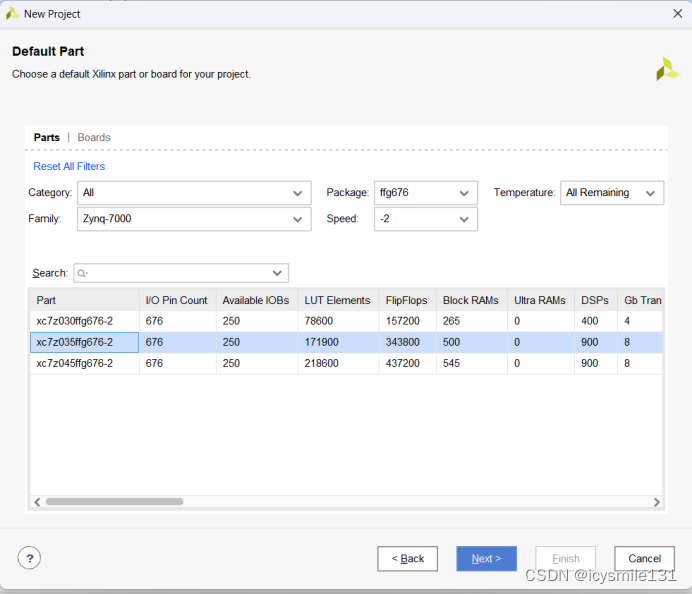

新建工程,选用xc7z035ffg676-2器件。

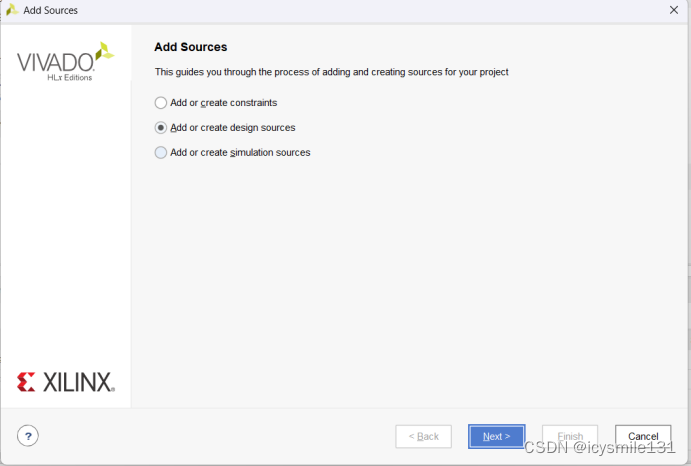

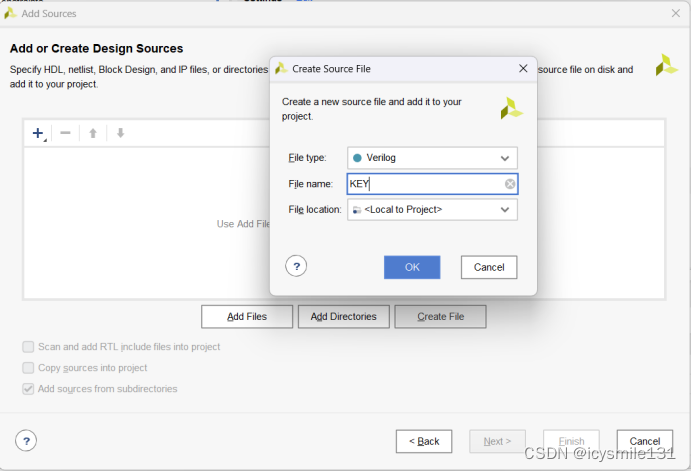

点击Design Sources中的“+”新建一个代码文件KEY.v。

文件类型选择Verilog。

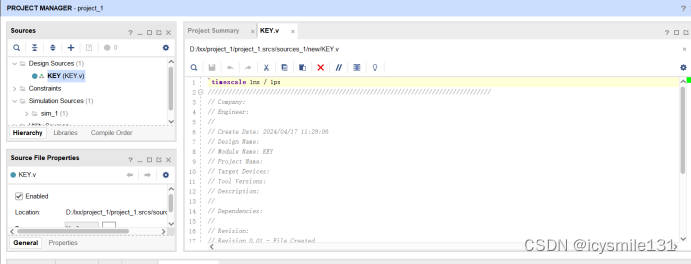

KEY.v文件创建完成后,可以看到Design Sources文件夹中有KEY.v文件,打开该文件编辑内容。

module KEY(

input clk,

input rst,

input key,

output led

);

parameter delay_time = 200;

reg [31:0] cnt;

reg led_r;

assign led = led_r;

always @(posedge clk or negedge rst)

begin

if(!rst) begin

cnt <= 'b0;

led_r <= 'b0;

end

else begin

if(!key) begin

if( cnt < delay_time) begin

cnt <= cnt + 'b1;

led_r <= led_r;

end

else begin

cnt <= cnt;

led_r <= 'b1;

end

end

else begin

cnt <= 'b0;

led_r <= 'b0;

end

end

end

endmodule

2、仿真设计

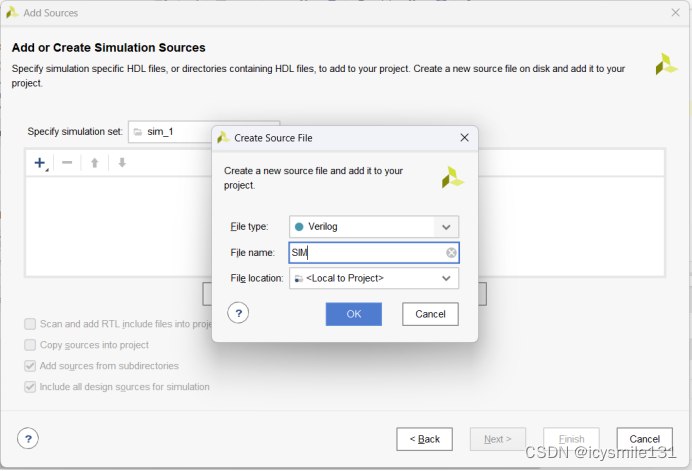

点击Design Sources中的“+”创建仿真文件SIM.v

文件类型选择Verilog。

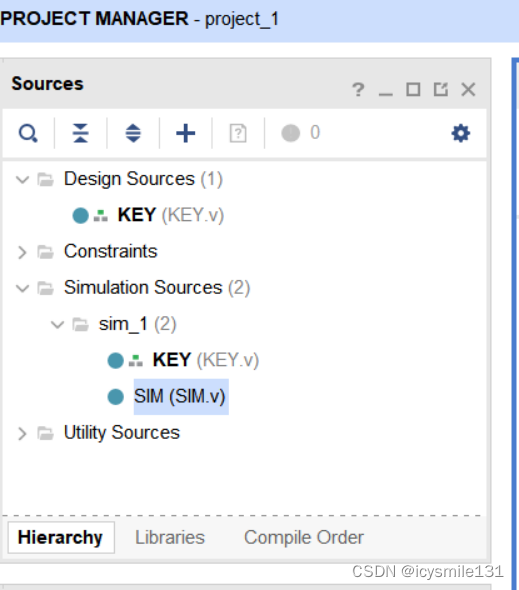

SIM.v文件创建完成后,可以看到Design Sources文件夹中有SIM.v文件,打开该文件编辑代码。

在这里,key = 1表示没有按按键,key = 0表示按下按键。

module SIM(

);

reg clk;

reg rst;

reg key;

wire led;

KEY KEY(

.clk(clk),

.rst(rst),

.key(key),

.led(led)

);

initial

begin

clk = 'b0;

rst = 'b0;

key = 'b1;

#1000;

rst = 'b1;

#20000;

key = 'b0;

#10000;

key = 'b1;

#20000;

key = 'b0;

end

always #5 clk = !clk;

endmodule

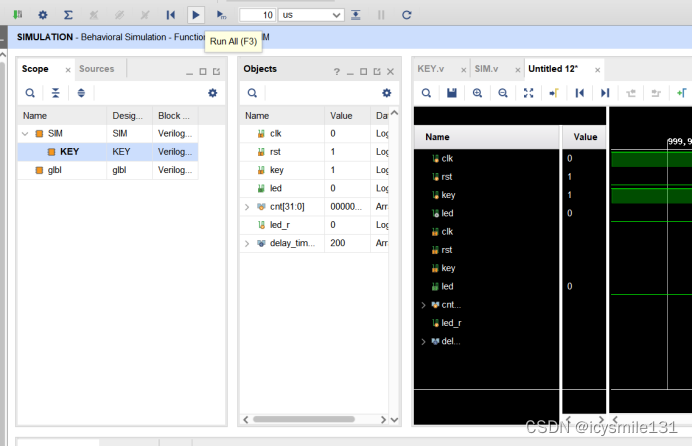

3、开始仿真

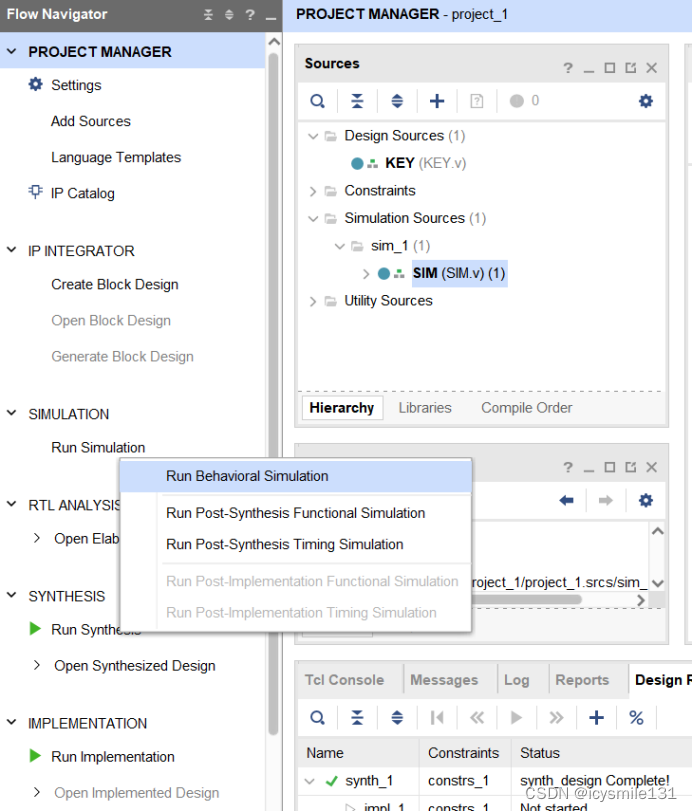

左键点击“PROJECT MANAGER——SIMULATION——RUN Simulation”。

选择Run Behavioral Simulation.

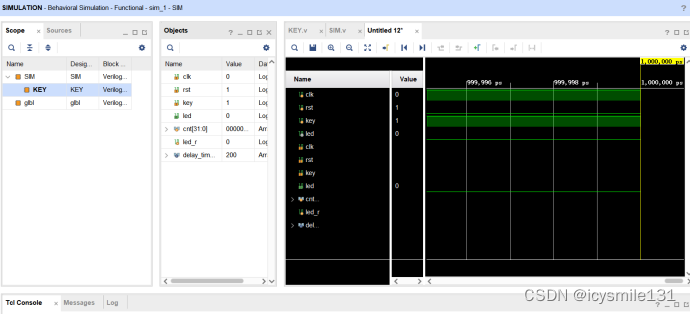

右键点击Scope下的KEY,选择Add to Wave Window,将KEY中的信号全部添加到右侧视图中。

点击Run All运行仿真。

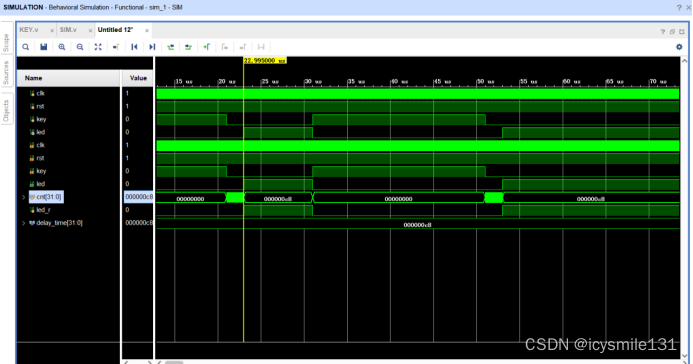

运行结果为:

9224

9224

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?