在线调试有多种方式,这里介绍一种快速入门的方式,添加lia核。ChipScope Pro集成逻辑分析(ILA)IP核是一个可定制的逻辑分析核,用于监视设计中的内部信号。通过在RTL设计中嵌入ILA核,可以抓取信号的实时波形,帮助我们定位问题。

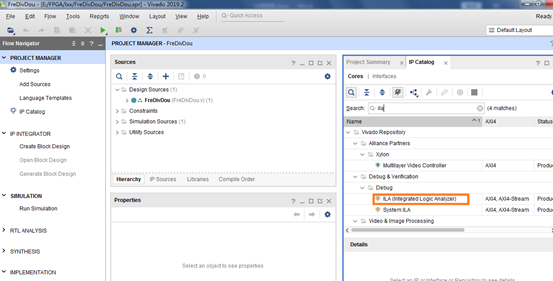

点击PROJECT MANAGER中的IP Catalog,

在IP Catalog的Search中输入ila,双击Debug &Verfication——Debug——ILA(Integrated Logic Analyzer),

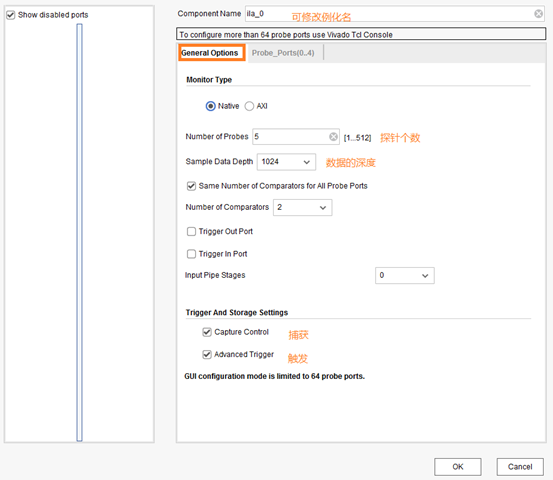

在General Option界面中,可以修改例化名称,也可以使用默认名称,修改探针的个数,勾选上Capture Control和Advanced Trigger,

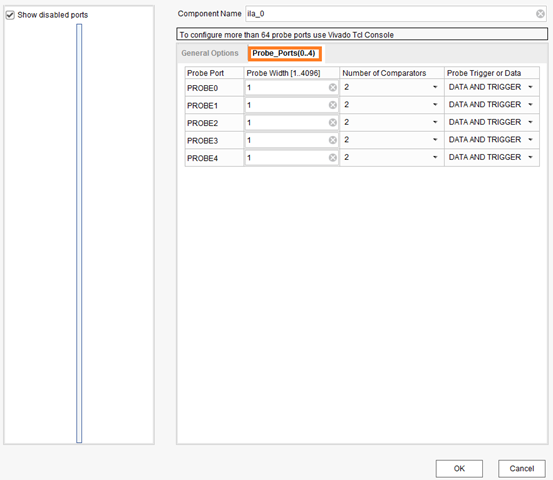

Probe_Ports(0..4)界面修改探针的宽度,点击OK,

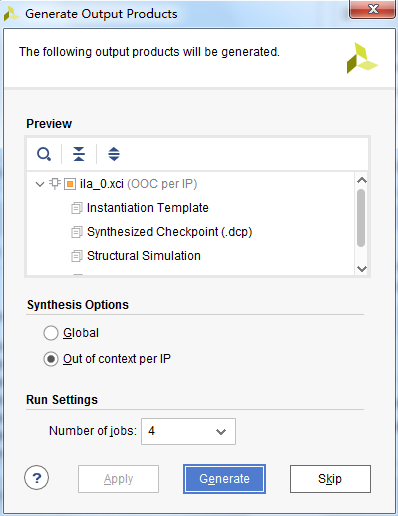

点击Generate,

本文介绍了如何在Vivado中使用ILA核进行FPGA设计的在线调试。通过添加ILA核,设置探针并连接到设计信号,可以在运行时捕获实时波形以定位问题。详细步骤包括ILA核的添加、配置、代码例化和调试过程,强调了ILA的时钟选择策略。

本文介绍了如何在Vivado中使用ILA核进行FPGA设计的在线调试。通过添加ILA核,设置探针并连接到设计信号,可以在运行时捕获实时波形以定位问题。详细步骤包括ILA核的添加、配置、代码例化和调试过程,强调了ILA的时钟选择策略。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1203

1203

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?