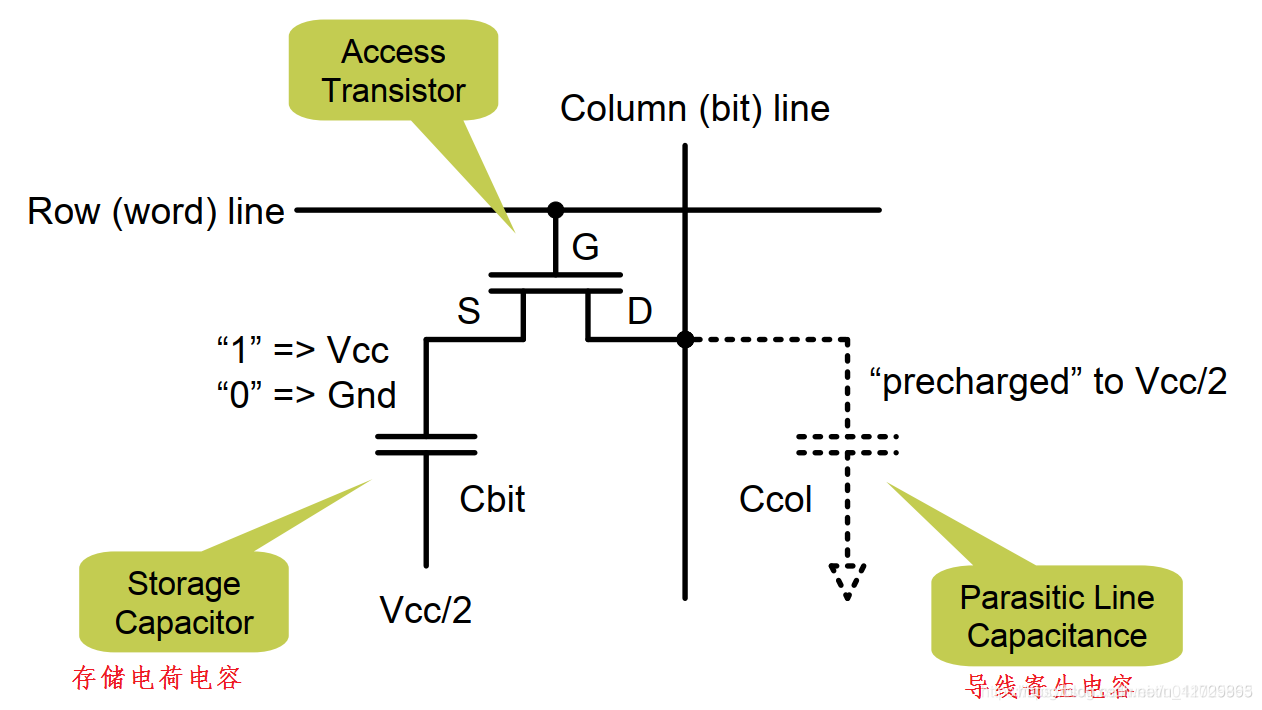

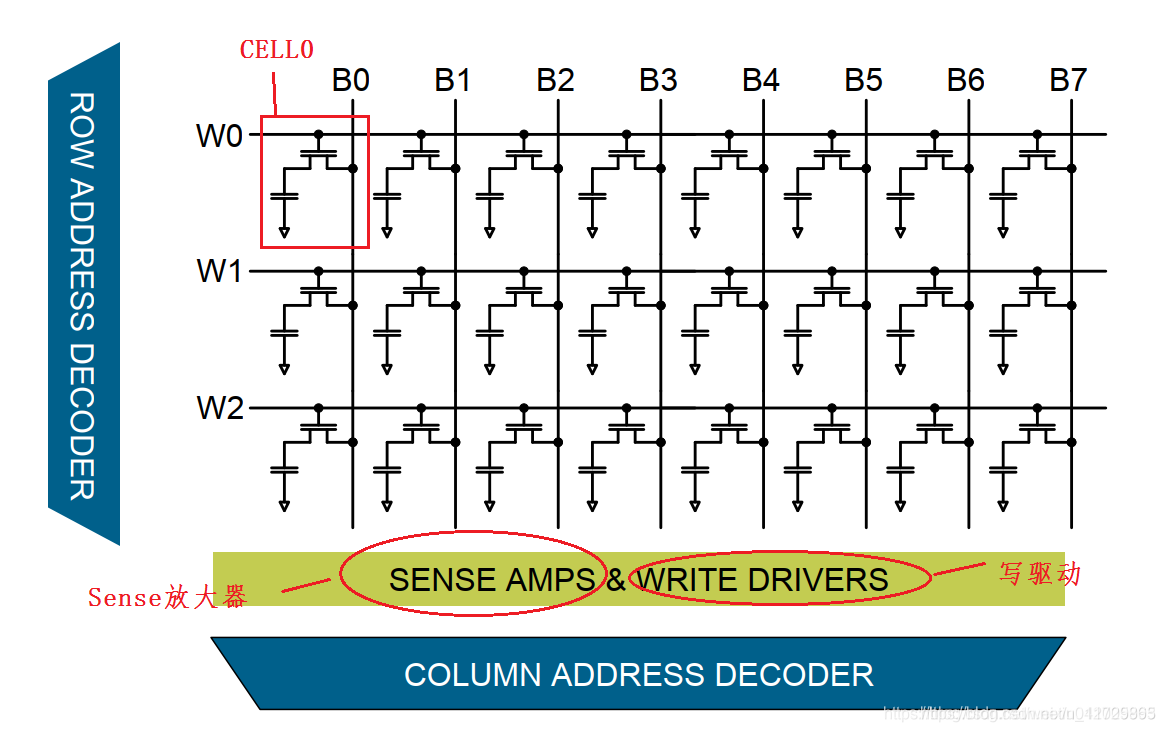

以上图Cell0为例子

读过程(包含预充电步骤)

- 首先关闭所有字线,W0,W1…Wn。让所有FET均不导通。

- 然后将位线B0通过预充电开关Precharge(图中未画出)拉到Vcc/2,即VB0=Vcc/2。(这个操作就是预充电Precharge)【读操作,位线,需要预充电至Vcc/2】

- 再断开预充电开关Precharge Switch,停止充电。

- 将W0置为高电平Vcc,此时Cell0的FET导通。

如果原来存储的是1,Cbit电压大于VB0,那么Cbit会对字线B0充电,使得VB0>Vcc/2,此时VB0经过放大器Sense AMP后放大电压到VCC电平,即读出1。

如果原来存储的是0,Cbit电压小于VB0,于是字线B0会对Cbit充电,使得VB0<VCC/2,此时VB0经过放大器Sense AMP后电压被拉直GND,即读出0。

写过程

写0

- 首先将位线B0拉低

- 然后将W0拉高,打开FET,Cbit通过B0放电置GND

- 拉低W0,完成写入0

写1

- 首先将位线B0拉高

- 然后将W0拉高,打开FET,Cbit通过B0充电至VCC

- 拉低W0,完成写入1

DDR为什么要刷新

其实了解了Cell结构,这个答案就很清楚了,DDR的数据保存就是通过Cbit电容保存电荷,因为漏电流的存在,如果长时间不操作Cell,那么电荷就会漏光,保存的数据就没有了。

所以为了保存住数据,需要定期对Cell单元里面的数据进行读取,然后再写入,这个过程就叫刷新。

————————————————

版权声明:本文为CSDN博主「硬件工程师炼成之路」的原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接及本声明。

原文链接:https://blog.csdn.net/weixin_42005993/article/details/103864181

1019

1019

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?