原文档-JESD209-4-LPDDR4

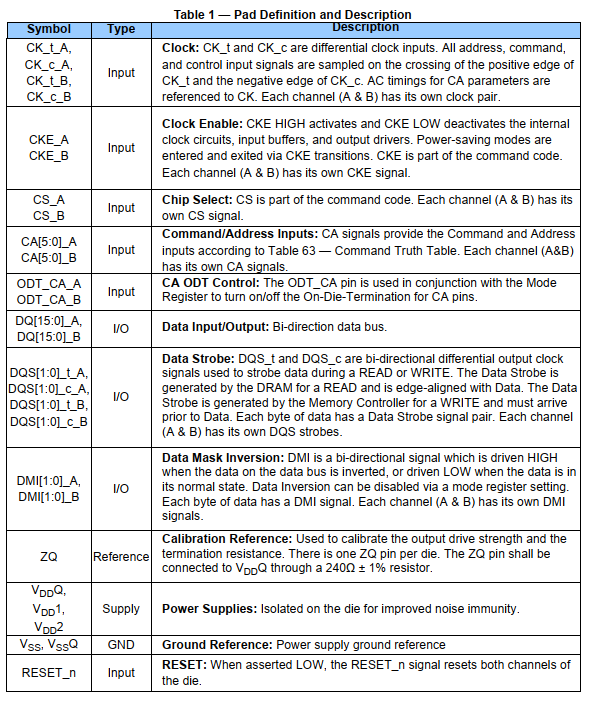

1.Pad definition & description

1.1

- CK_t_A/CK_c_A;CK_t_B/CK_c_B(输入)

- Clock

- CK_t和CK_c是差分时钟输入。

- 所有的地址、指令、和控制输入信号都在CK_t上升沿和CK_c下降沿采样。

- AC timings for CA 参数需要参考CK。

- 每个通道(A&B)都有自己的时钟对

- CKE_A、CKE_B (输入)

- clock enable

- CKE高有效

- 控制内部 时钟电路、输入缓存、输出驱动

- 省电模式进出由CKE转换控制

- CKE是指令码的一部分

- 每个通道有自己的CKE信号

- CS_A、CS_B(输入)

- chip select

- cs 是指令码的一部分

- 每个通道有自己的片选

- CA[5:0]_A、CA[5:0]_B(输入)

- command /address inputs

- CA信号提供指令和地址输入,参考table 63 指令真值表

- 每个通道都有自己的CA信号

- ODT_CA_A 、ODT_CA_B(输入)

- CA ODT Control

- ODT_CA端口用于 在模式寄存器连接中,以打开或关上片内终端电阻(On-Die_Termination)

- DQ[15:0]*A DQ[15:0]_B (I/O)

- Data input/Output

- 双向数据总线

- DQS[1:0]_t _A/DQS[1:0] _c _A;DQS[1:0]_t _B/DQS[1:0] _c _B (I/O)

- Data Strobe

- DQS_t 和DQS_c是双向差分时钟信号

- 用于在读写过程中strobe数据

- DRAM读操作可以生产DQS,并且与DATA同沿

- 存储控制器写操作也可以生成DQS,并且需要比数据早一个周期

- 数据的每个BYTE都有DQS对

- 每个通道都有自己的DQS

- DMI[1:0] _A,DMI[1:0] _B(I/O)

- Data Mask Inversion

- DMI是一个双向信号

- 数据总线上的data inverted时,DMI为高

- 数据总线上数据正常时,DMI为低

- 数据翻转可以 通过模式寄存器关闭

- 数据的每个Byte都有DMI信号

- 每个通道都有自己的DMI信号

- ZQ(reference)

- Calibration Reference

- 同于标定输出驱动强度和终端电阻。

- 每个die都有一个ZQ端口

- ZQ管教应该连接到VDDQ,中间挂一个240Ω±1%的电阻

- VDDQ VDD1 VDD2 (Supply)

- Power Supplies

- 独立位于die,用于提高抗干扰度

- Vss,VssQ(GND)

- ground referrence

- 电源参考地

- RESET_n(输入)

- 此信号为低,复位die上两个通道

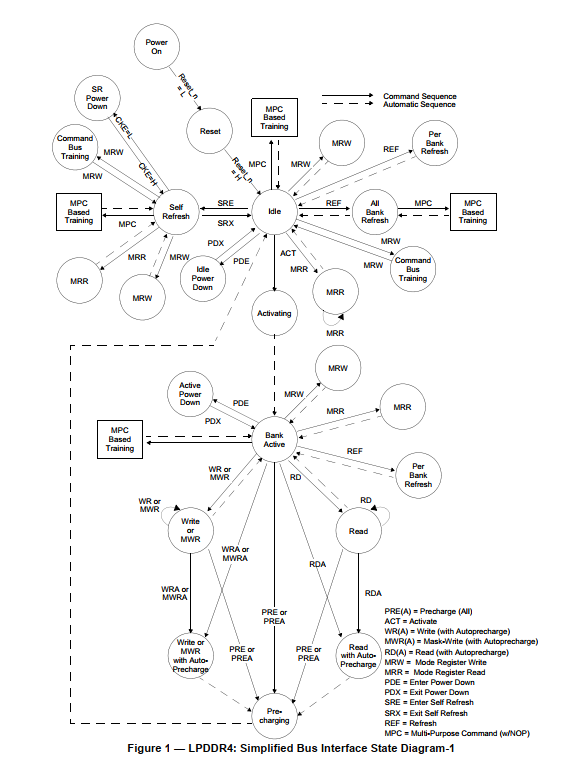

2 Function Description

2.1 Simplified LPDDR4 State Diagram

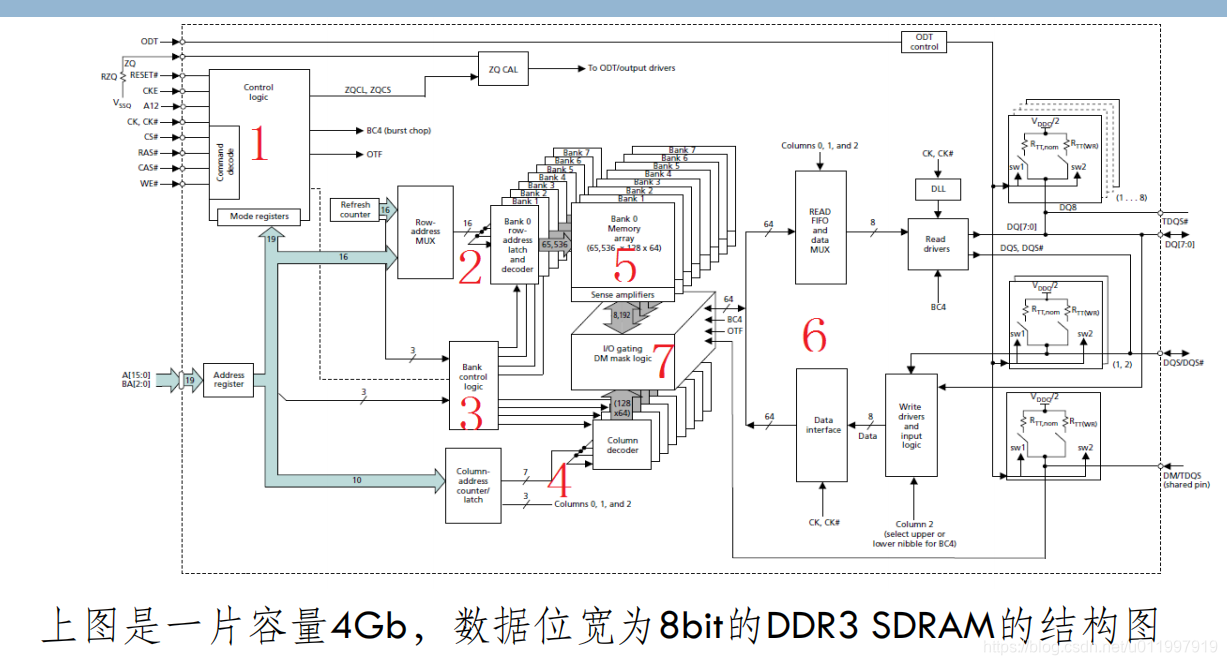

3 DDR的片内结构框图

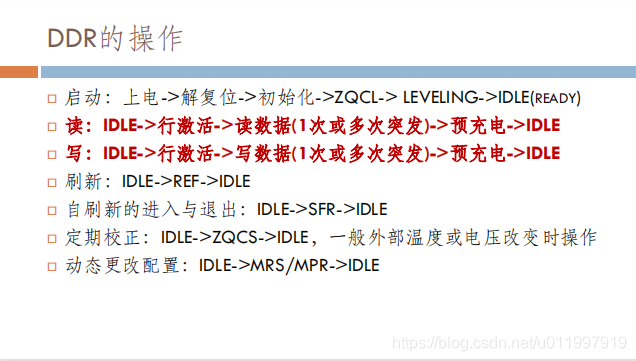

4 DDR的操作

本文档详细介绍了LPDDR4内存的引脚定义、功能描述和操作流程。CK_t/CK_c是差分时钟输入,所有信号在CK_t上升沿和CK_c下降沿采样。CKE控制内部时钟,CS是片选信号,CA提供指令和地址输入,DQ和DQS是数据总线,DMI用于数据翻转控制,ZQ用于校准。此外,还提到了LPDDR4的工作状态图和片内结构框图。

本文档详细介绍了LPDDR4内存的引脚定义、功能描述和操作流程。CK_t/CK_c是差分时钟输入,所有信号在CK_t上升沿和CK_c下降沿采样。CKE控制内部时钟,CS是片选信号,CA提供指令和地址输入,DQ和DQS是数据总线,DMI用于数据翻转控制,ZQ用于校准。此外,还提到了LPDDR4的工作状态图和片内结构框图。

4099

4099

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?