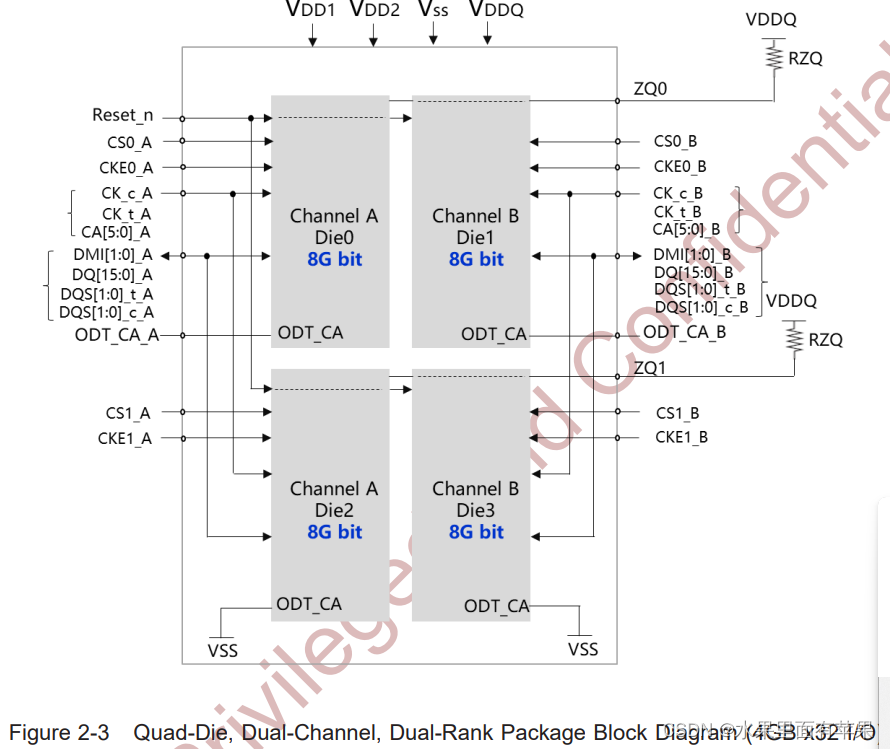

LPDDR4芯片学习记录

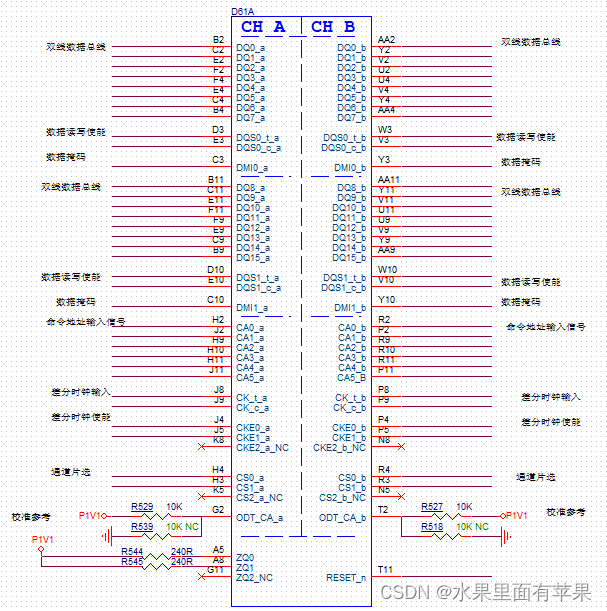

1.LPDDR4芯片引脚说明

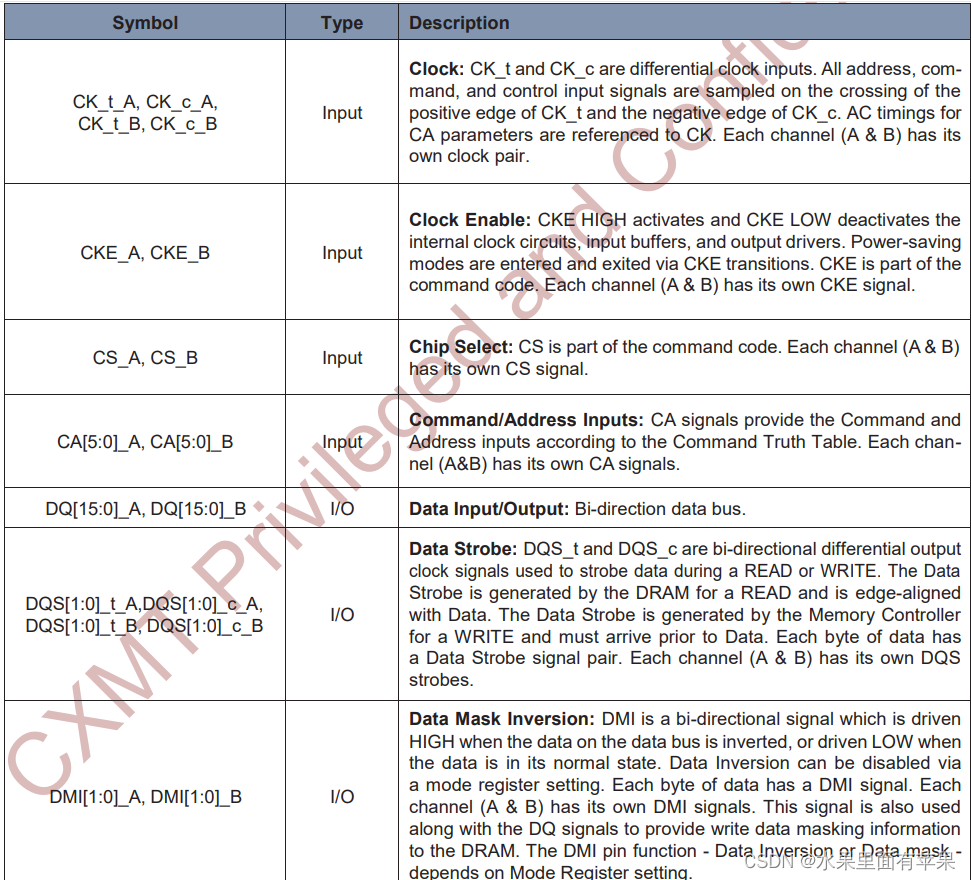

- CK_A,CK_An,CK_b,CK_bn

时钟:CK和CKn是差分时钟输入。所有地址、命令和控制输入信号都在CK的上升沿和CKn的下降沿交叉采样。CA参数的交流时序参考CK。每个通道(A和B)都有自己的时钟对。 - CKE_A,CKE_B

时钟使能:CKE高电平激活并且CKE低电平停用内部时钟电路、输入缓冲器和输出驱动器。通过CKE的转换进入和退出省电模式。CKE是命令代码的一部分。每个通道(A和B)都有自己的CKE信号。 - CS_A,CS_B

芯片选择:CS是命令代码的一部分。每个通道(A和B)都有自己的CS信号。 - CA[5:0]_A,CA[5:0]_B

命令/地址输入:CA信号根据命令真值表提供命令和地址输入。每个通道(A和B)都有自己的CA信号。 - DQ[15:0]_A,DQ[15:0]_B

数据总线:双向数据总线。 - DQS[1:0]_A DQS[1:0]_An,DQS[1:0]_B,DQS[1:0]_Bn

数据使能:DQS和DQSn是用于在读取或写入期间对数据进行节拍的双向差分输出时钟信号。数据使能由DRAM在读取操作中生成,并与数据边沿对齐。数据使能由内存控制器在写入操作中生成,并且必须在数据之前到达。每个数据字节都有一个数据使能信号对。每个通道(A和B)都有自己的DQS使能信号。 - ODT_CA_A,ODT_CA_B

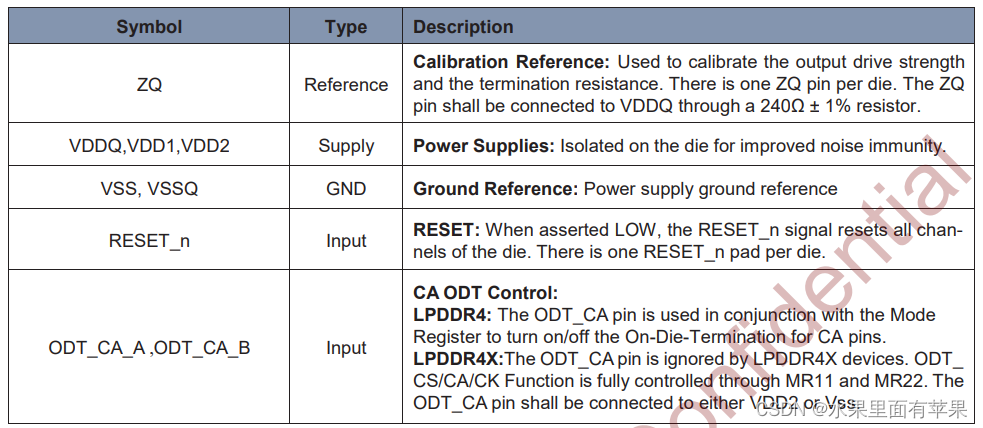

CA ODT控制:LPDDR4X设备忽略ODT_CA引脚。ODT-CS/CA/CK功能完全通过MR11和MR22进行控制。ODT_CA引脚应连接到VDD2或VSS - DMI[1:0]_ADMI[1:0]_B

数据掩码反转:DMI是一个双向信号,当数据总线上的数据被反转时,它被驱动为高电平;当数据处于正常状态时,它被驱动为低电平。可以通过模式寄存器设置禁用数据反转。每个数据字节都有一个DMI信号。每个通道(A和B)都有自己的DMI信号。该信号还与DQ信号一起用于向DRAM提供写数据屏蔽信息。DMI引脚的功能(数据反转或数据屏蔽)取决于模式寄存器的设置。 - ZQ

校准参考:用于校准输出驱动强度和终端电阻。每个芯片有一个ZQ引脚。ZQ引脚应通过240Ω ± 1%电 - VDD1

电源供应1:核心电源dram的core供电的,即dram内部的analog电路 - VDD2

电源供应2:核心电源dram的core供电的,即dram内部的analog电路 - VDDQ

DQ电源供应:隔离在芯片上,以提高抗干扰能力。dram的IO上供电的,如DQ/CA等IO的电路,需要的电压比较小 - VSS,VSSQ

底线 - RESETn

复位:当RESETn信号为低电平时,将复位芯片的两个通道

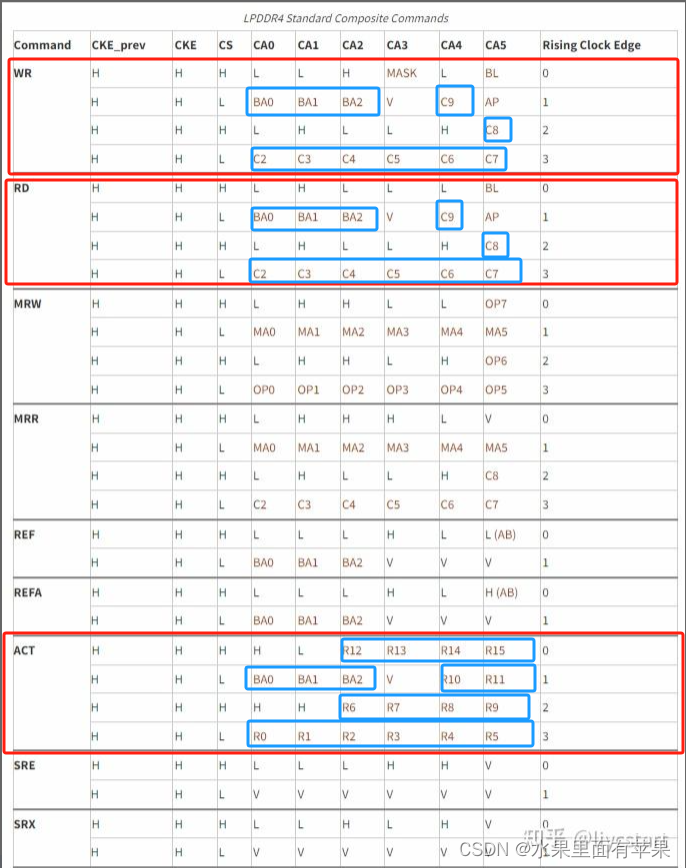

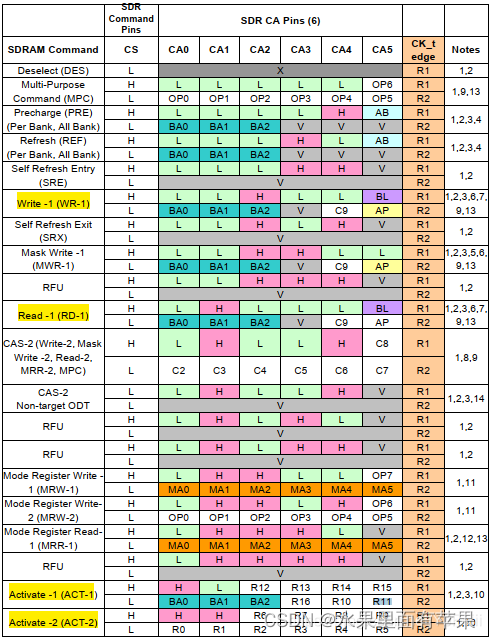

2. 协议与时序

- ACTIVATE命令由两个连续命令组成,Activate-1命令和Activate-2。通过在(Activate-1)时钟的第一个上升沿保持CS HIGH,CA0 HIGH和CA1 LOW来发出Activate-1命令,通过在(Activate-2)时钟的第一个上升沿保持CS HIGH,CA0 HIGH和CA1 HIGH来发出Activate-2命令。存储体地址BA0,BA1和BA2用于选择所需的存储体。行地址用于确定在选定存储区中激活哪一行。

161

161

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?