参数设定:

主时钟clk=16MHz,数据速率Rb=1Mbps,中心载波Fc=3Mhz,传号载波fL=2.75Mhz,fH=3.25MHz,调制度h=(fH-fL)*Rb;NCO的相位累加字宽度N=32,环路宽度Bloop=28;K=1.1781,Wn=150Khz,Tdds=12/fs;T=1/16M;

- 信源产生

信源采用的PN伪随机序列,周期为4095,采用12bit寄存器+反馈构成,速率为1Mbps,采用1MHz的时钟生成。参照《基于VerilogHDL的通信系统设计—陈曦》P184页。

- MSK调制模块整体说明

整体MSK调制的框图参见《数字调制解调技术的MATLAB与FPGA实现---杜勇》P234页。

需要进行单比特的差分编码,串并转换,I路延迟1Mbps的码片(16clk)。同时还有加权波0.25M和载波3M的计算。

- MSK解调模块整体说明

首先要实现单路平方环,用于从输入信号当中提取载波信号,框图如下:

以上是采用的一种改进的方式,鉴相2

![]()

,整体的鉴相能力减半。

环路滤波分两路走(计算用组合电路几乎不用时间):

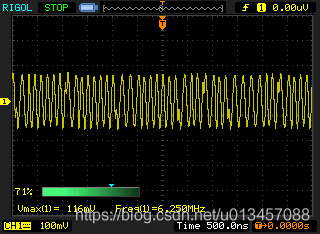

仿真与实战图片

上述为调制前和解调后的结果,可见通过调制解调回环,数据进行了还原。

1549

1549

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?