tCK (Clock Cycle Time): 时钟周期时间,即两个连续时钟边沿之间的时间间隔。

tRCD (RAS to CAS Delay): 行选通到列选通的延迟时间,即发出行地址到发出列地址的时间间隔。

tCL (CAS Latency): CAS延迟时间,即从列选通到数据输出的延迟时间,MR0决定。

tRP (RAS Precharge Time): 行选通预充电时间,即行选通结束到下一次行选通开始之间的时间间隔。

tRAS (Active to Precharge Delay): 行选通到预充电的延迟时间,即行选通到下一次行选通开始之间的时间间隔。

tWR (Write Recovery Time): 写恢复时间,即写操作完成后到下一次读或写操作开始之间的时间间隔。tWR is programmed through MR0.

tRFC (Refresh Cycle Time): 刷新周期时间,不同颗粒刷新周期有差别,例如350ns,500ns。

tREFI(the average Refresh interval):两次刷新之间的间隔时间,例如7.8us。MR3寄存器定义x tREFI。

tFAW (Four Activation Window): 四次行选通窗口时间,即在同一刷新周期内发出的行选通命令的最小时间间隔。

tRC (Row Cycle Time): 行周期时间,即两个连续行选通之间的时间间隔。

tCCD (CAS to CAS Delay): CAS到CAS延迟时间,即在同一行内切换列选通的时间间隔。tCCD_L:same bank group;tCCD_S:diff bank group

tRTP (Read to Precharge Delay): 读到预充电的延迟时间,即读操作完成到预充电开始之间的时间间隔。

tWTR (Write to Read Delay): 写到读延迟时间,即写操作完成到读操作开始之间的时间间隔。tWTR_L(Write to Read Delay Same Bank Group),tWTR_S(Write to Read Delay different Bank Group)

Write Latency(WL) = AL(Addition Latency,MR1决定)+CWL(CAS Write Latency,MR2寄存器决定) + PL(Parity latency)。

Read Latency(RL)= AL + CL (CAS Latency,MR0决定)。

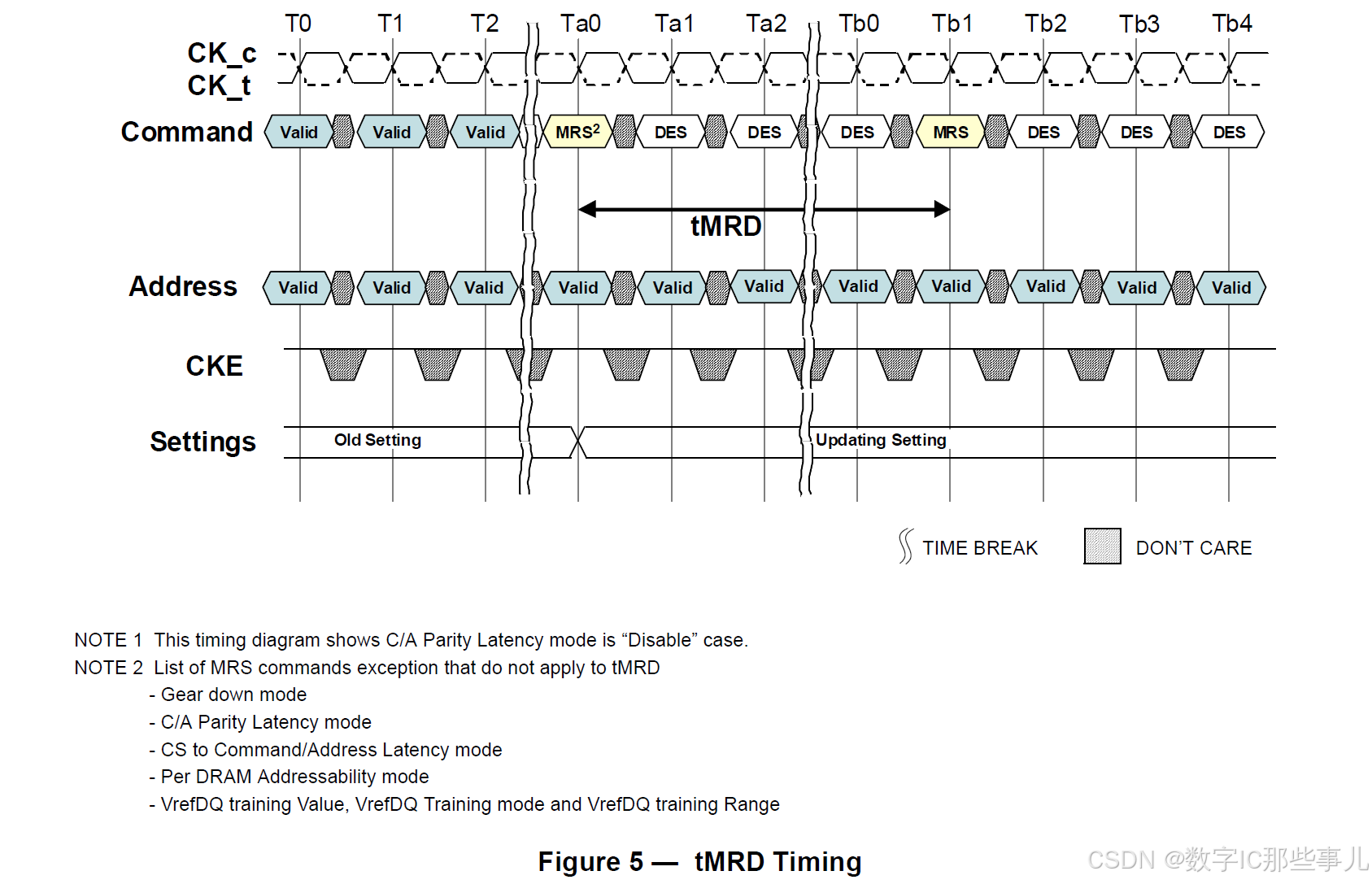

tMRD(the minimum time required between two MRS commands): MRS命令之间的延时。

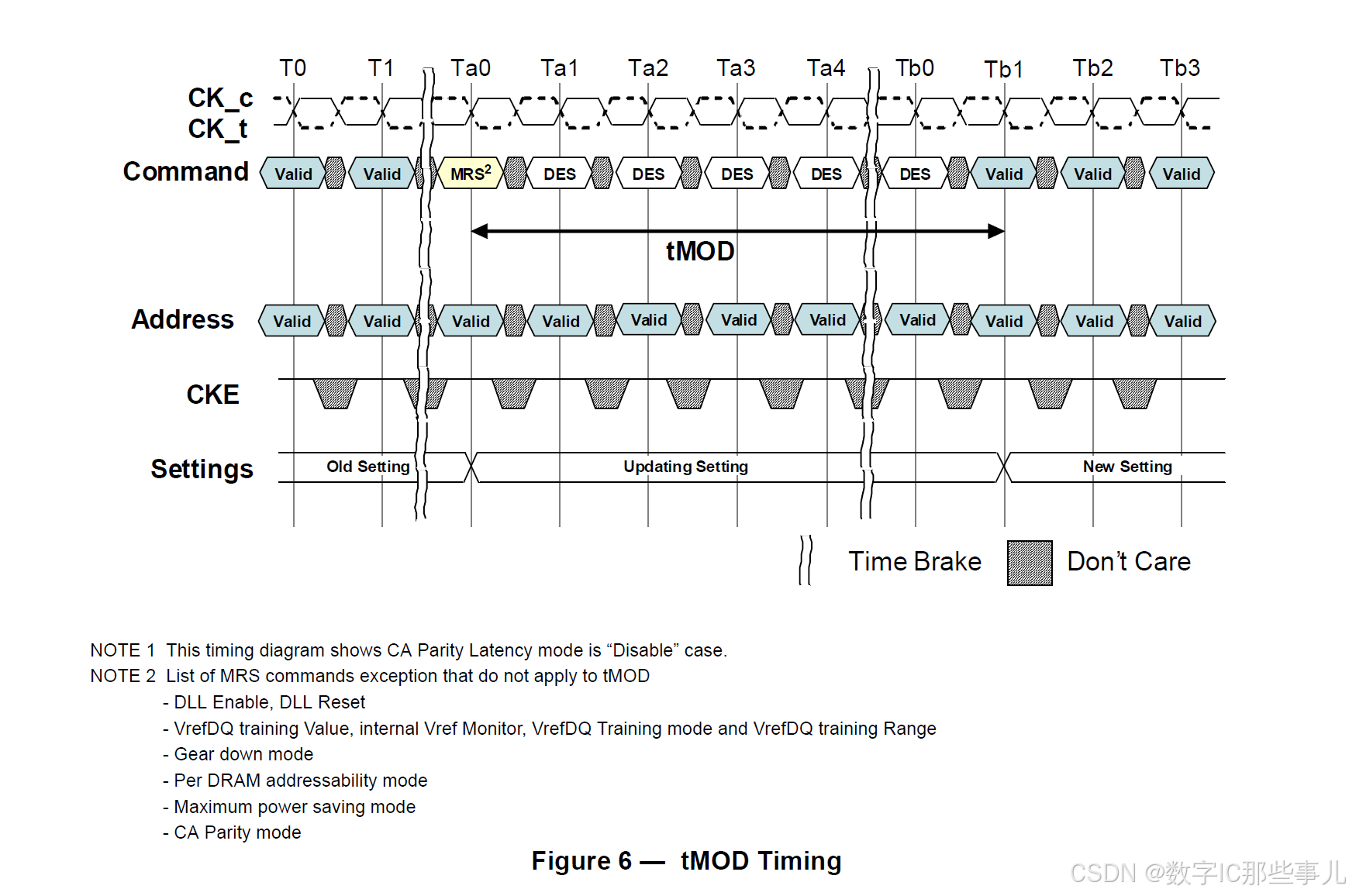

tMOD(The most MRS command to Non-MRS command delay):is required for the DRAM to update the features, and is the minimum time required from an MRS command to a non-MRS command excluding DES shown in Figure 6.

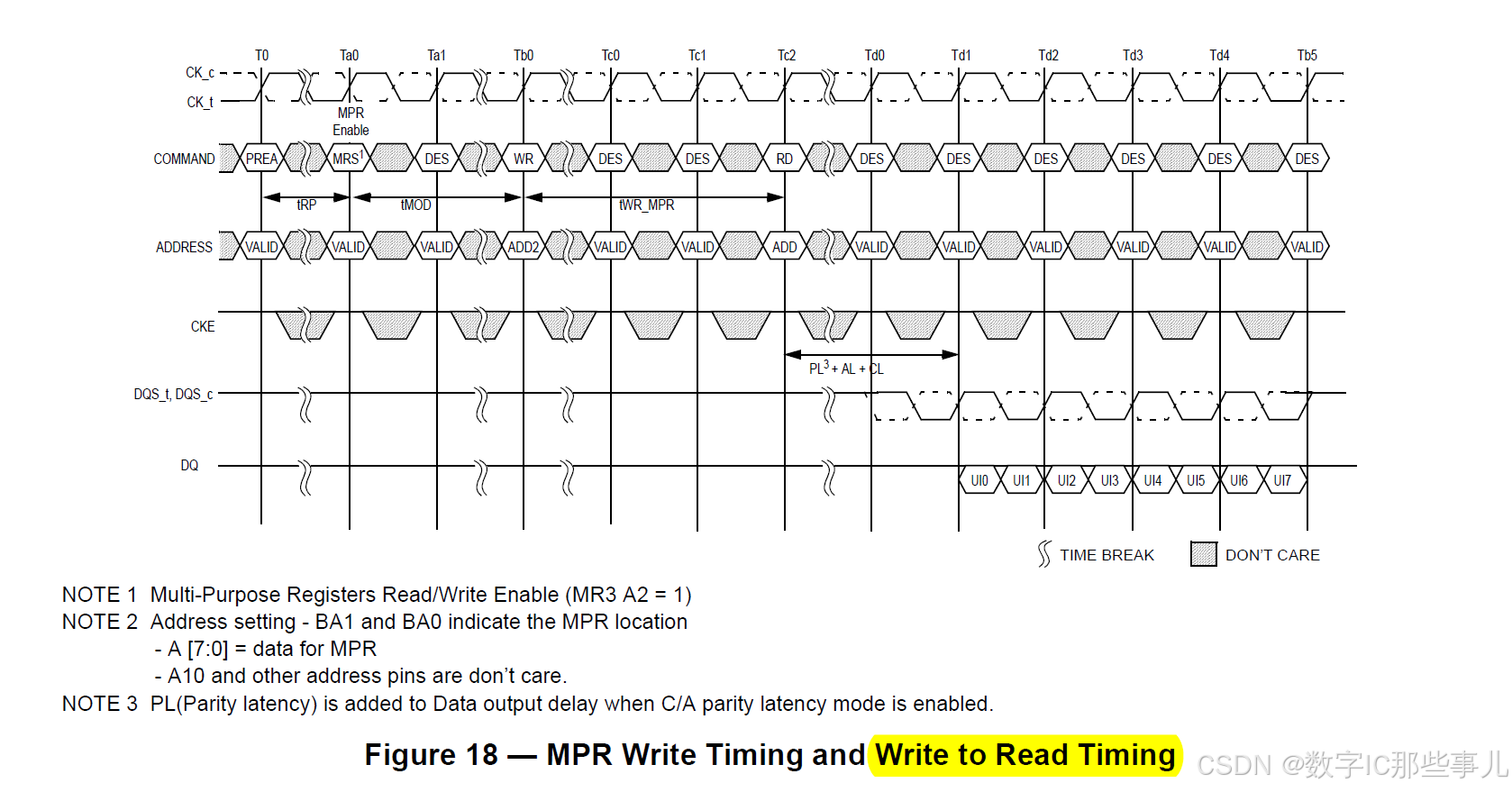

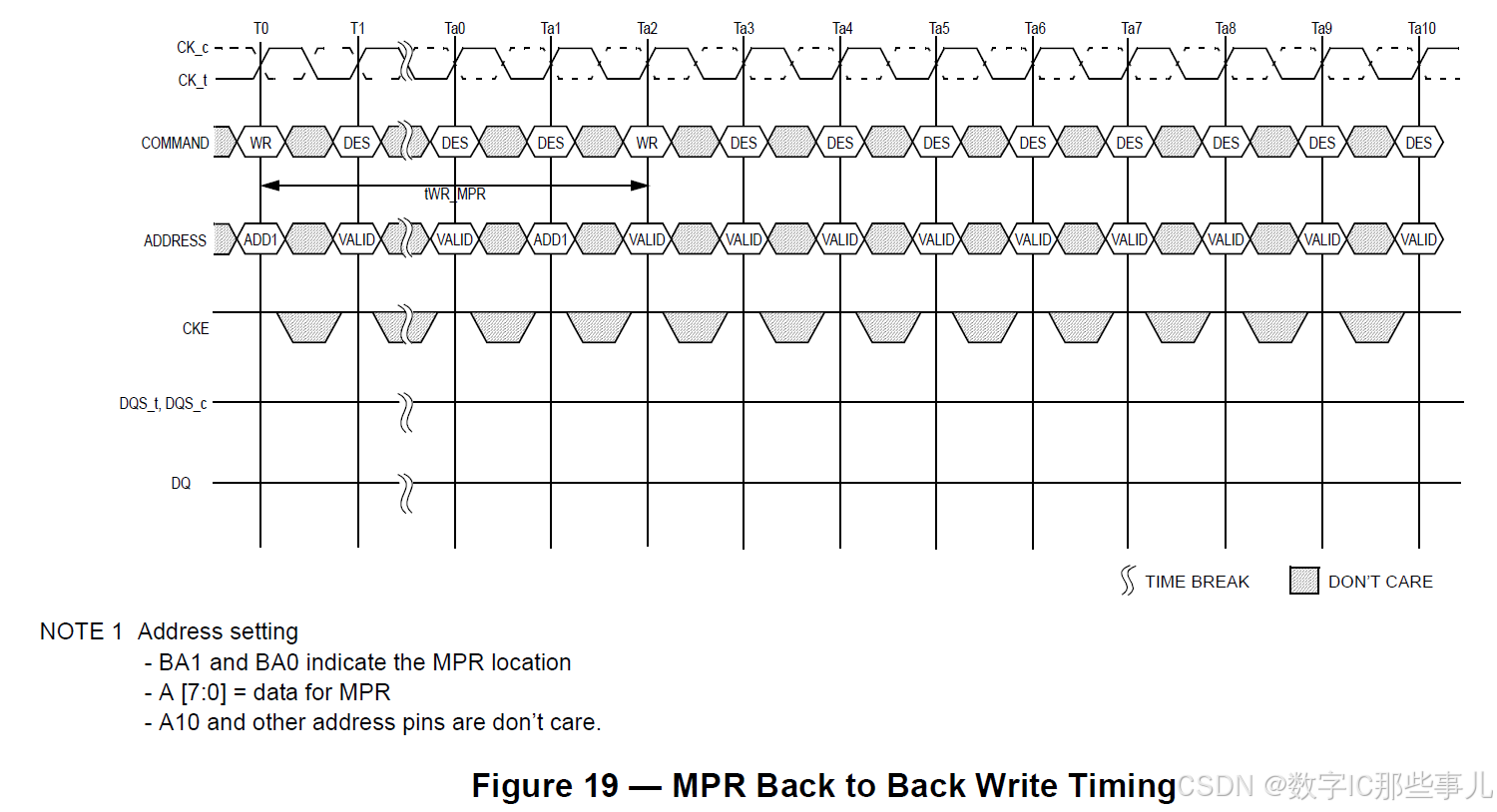

tWR_MPR(Multi Purpose Register Write Recovery Time):

tCKSRX: (Valid Clock Requirement before Self Refresh Exit (SRX) or Power-Down Exit (PDX) or Reset Exit)

本文详细解释了动态随机访问存储器(DRAM)中的关键时序参数,包括时钟周期、行选通延迟、CAS延迟、预充电时间等,这些参数对于理解内存性能和优化系统设计至关重要。

本文详细解释了动态随机访问存储器(DRAM)中的关键时序参数,包括时钟周期、行选通延迟、CAS延迟、预充电时间等,这些参数对于理解内存性能和优化系统设计至关重要。

868

868

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?