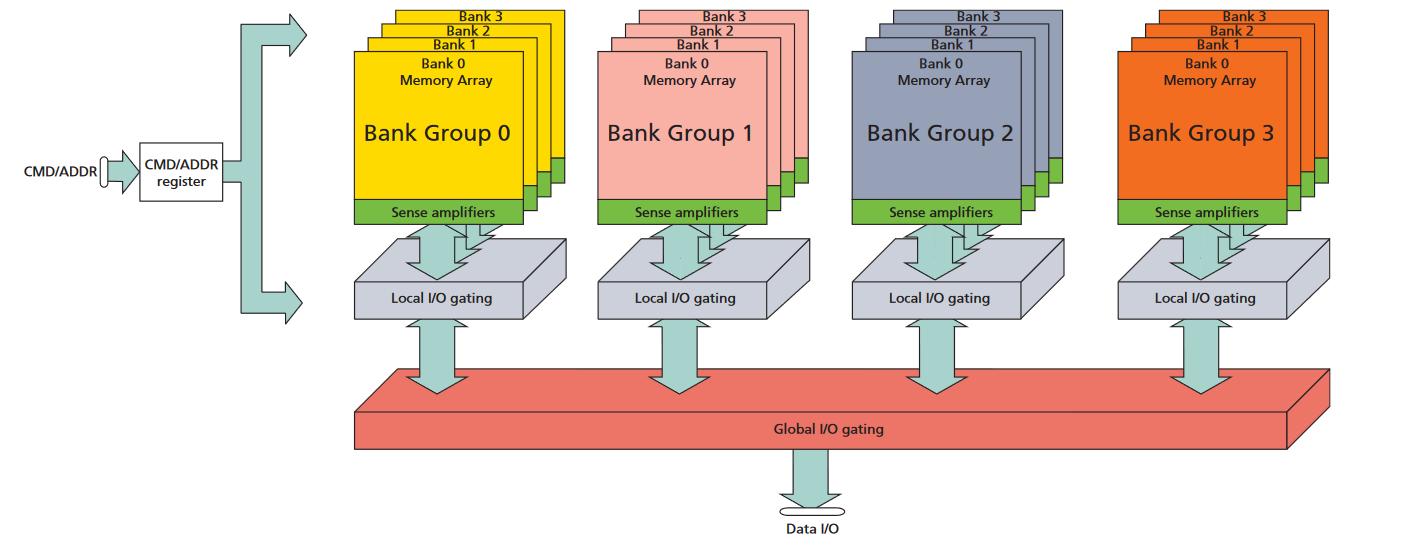

DDR4结构

DDR4的地址操作

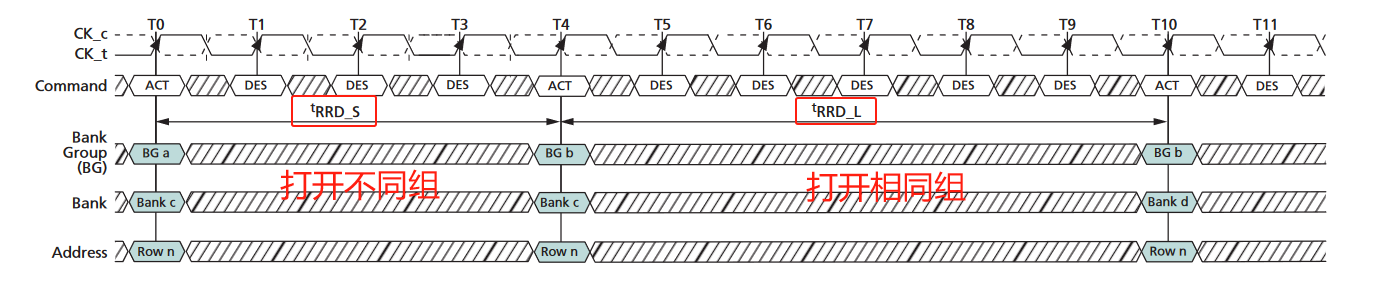

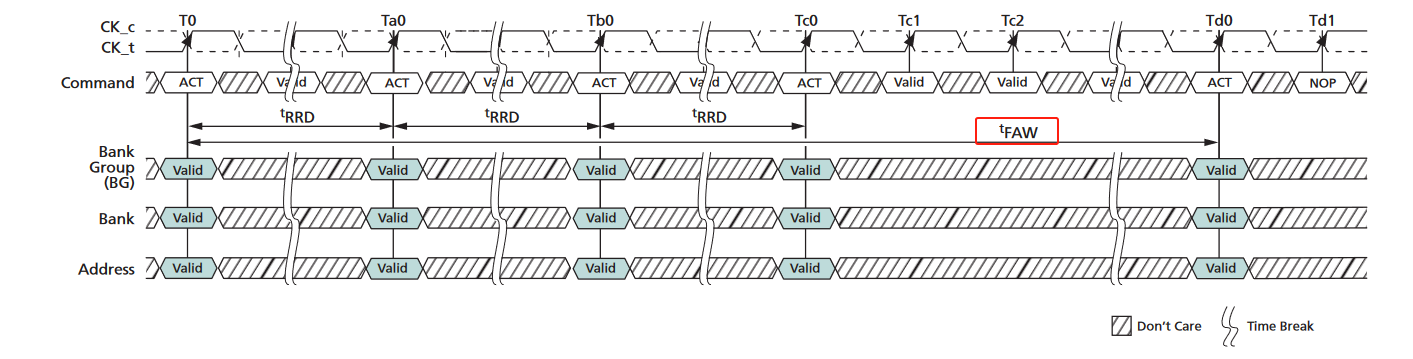

激活命令是打开一个存储块组中的一个存储块bank下的一行,用于接下来对该行的读写操作。下图是连续打开多个存储块bank的操作图,连续发出的激活命令ACT之间需要留有一定间隔时间tRRD,对于连续打开相同组的不同bank的行,时间会长一些。

此外,如果连续使用ACT命令打开了四个bank,打开下一个不同组的bank是,还会受到tFAW的约束。

如果在当前需要读写的地址所在的存储块bank已经被打开,这是分为两种情况,如果,要进行读写的地址正是在被打开的行上,那么可以直接进行读写操作,否则,需要发出预充电命令PRECHARGE,来关闭打开的行。对于发出PRECHARGE命令后,需要等待tRP时间后,才能对该bank进行激活操作ACT。

在DDR4中,还支持在读写操作完成后,自动对该行进行预充电来关闭该行

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

6288

6288

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?