平常编写FPGA程序的时候,最麻烦的就是时序违约

平常设计FPGA的时候,明明仿真都是对的,但是下板测试总会出现莫名其妙的问题。还有就是vivado每次编译出来的下板后现象都不一样,并且vivado没有报错的情况,这些问题的罪魁祸首就是时序紊乱,也可以说是时序违规。

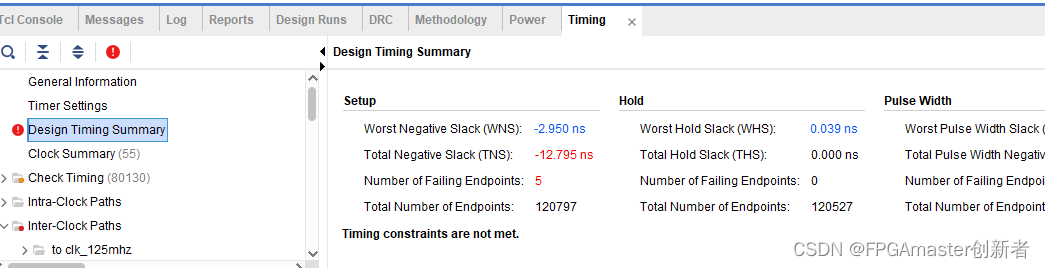

给大家列举几个时序违约的例子:

这些红色的错误,都会影响到整个工程的错误,而不是逻辑的问题,下面我将给大家介绍一种可以很简单的消除这种错误的办法,以及今后工作中如何避免这种错误的发生和理解时序违规的原理的过程。

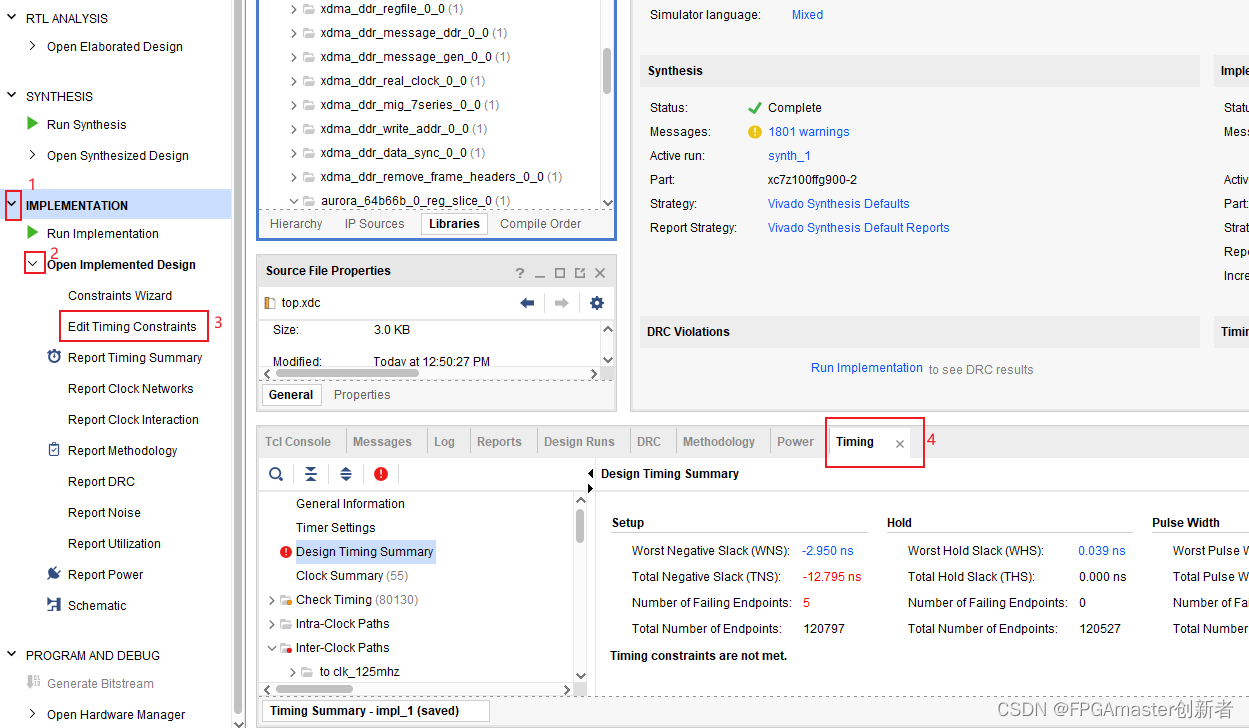

今天介绍一种简单的消除时序违约的办法:

1、vivado时序报告列出来的

首先打开时序报告:

可以发现,这里有两个违约病例

然后选中其中一个单机右键:

然后直接点击OK

并保存,他就会保存到xdc文件内即可

2、vivado时序报告没有列出来,但是会影响设计的

最多的就是组合逻辑,存在不确定的条件,

例如:

1、case 语句缺少default语句,或者(default : ;),会导致生产锁相环,用case的时候尽量就不要判断复位了,直接case

always @ (*) begin

case (c_state)

S0 : begin

if (en)

n_state = S1;

else

n_state = S0;

end

S1 : begin

if (en)

n_state = S0;

else

n_state = S1;

end

//此处缺少default,会产生锁相环

endcase

end应该改为:

always @ (*) begin

case (c_state)

S0 : begin

if (en)

n_state = S1;

else

n_state = S0;

end

S1 : begin

if (en)

n_state = S0;

else

n_state = S1;

end

default : n_state = 'bx;

endcase

end2、 if 语句 缺少 最后一个else ,会导致锁相环

always @ (*) begin

if (en)

data = 1;

else if (!en)

data = 0;

//此处缺少else,会产生锁相环

end应该改为:

always @ (*) begin

if (en)

data = 1;

else if (!en)

data = 0;

else

data = 0;

end这就是新手最容易碰到的时序错误了,希望大家引以为戒

如果感觉文章对您有用,麻烦三连支持一下,方便下次用到的时候,就可以快速找到我,非常感谢您的支持!!!

376

376

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?