本文章FPGA加载适用于Xilinx FPGA系列的A7、K7、V7以及zynq、zynqMP的PL端程序。将介绍如何利用 Slave Select Map(SSM) 接口和 JTAG 接口来加载 Xilinx FPGA 配置。通过这两种接口,用户可以灵活、高效地将 bit 文件上传至 FPGA,从而实现硬件功能的更新与调试

一、背景介绍

在某些特殊应用中,尤其是涉及到卫星、航天和其他高辐射环境的系统,单粒子翻转(SEU,Single Event Upset)是一个不可忽视的问题。SEU 是指高能粒子(如宇宙射线或粒子辐射)撞击到半导体器件时,可能导致存储单元发生位翻转,进而影响系统的正常工作。尤其是在 FPGA 中,单粒子翻转可能导致配置数据被破坏,影响 FPGA 的功能或导致系统崩溃。

所以我们一般设计上使用微处理器、CPLD、或不易被单粒子打翻的Flash型FPGA或者不易被单粒子反转的存储器件:FLASH、MRAM等, 对xilinx FPGA在线加载bit文件。保证FPGA功能能够正常运行。

本次设计采用A3P开发板作为加载FPGA,zedboard作为被加载FPGA。

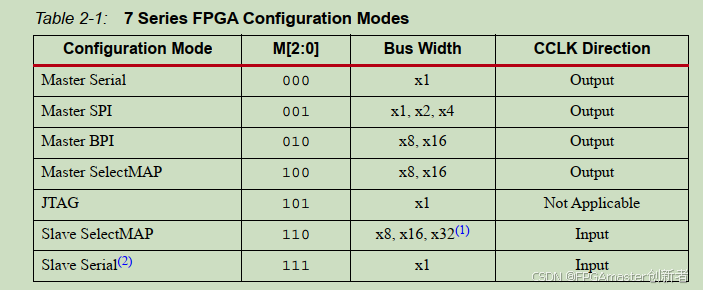

在Xilinx的官网文档上显示,FPGA加载类型如下图所示

通过外部加载一般我们都选择Slave Select Map 接口和JTAG接口进行加载。

二、 Slave Select Map 接口

2.1 硬件设计

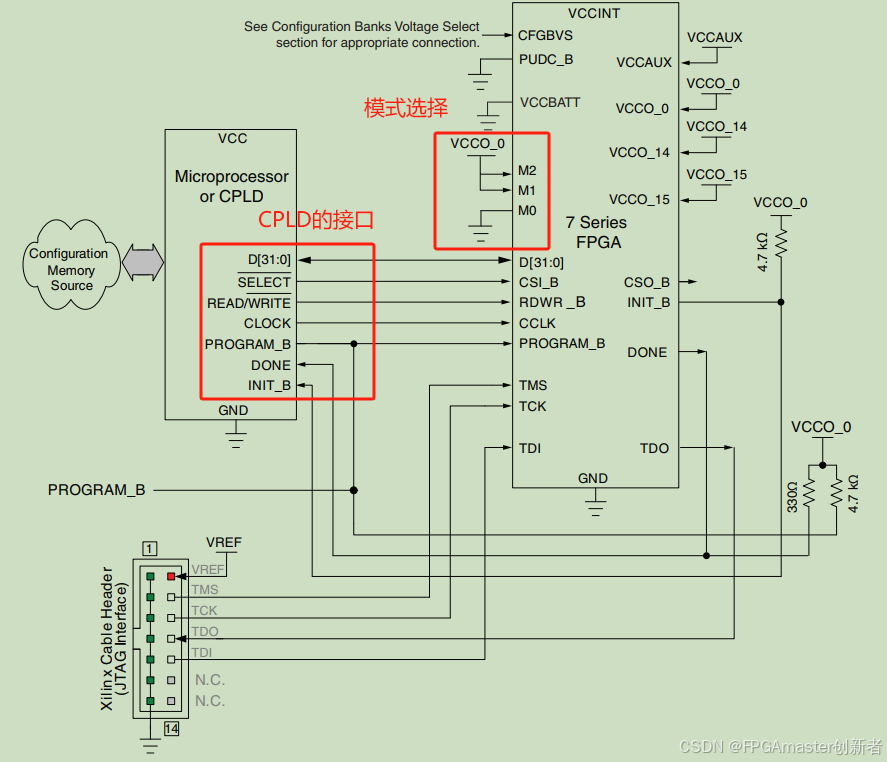

如果选择Slave Select Map 接口,需要在硬件开发的时候做一些相对应的处理,以CPLD为例子来介绍。

- 模式选择:根据上个图片介绍,需要把FPGA的模式选择设置为:M[2:0] == 3'b110

- 同时还要根据下图,把CPLD的接口预留出来给FPGA加载使用的。

- 在CPLD中存储启动文件的时候,尽量使用.bin后辍的文件

- 选择外部存储器的时候尽量选择不易被单粒子反转的器件,如:FLASH、MRAM等

细节注意:

1、处理器或CPLD I/O需要支持与连接的电压兼容的电压,7系列FPGA VCCO_0电源输入和AMD电缆VREF必须具有相同的电压。

2、DONE引脚是一个开漏输出。

3、INIT_B引脚是一个双向、漏极开路的引脚。需要外部上拉电阻器。

4、对于SelectMAP配置,必须为CCLK设置比特流启动时钟设置。

5、如果只有一个FPGA要接地,则CSI_B和RDWR_B信号可以接地不需要配置和回读。

5、CCLK信号完整性至关重要,可能需要终止,并不是连续的CCLK。

6、VCCBATT是存储在SRAM中的AES密钥的电源。它应该连接到电池供电(使用时)。

7、对于从属SelectMAP配置,数据总线宽度可以是x8、x16或x32。SelectMAP x16和x32总线宽度不支持AES加密比特流。

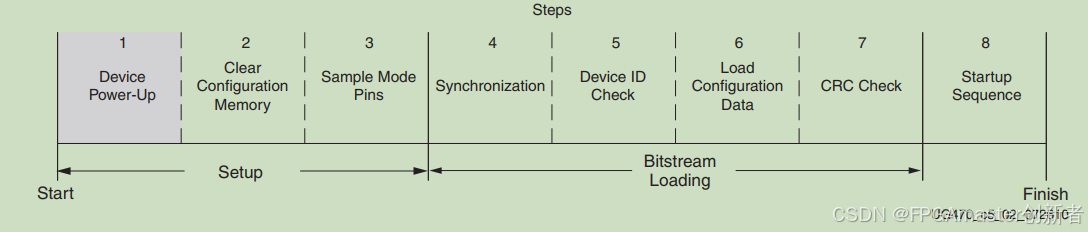

2.2 加载流程

对于Slave Select Map接口加载FPGA,主要分为以下几步

1、设备上电

2、清除FPGA配置寄存器

3、采集模式引脚,M[2:0]

4、同步码检测 0xAA995566

5、设备ID检查

6、加载配置信息数据

7、CRC校验

8、启动配置序列

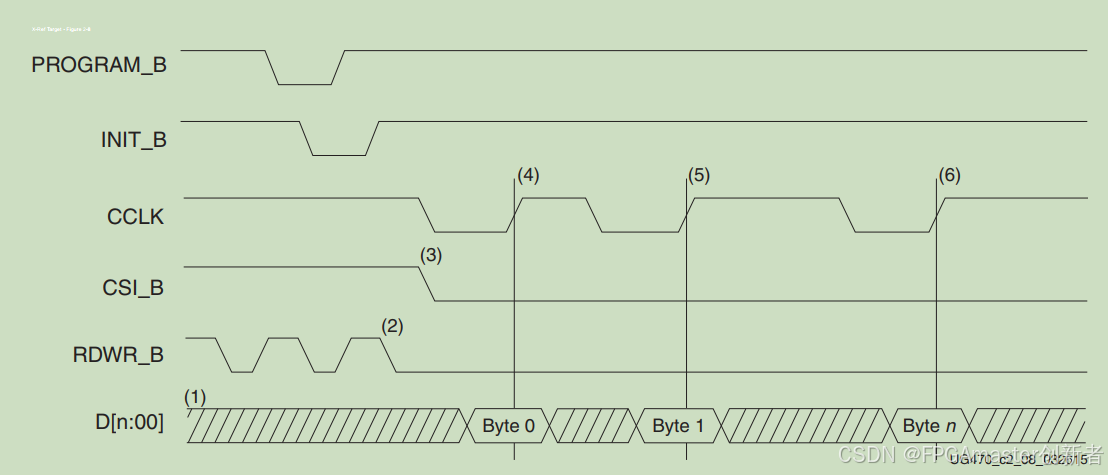

加载时序如下图所示

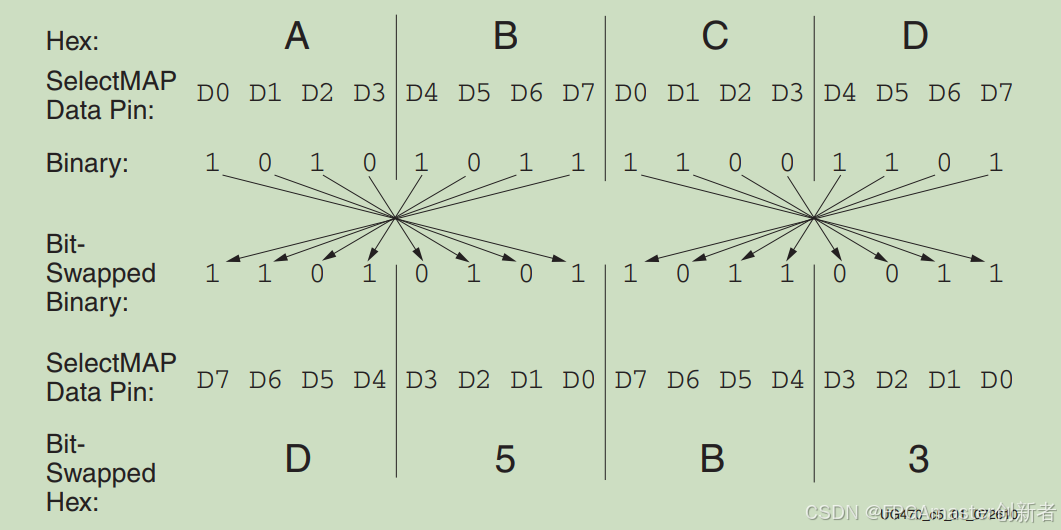

同时对于bit文件加载的时候,还需要进行大小端转换,以0xABCD为例,大小端转化如下图所示:

2.3 优缺点

优点:利用Slave Select Map接口进行加载,实现起来方式相对来说比较简单

缺点:需要再设计开发板的时候提前根据要求,定制需要的硬件,对于现成的开发板来说,此方式并不适用。所以对于现成的开发板,我们选择通过JTAG接口进行设计。

三、 JTAG接口

因为我们想要不修改开发板硬件的前提下,进行对Xilinx FPGA重加载,也应为JTAG协议比较标准,在很多嵌入式设备都比较常用,所以这次我们主要采用JTAG接口进行加载,争取做一个通用的加载设计。

3.1 硬件设计

JTAG也是Xilinx官方推荐的一组接口,同时符合IEEE 1149.1标准协议,硬件设计一般比较简单,也就是大家平常用的JTAG接口电路。

- 模式选择:根据Slave Select Map接口硬件图片介绍,需要把FPGA的模式选择设置为:M[2:0] == 3'b101

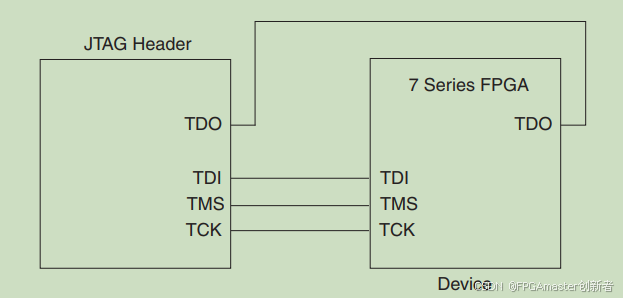

- 同时只需要把下图中的JTAG Header中的四个接口,接到CPLD即可

- 在CPLD中存储启动文件的时候,尽量使用.bin后辍的文件

- 选择外部存储器的时候尽量选择不易被单粒子反转的器件,如:FLASH、MRAM等

3.2 JTAG介绍

Xilinx 7系列设备支持IEEE 标准测试访问端口和边界扫描架构 (IEEE Std 1149.1),通过JTAG加载PL端配置文件(bit文件),主要依据TAP控制器进行实现配置信息的加载,而对于zynq的PS端,则需要通过DAP控制器去加载ARM的部分,进而去加载PL端。

TAG(Joint Test Action Group;联合测试行动小组)是一种国际标准测试协议(IEEE 1149.1兼容),主要用于芯片内部测试。现在多数的高级器件都支持JTAG协议,如DSP、FPGA器件等。标准的JTAG接口是4线:TMS、TCK、TDI、TDO,分别为模式选择、时钟、数据输入和数据输出线。

(1)7 系列 FPGA TAP控制引脚

JTAG接口包括以下几个信号:

- TMS(Test Mode Select):用于设置测试模式和测试状态机的状态。通过 TMS 信号,可以控制 TAP 在不同的状态间相互转换。TMS 信号在 TCK 的上升沿有效。TMS 具有内部电阻式上拉,可在引脚未驱动时提供逻辑高。

- TCK(Test Clock):用于提供时钟信号,控制测试状态机的运行。

- TDO(Test Data Out):此引脚是所有JTAG指令和数据的串行输出,TDO具有内部电阻拉拔,如果引脚不活动,则提供逻辑高。

- TDI(Test Data Input):用于向测试状态机输入数据。在 TCK 的上升沿有效。TDI 具有内部电阻拉拔,可在引脚未驱动时为系统提供高逻辑。

- TRST(Test Reset Input): RST可以用来对TAP Controller进行复位(初始化)。不过这个信号接口在IEEE 1149.1标准里是可选的,并不是强制要求的。 因为通过 TMS 也可以对 TAP Controller 进行复位(初始化)

(2)TAP控制器和架构

在讲到TAP控制器之前,先给大家介绍一下两个寄存器,也是JTAG协议中,最经常使用的两个寄存器

在 FPGA 和其他数字系统中,指令寄存器(IR,Instruction Register)和数据寄存器(DR,Data Register)是常见的寄存器,特别是在使用 JTAG 接口或类似的串行通信协议时。它们在处理器架构、通信协议和调试过程中发挥着重要作用。下面是它们的简要介绍:

① 指令寄存器(IR,Instruction Register)

指令寄存器的主要作用是存储和管理指令,这些指令控制着外设的操作,在 JTAG 协议中,指令寄存器确定了要执行的测试或配置操作,比如读取、写入、扫描链的控制等,在执行特定操作时,IR 会根据控制信号来选择适当的功能模块或通道。

② 数据寄存器(DR,Data Register)

数据寄存器用于存储实际的数据,尤其是在数据传输过程中,它作为接收和发送数据的中介。在 JTAG 流程中,数据寄存器用于存储用于测试、调试或配置操作的数据。在 FPGA 设计中,数据寄存器可以直接与设计的模块相连,用于数据的缓冲和传输。

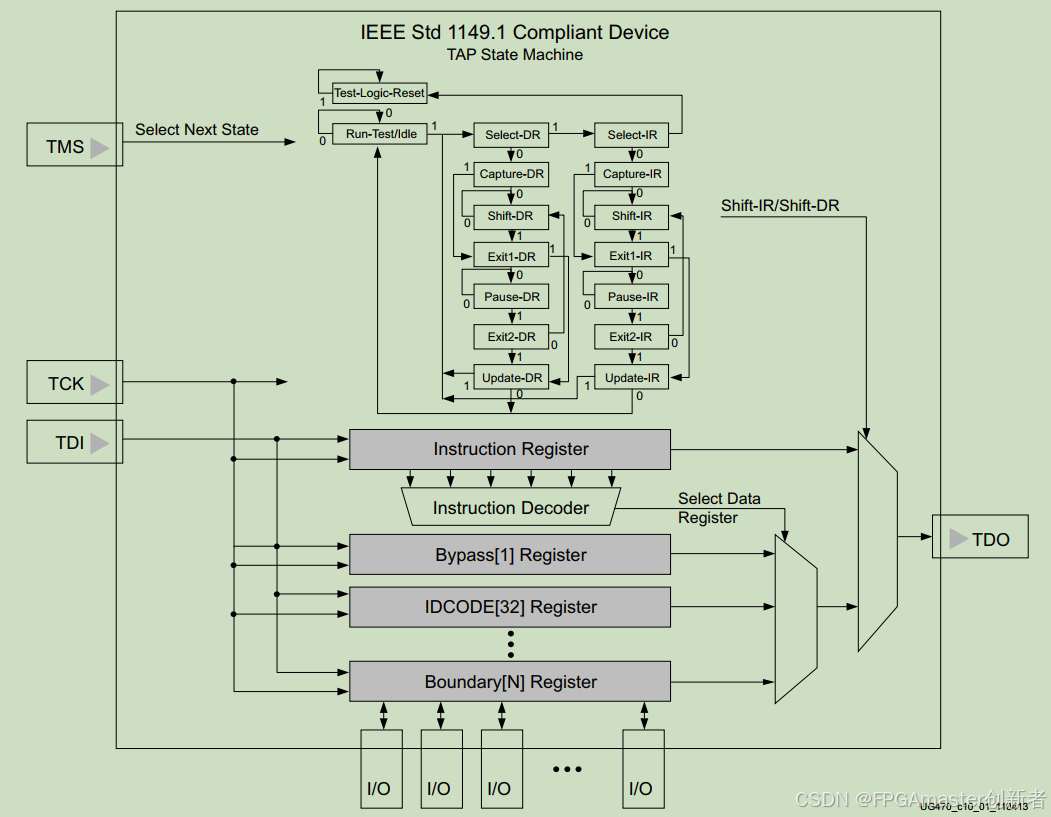

典型的JTAG架构

主要通过JTAG接口去控制的TAP控制器

由上图可以看出来,TAP控制器主要是通过控制TMS的电平,来控制TAP控制器的状态,然后通过TDI来获取指令和数据,在SHIFT-DR状态去传递数据,在SHIFT-IR状态去传递数据信息,并从TDO得到TAP控制器的反馈信息,然后整个流程都是在TCK的上升沿进行工作的。

TAP各个状态介绍

| TAP状态 | 功能 |

| Test-Logic-Reset | 在此控制器状态下禁用所有测试逻辑 |

| Run-Test-Idle | 空闲状态,等待触发指令 |

| Select-DR-Scan | 数据和指令状态选择,此控制器状态控制是进入数据路径还是指令路径 |

| Select-IR-Scan | 此控制器状态控制是否进入指令路径。否则,控制器可以返回测试逻辑重置状态 |

| Capture-IR | 捕获IR状态,获取IR数据开始 |

| Shift-IR | 在这种控制器状态下,指令寄存器连接在TDI和TDO之间,捕获的图案在TCK的每个上升沿取值。TDI引脚上的可用指令也被移入指令寄存器 |

| Exit1-IR | 此控制器状态控制是进入暂停IR状态还是更新IR状态。 |

| Pause-IR | 暂停IR状态 |

| Exit2-DR | 此控制器状态控制是否进入Shift-DR状态或Update-DR状态。 |

| Update-IR | 在这种控制器状态下,指令寄存器中的指令在TCK的每个下降沿上被锁存到指令寄存器的锁存器组。此指令在锁存后成为当前指令 |

| Capture-DR | 在这种控制器状态下,数据被并行加载到TCK上升沿上由当前指令选择的数据寄存器中 |

| Shift-Dr, Exit1-DR, Pause-DR, Exit2-DR, and Update-DR | 这些控制器状态类似于Shift-IR, Exit1-IR, Pause-IR, Exit2-IR, and Update-IR状态 |

(3)IR指令集

IR指令集特别多,在这里我只列出几个比较常用的指令集(只适合Xilinx FPGA)

| IR指令 | binary code[5:0] | 描述 |

| CFG_OUT | 6'b000100 | 访问配置总线进行回读 |

| CFG_IN | 6'b000101 | 访问配置总线进行配置 |

| USERCODE | 6'b001000 | 允许移出用户代码 |

| IDCODE | 6'b001001 | 允许移出ID代码 |

| JPROGRAM | 6'b001011 | 等同于PROGRAM,并具有与PROGRAM相同的效果 |

| JSTART | 6'b001100 | 启动码流时序 |

| JSHUTDOWN | 6'b001101 | 关闭码流时序 |

| BYPASS | 6'111111 | 使能BYPASS |

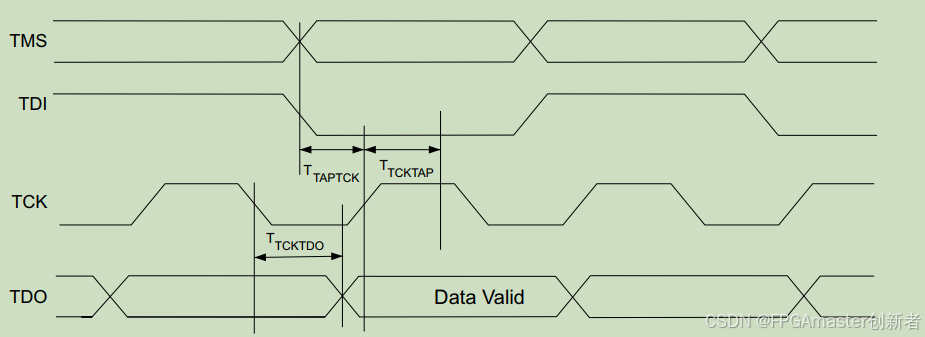

(4)JTAG定时参数时序

为了可以正确通过JTAG引导启动FPGA,还必须满足如下时序定时参数

3.3 优缺点

硬件设计比较简单,可以直接使用现有的开发板(预留JTAG接口),但是代码实现起来可能比Slave Select Map接口来说,比较复杂,但是实现起来后可以使用很多设备,可移植性比较强,所以我也推荐大家使用这种方法。

Xilinx FPGA重构的两种方法的原理以及时序大致就介绍完了,下面一节我们将介绍如何通过Verilog代码去实现他们,以及通过下板去调试。

Verilog实现JTAG接口协议快速入口:Verilog实现JTAG接口协议

制作不易,记得三连哦,给我动力,持续更新!!!

4506

4506

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?