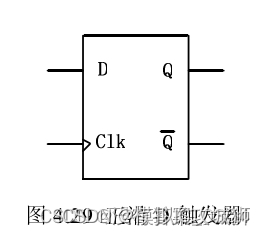

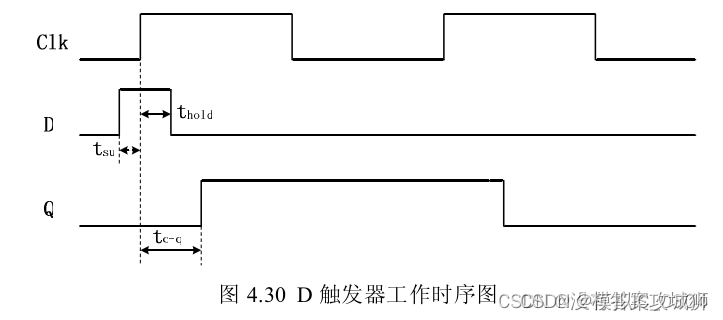

一、D触发器原理

正沿D触发器的工作时序图

在时钟由低电平到高电平的转换阶段,将输入端的数据锁存到输出端,直到下一个上升沿到来之前保持不变, 其为边沿触发器件。其关键时序参数有建立时间(ts u )、延迟时间(tc -q )、保持时间 (th old ),如图所示,建立时间指的是输入信号在时钟上升沿之前必须稳定的时 间,传播延迟时间是数据信号在时钟上升沿到输出端Q有效转换所需要的时间, 保持时间是在时钟上升沿之后数据输入必需稳定的时间。

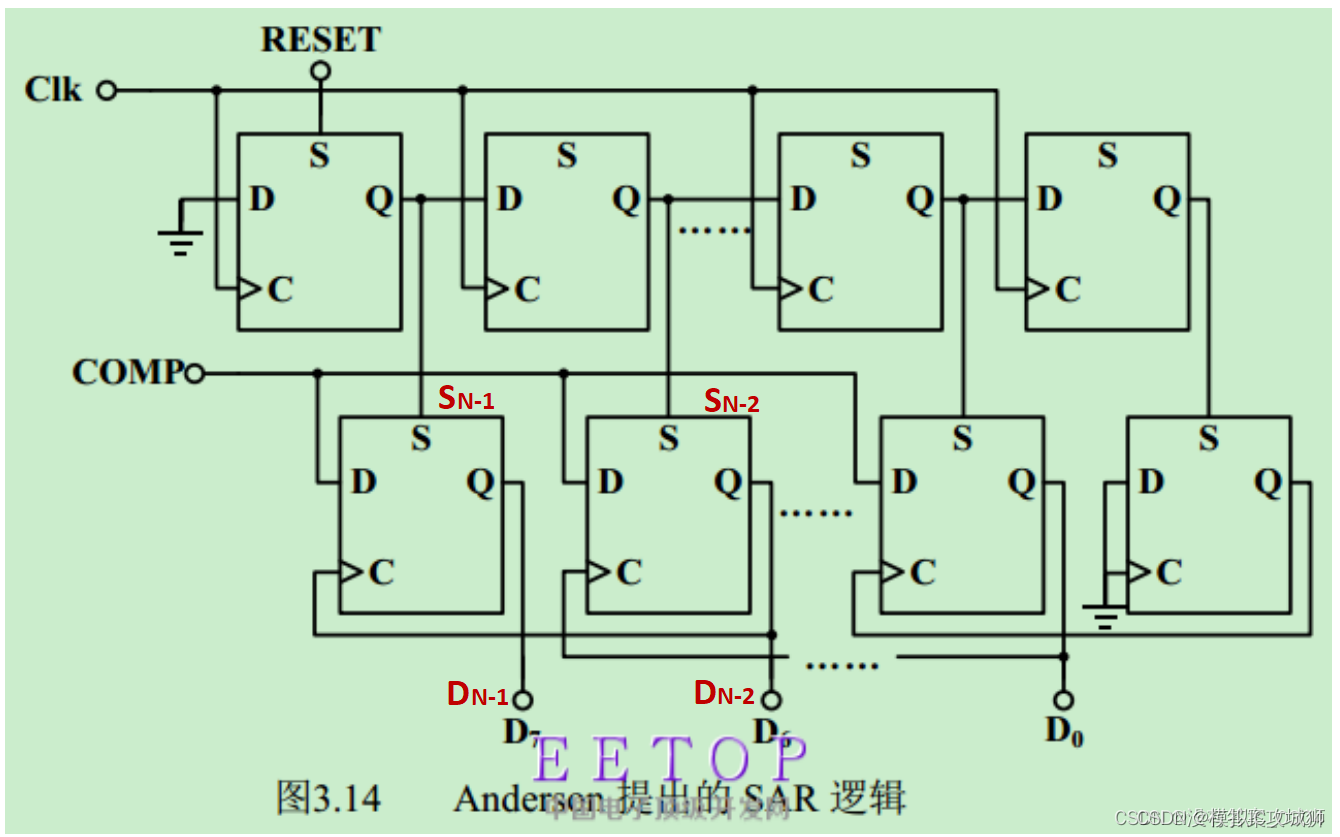

二、同步SAR逻辑

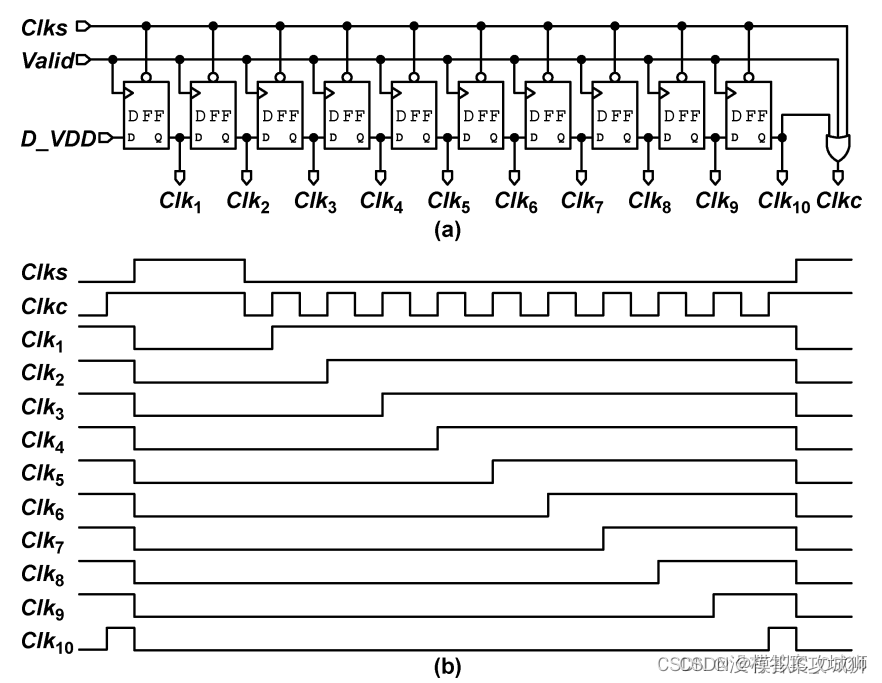

上面一排D触发器是相当于相位指针逻辑电路,主要用于移位操作;下面一排D触发器作为寄存器使用,根据上面一组排触发器的输出指针将比较器的结果存储至相应位的D触发器中。在比较之前Reset信号会先将上面第一个触发器和下面第一个触发器的输出D7预置为1,D6-D0都清0,也就是先假设D7为1,然后CLK高电平到来根据COMP信号改变或保持D7的值。

工作流程

再开始转换之前,reset信号讲上一排第一个D触发器复位,SN-1为“1”,DN-1输出为高,DN-1对应最高位DAC置1,DAC输出值供给比较器比较,输出COMP。CLK下一个时钟沿来临,SN-1通过第一排第二个触发器使SN-2为“1”,

DN-2输出为高,触发下排第一个触发器,此时DN-1变化为COMP,此时完成最高位的判断和存储。此时DN-2为1,等待下排第三个DN-3为1时触发下排第二个比较器,将DN-2变化为COMP.

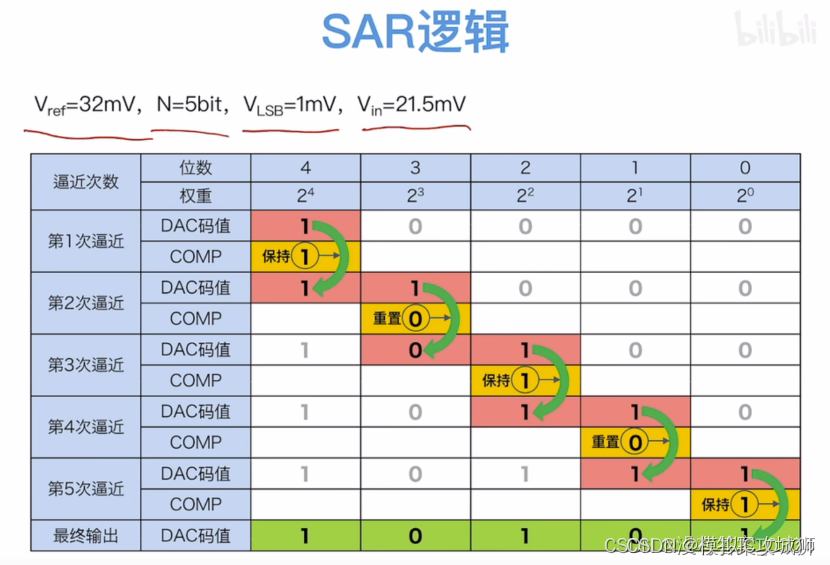

比较过程

每一位D值初始都置1,给cmp比较,根据COMP输出为1或0,来保持或改变该位的D码值,存储该位码值后,再进行下一位的比较。

SAR 控制逻辑可以分为两种:同步逻辑电路和异步逻辑电路。同步逻辑电路是通

过一个内部时钟同时作为比较器和逻辑电路的时钟,为了尽可能的提高比较器的比较

速度,这个内部时钟必然是一个高频时钟。假设一个 ADC 采样率为 Fs,分辨率为 N

位,那么这个内部时钟的频率至少为 Fs*(N+1),而产生一个高频时钟需要的功耗是

十分大的。除了功耗十分大,同步逻辑电路的另一个缺点是由于没有合理利用输入信

号与比较时间之间的关系导致模数转换的时间变长。从对比较器的描述中可知,当输

入电压比较大时比较时间较短,而当输入电压比较小时比较时间较长。同步逻辑电路

中每个时钟脉宽都是相等的,为了保证每次比较都能得到正确的输出,这个时钟脉宽

应该大于比较出最小输入的脉宽。由逐次逼近的原理可知,比较器的输入会逐渐减小,

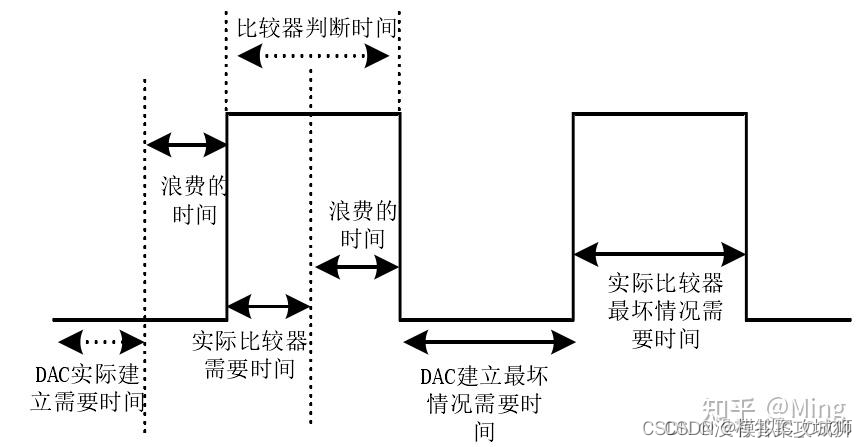

如果使用同步逻辑电路,转换在比较器输入大于 1LSB 时均有时间的浪费。

同步SAR逻辑限制

同步控制逻辑是指时钟控制信号SAR ADC内部DAC电容阵列模块和比较器模块的工作频率是采样频率的N倍,这就意味着需要在片外产生一个高频时钟控制信号并输入片内使其正常工作。这在会提升片外电路的设计难度的同时,也会增加高频信号对片内系统的信号传输干扰。是由外部产生并且输入到芯片内部。

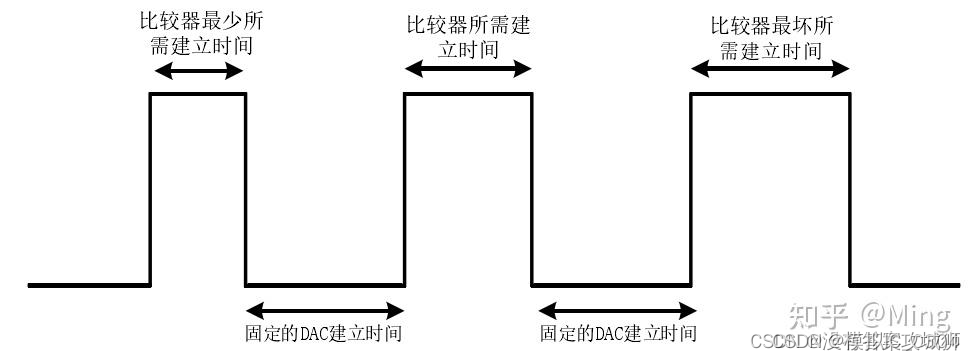

同步数字逻辑架构时序分配,其时序频率由两方面组成:一是比较器的传输延时,它与输入信号大小有关,输入信号幅值越大,比较器传输延时越小,反之越大;二是DAC 阵列建立时间,它由 RC 常数决定,CDAC最高有效位电容最大,其电压建立时间也越长。 同步数字逻辑的时序充分考虑上述两方面的原因,最大的工作频率是由上述两者最坏的情况所限制,因而同步数字逻辑会有很大部分的时序被浪费,因此提出了异步SAR逻辑。

同步SAR浪费的时间

三、异步SAR逻辑

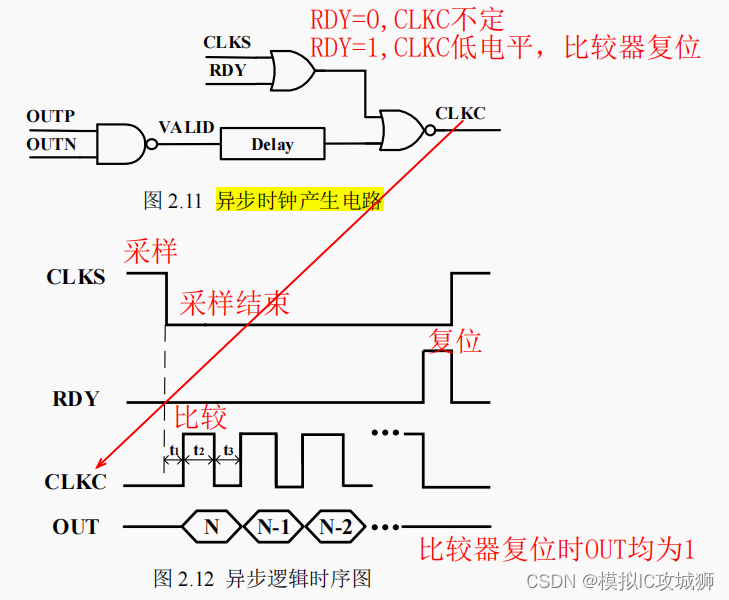

异步SAR逻辑时序图

所谓的异步控制逻辑,即为时钟控制信号通过电路内部生成的低频信号基于组合逻辑进行分析处理,而产生能够符合DAC电容阵列模块和比较器模块的工作频率的 高频时钟控制信号,这样就可以避免外部高频控制信号输入而对内部电路产生干扰。

对于SAR ADC,因为比较器正反相输入端的输入信号与DAC阵列P、N输上极 板电压的电压差不同,所以各位电容经过比较器的输出延时也有所不同。电压差值越 大,则比较器产生输出的时间越短。同步时序的每个比较周期都设定为比较器输出结 果的最大延时,所以导致转换速率较低,采用同步时序的SAR ADC采样频率通常小 于5MHz。而异步时序的基本原理则是,在每个比较周期完成后,将通过异步逻辑控 制生成反馈,然后立即进入下一个比较周期。这种操作可以通过使每个比较周期所用 时间降低,减少不必要的时间浪费,而达到提高整体ADC转换速率的效果,同时简 化了所需要的外围电路,降低的整体系统的功耗。

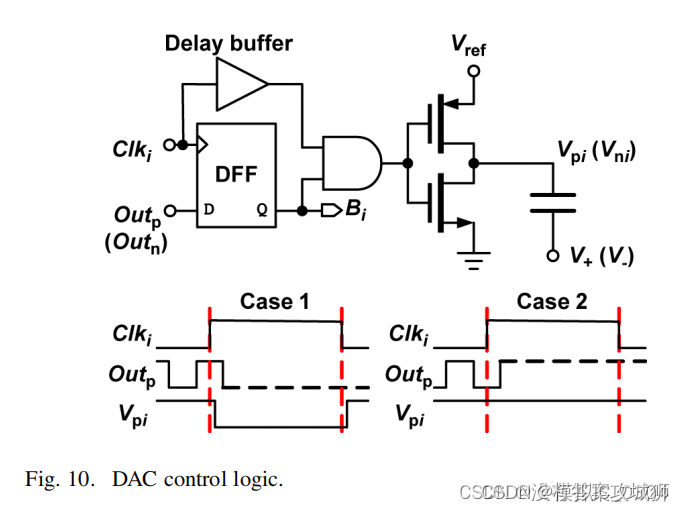

delay buffer 保证CLKi在Bi采集到比较器输出OUTp之后触发与门。

SAR ADC 详细介绍

SAR ADC详细介绍传送门

5095

5095

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?