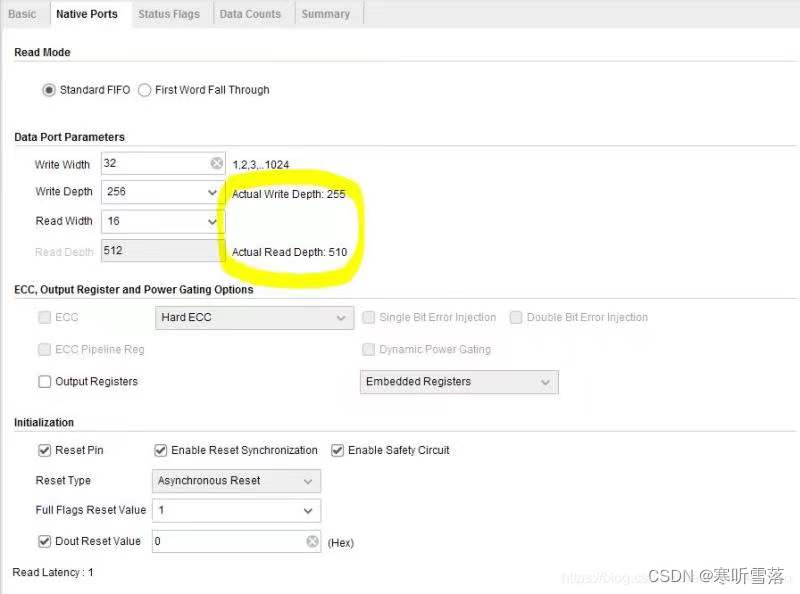

1,XILINX的FIFO,不同带宽输入输出,输出时,默认是先输出高位,再输出低位。这个能不能设置?先输出低位再到高位?答:在写入的时候,切换下位置就行了。

2,zynq7020 fpga启动了,但是ps没反应,ps灯不闪烁,程序直接ram运行,ps正常。

后续解答

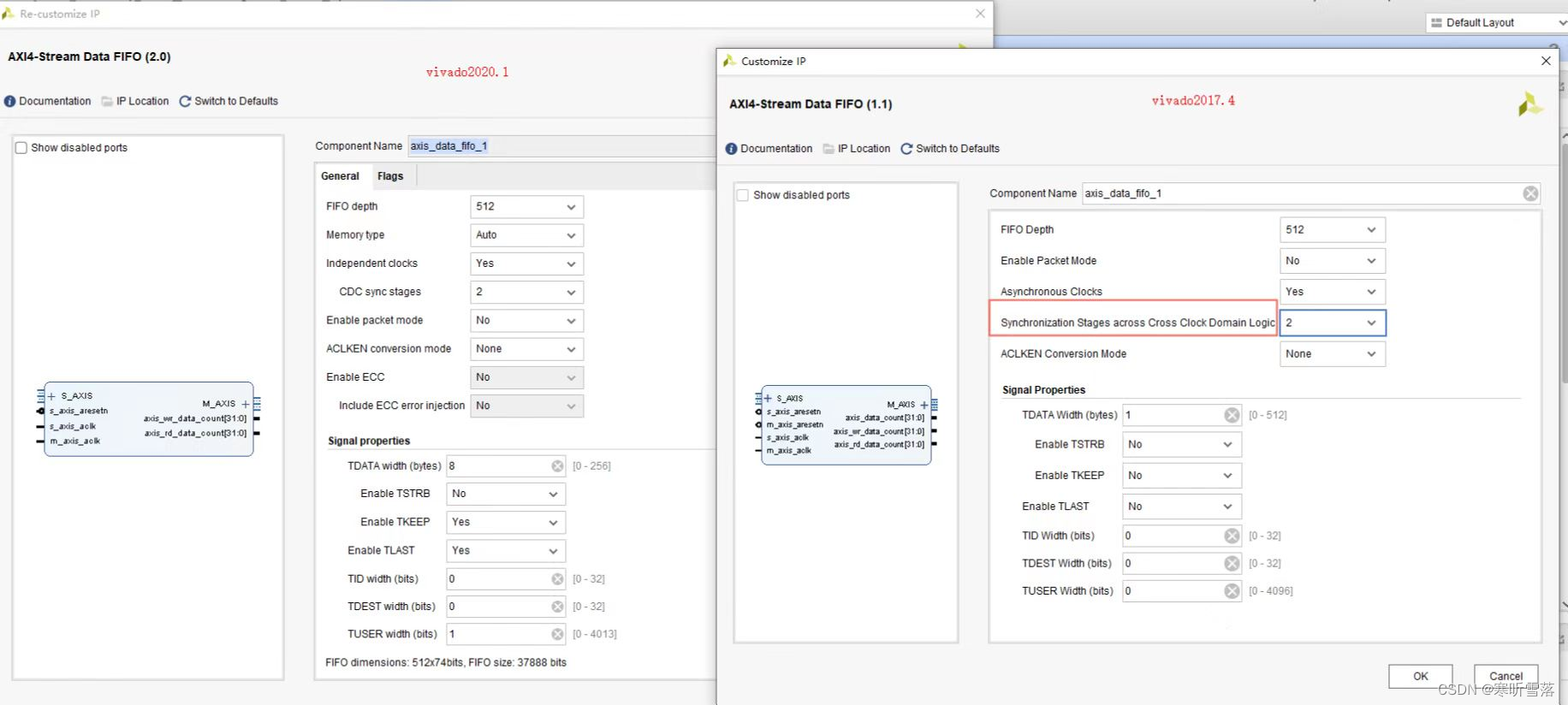

3, FIFO这种复位时钟个数有什么要求?

同步就是一个、异部就是两个,xilinx的板子没什么差异

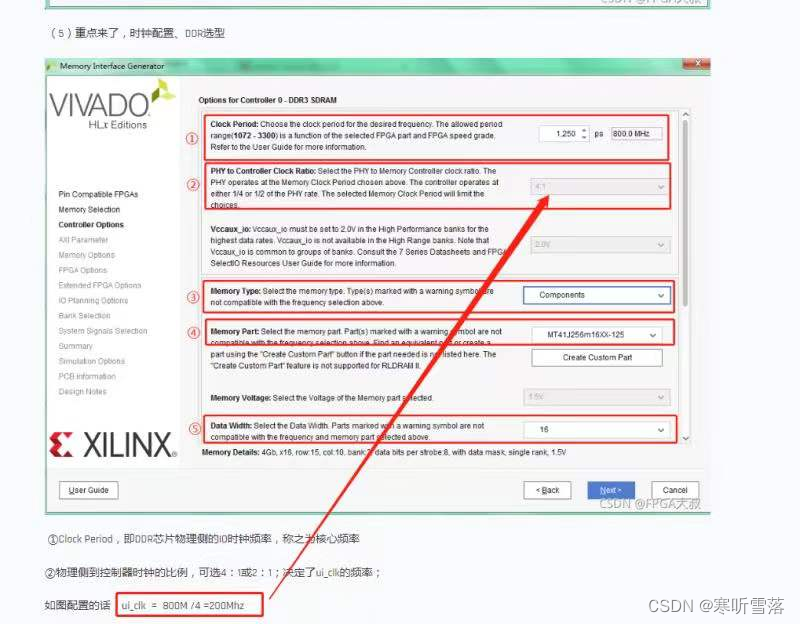

4, DDR3用什么运行频率?能不能用很低的频率让它工作呢?

K7的DDR可以跑到800M,用户逻辑可以跑到200M。

5,PS的以太网用emio经过gmii转rgmii后Txclk变成了2.5Mhz,而用mio输出则是125Mhz。

6,uiudp_stack这个协议栈能使用MDIO吗?不能

uiudp_stack这个协议栈,我的phy协商的是100M,协议栈能正常工作吗?现在app_tx_ack这个信号没有拉高。100m, rgmii不能工作,协议栈能正常工作。

569

569

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?