一直以来对zynq的结构和概念都不是很清楚,今天老师特地给我讲解了一番,收获巨大,特地记下。

Zynq是指一款芯片,xilinx推出的Zynq-7000 All Programmable SoC系列,将ARM与FPGA结合起来。

以上是Zynq的架构,主要分为PS和PL两部分。PS部分可以看成一个集成在内部的ARM芯片,该ARM芯片基于Cortex-A9双内核,内部有GPIO(MIO,EMIO),UART,I2C,SPI,SWDT,TTC等一切ARM芯片都有的模块。DDR2/3控制器也被集成到了ARM内部。PS端内部使用AXI3、AHB、APB等总线,颜色与总线名称相对应。PL部分就是FPGA了,有XADC,GTX等模块,其他就是逻辑资源了。

PL与PS之间通过AXI总线连接,有32位的通用AXI主从端口,有32/64位高性能从机端口以及64位的ACP从机端口。

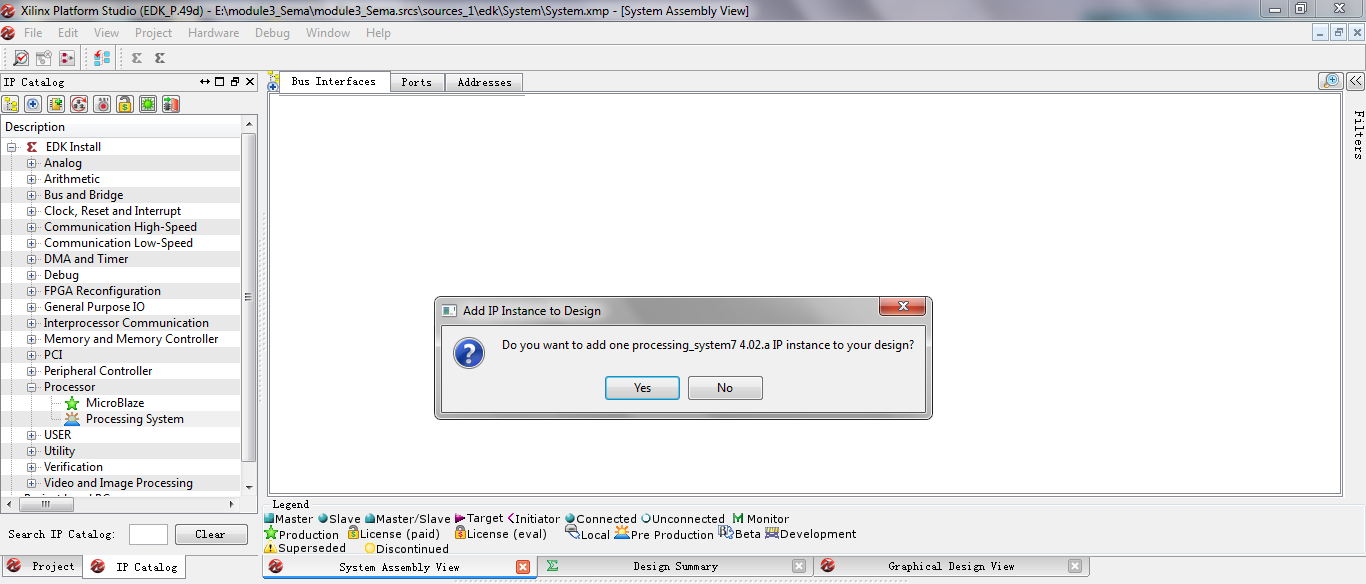

还有processing_system7_0。它本质上是一个IP核,新建工程时算是默认选项。可以认为processing_system7_0=PS+PL。因为把它删掉后,Zynq的标签页也就没了。在IP核目录中,它属于processor处理器一类。

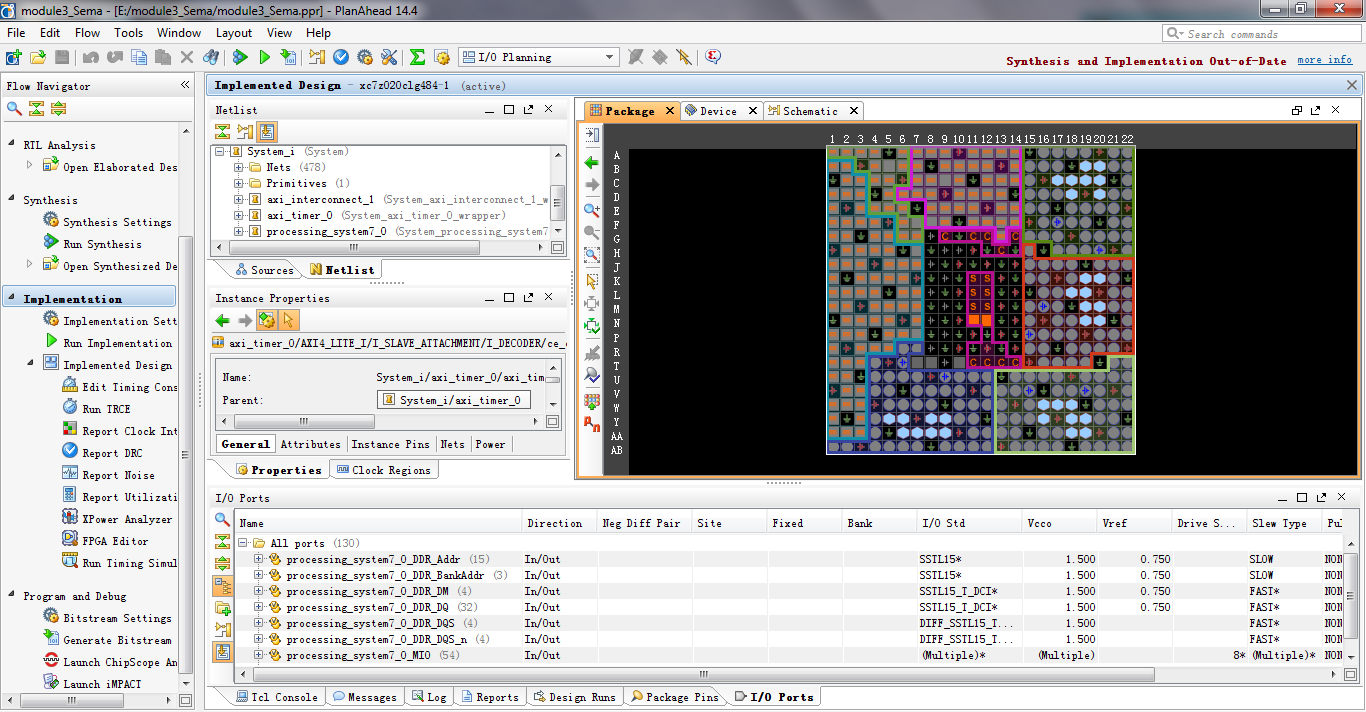

我们再从FPGA的角度看看Zynq。在PlanAhead中Open Implemented Design,右上Package一栏显示的是IO引脚使用情况,Device一栏则是内部资源使用情况。

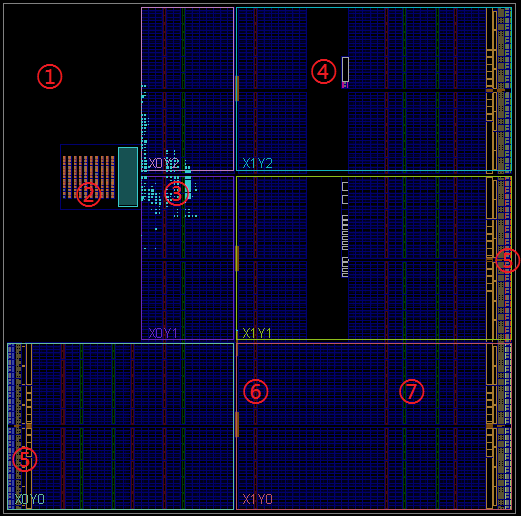

单击Device,放大。下图中,左上侧1黑的部分就是PS部分,2是PS端的引脚。其他就是FPGA部分了,FPGA按坐标分为X0Y0,X0Y1,X0Y2,X1Y0,X1Y1,X1Y2六大部分。3绿色的点状部分是使用的资源。4是XADC。5是IOB引脚部分。6是BRAM,7是DSP。

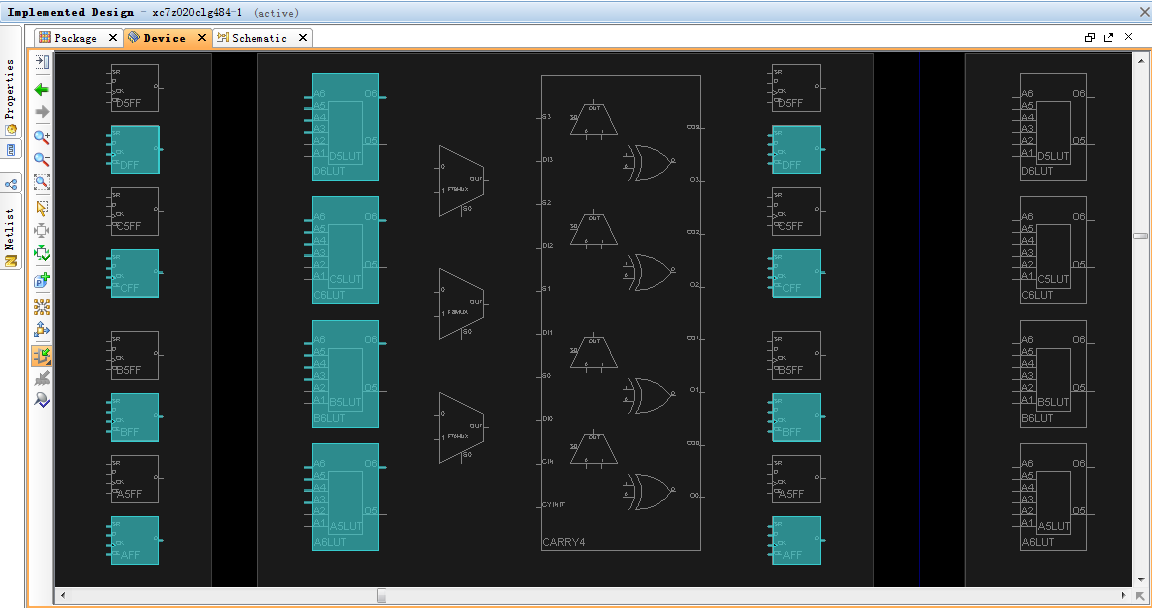

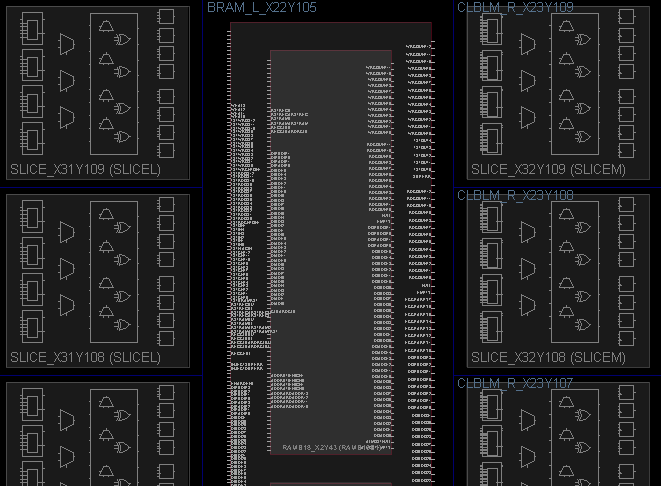

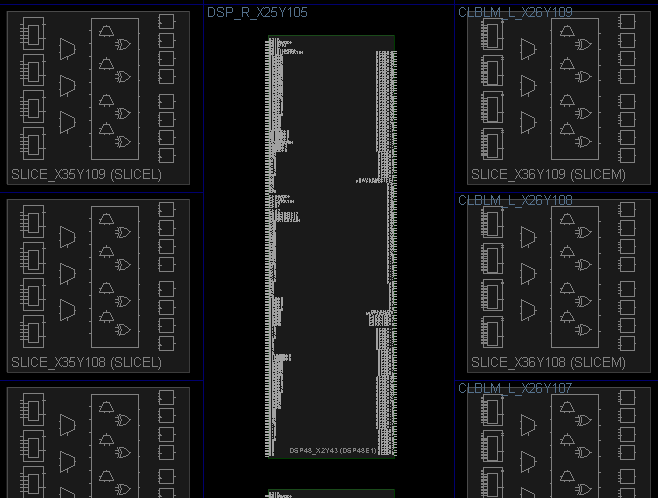

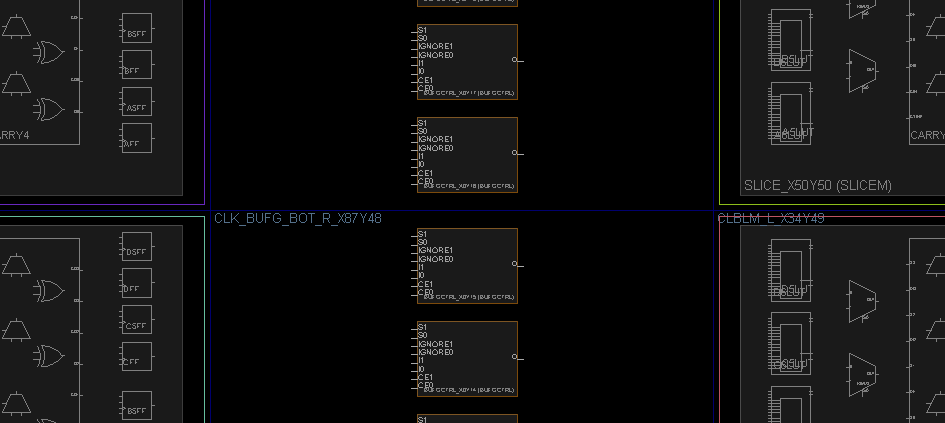

放大看一下FPGA的内部结构。最小的单元是Slice,它组成了FPGA中的基本单元CLB(Configurable Logic Block,可配置逻辑块)。每个Slice内部包含4个LUT(查找表)、4个触发器、多路开关及进位链等资源。部分Slice还包括分布式RAM和32bit移位寄存器,这种Slice称为SLICEM,其他Slice称为SLICEL。CLB内部的两个Slice是相互独立的,各自分别连接开关阵列(Switch Matrix),以便与通用布线阵列(General routing Matrix)相连。MUX是二选一多路选择器。Carry是快速进位链,由MUX和与非门组成。再后面就是D触发器。

Slice中间有一竖条Block Ram。

神奇的是还有一竖条DSP。

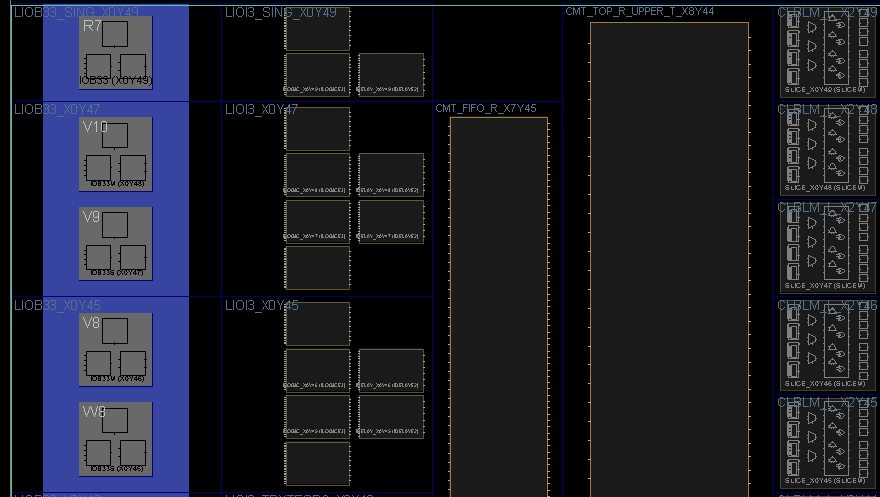

左下边和最右边是IOB可编程输入输出单元、FIFO等各种模块。最边沿加颜色的部分就是FPGA的引脚。

两个坐标之间有bufhce,充分利用BUFGMUX,BUFGCE和BUFHCE可用于降低功耗。

227

227

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?