前言

本节主要是介绍 Xilinx DDR 控制器 IP 的创建流程、IP 用户使用接口 AXI 协议介绍和IP 对应的 Example Design 的仿真和上板验证。

提示:以下是本篇文章正文内容,下面案例可供参考

三.DDR 控制器 Example Design 生成

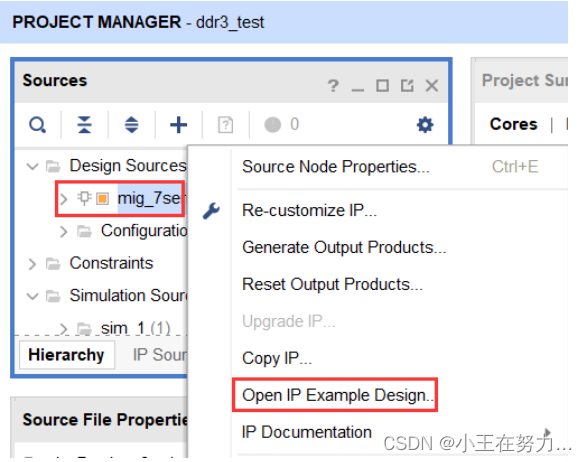

IP 核生成完成后,在 Sources 窗口找到 IP 核选中鼠标右键点击 Open IP Example Design。

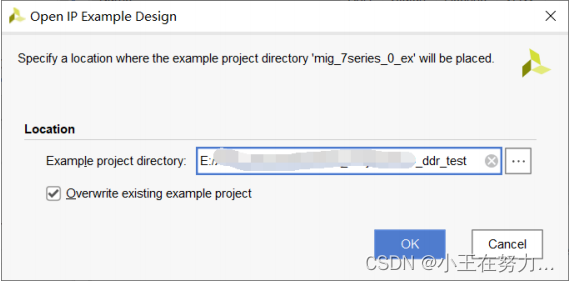

出现弹窗,设置选择生成 Example Design 的路径,这里将其设置为建立工程的目录。

点击 OK。会自动生成和打开名称为 mig_7series_0_ex 的工程。

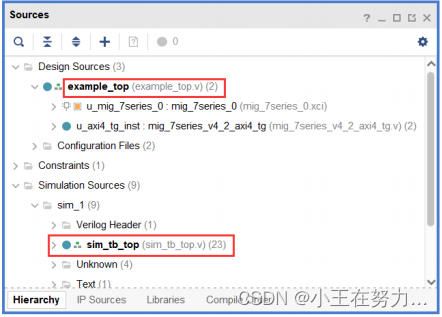

在自动打开 mig_7series_0_ex 工程的 Source 窗口可以看到生成的设计顶层 example_top和仿真顶层 sim_tb_top。

这个工程是可以直接进行仿真看波形和进行上板测试的。

四.DDR 控制器 Example Design 仿真

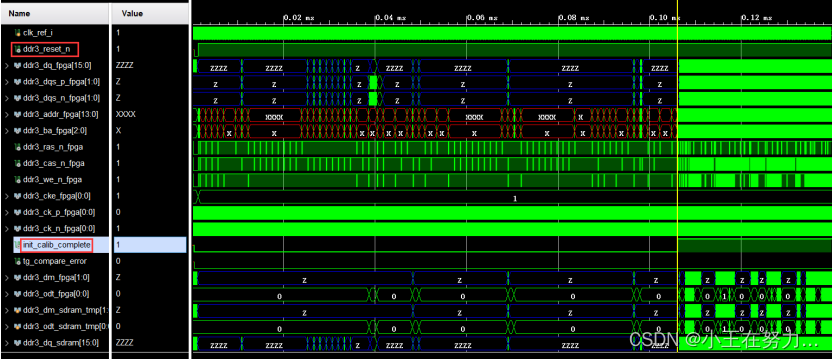

对于验证 FPGA 与 DDR 接口硬件设计能否正常工作很有用。在左侧边栏 SIMULATION 下点击 Run Simulation,选择 Run Behavioral Simulation 点击可直接进行仿真。整个仿真过程需要一点时间,在仿真结束后,可以看到整个的仿真波形。

在仿真大概 0.1ms 后,init_calib_complete 信号被置高,说明这个时候对 DDR3 存储器初始化和校准已经完成。之后是往 DDR3 里写入/读出数据,通过比较同一地址写入和读出的数据是否相等验证其功能的正常。

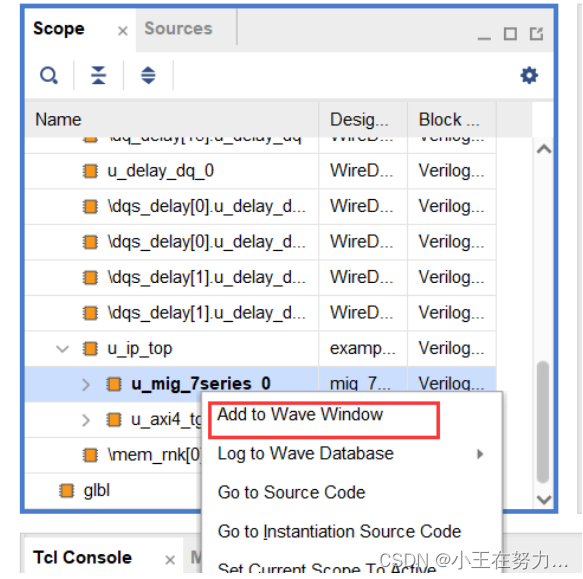

为了能观察用户侧的 AXI 接口的控制信号的波形,将 AXI 接口的波形添加到波形窗口。

重新跑仿真,先点击 Restart(建议多点击几次 Restart,有时只点击一次后就点击 Run All 跑仿真会出现新添加的信号没有波形),再点击 Run All。

重新跑仿真,先点击 Restart(建议多点击几次 Restart,有时只点击一次后就点击 Run All 跑仿真会出现新添加的信号没有波形),再点击 Run All。

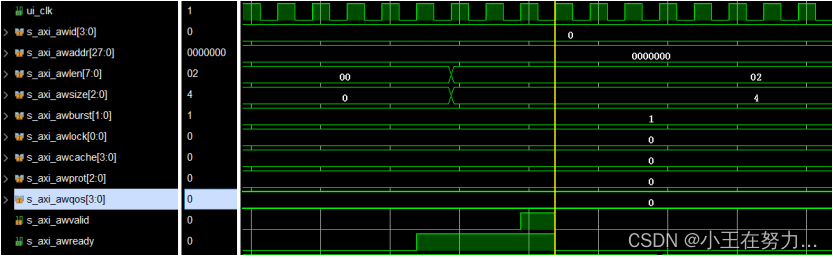

仿真结束后,随便找一处写操作过程 AXI 总线信号的变化情况。写地址通道的波形如下。这次突发写操作的起始地址是 0,突发长度是 3(等于 awlen+1),每个数据的字节数为16(等于 2awsize = 24字节),即数据位宽为 128bit,这个与我们 IP 配置 AXI 接口的数据位宽是一致的。

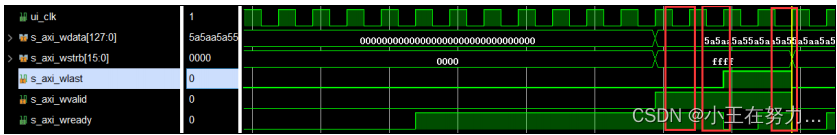

观察本次突发写操作的的写数据通道的波形如下。

写数据通道写入了 3 个数据,wvalid 和 wready 同时为高表示写数据有效,当写最后一个数据的时候wlast、wvalid 和 wready 是同时为高的。wstrb 等于 16’hffff,表示写入的 16 个字节全部有效。

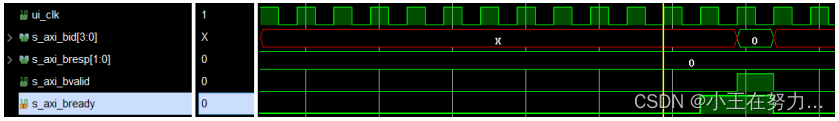

观察本次突发写操作响应通道的波形如下。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

8607

8607

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?