内容提要

- ready打拍的问题

- 用FIFO的思路去解决

- 用Buffer的思路去解决

问题提出:ready时序如何优化?

在valid/ready 握手协议中,valid 与 data的时序优化比较容易理解,(不熟悉valid/ready协议或者valid打拍方法的)大家可以参考上次推送(握手协议(pvld/prdy或者valid-ready或AXI)中Valid及data打拍技巧)。 但是有时候,关键路径是在ready信号上,如何对ready信号打拍呢?

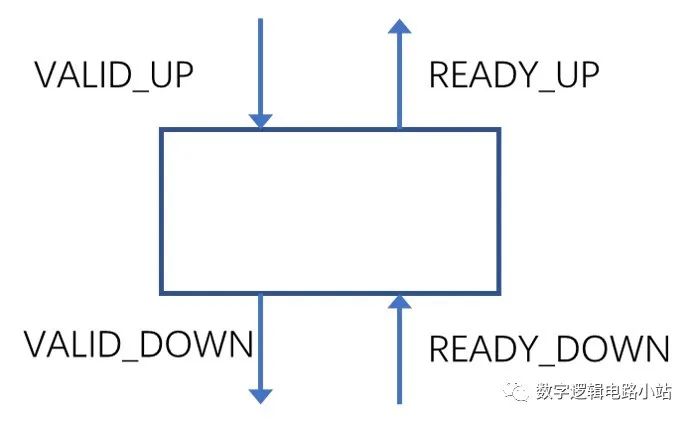

首先将把目标设计想象成一个黑盒子,如图1所示,我们的目标是将READY_DOWN通过打拍的方法获得时序优化。

(图1)

尝试直接对ready打一拍

READY_UP <= READY_DOWN;

VALID_DOWN = valid_up;

(仅示例,非verilog代码。下同)

这样是行不通的。

一个简单的例子(case 1)就是你让READY_DOWN像一个时钟一个,间隔一个cycle起来一次,那么VALID_UP && READY_UP 与 VALID_DOWN && READY_DOWN无法同步,数据无法传输下去。

思路:将其分解成两个interfaces

将ready打拍的逻辑想象成一个黑盒子,去分析这个黑盒子的设计,分为up interface 和down interface将问题细化:

- up interface 有VALID_UP, DATA_UP, READY_UP

- down interface 有VALID_DOWN, DATA_DOWN, READY_DOWN 可以总结成下面的样子:

READY_UP <= READY_DOWN; //or READY_UP = function(READY_DOWN_next);

transfer_up = VALID_UP && READY_UP;

transfer_down = VALID_DOWN && READY_DOWN;

如果去解决刚才例子(case 1),那么这个黑盒子:

当READY_UP为高的时候,可以接受数据; 当READY_DOWN为高的时候, 如果我们有数据可发的话,我们可以向downstream发送数据;

是不是很像一个FIFO?

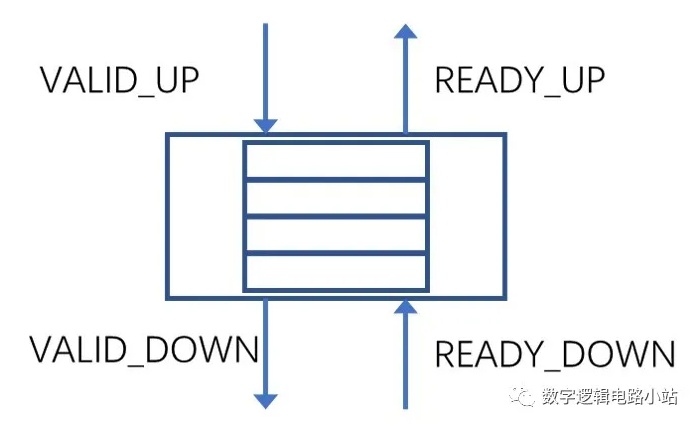

用FIFO去解决

将一个FIFO插在黑盒子这里,那么就会变成这样子:

(图2)

VALID_UP/READ_YUP ==> FIFO ==> VALID_DOWN/READY_DOWN

也就是:

VALID_UP = fifo_push_valid;

READY_UP = fifo_push_ready;

VALID_DOWN = fifo_pop_valid;READY_DOWN = fifo_pop_ready;

现在问题变成了:如何设计这个FIFO呢?

- 这个FIFO深度多少?

- 怎么设计,能够保证READY_UP是READY_DOWN打过一拍的呢?

FIFO设计多深?

因为本身valid/ready协议是反压协议(也就是READY_UP为0的时候,不会写F

本文探讨了在AXI协议中优化ready时序的方法,通过将问题分解为两个接口并引入FIFO,解决了ready打拍的挑战。详细讨论了FIFO的深度、无气泡传输和FIFO穿越等概念,提供了实现ready时序优化的方案。

本文探讨了在AXI协议中优化ready时序的方法,通过将问题分解为两个接口并引入FIFO,解决了ready打拍的挑战。详细讨论了FIFO的深度、无气泡传输和FIFO穿越等概念,提供了实现ready时序优化的方案。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?