任意进制计数器 || 反馈复位法 反馈置数法 || 超级重点 || 数电

前面介绍了4位二进制计数器和十进制计数器,但它们的计数长度、计数方式是固定的。

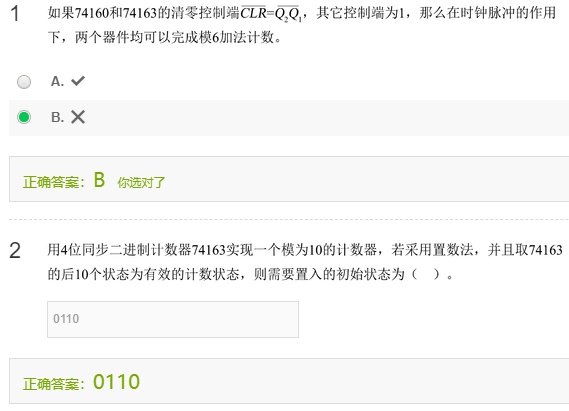

例如:

- 十进制计数器74160,其计数的模为10,计数方式为加1计数,从0000开始,每个时钟脉冲加1,直到1001,即十进制数9,然后再回到0000。

- 4位二进制计数器74161或者74163,其计数的模为16,计数方式为加1计数,从状态0000开始,每个时钟脉冲加1,直到1111,即十进制数15,然后再回到0000。

但在数字电路应用中,需要用到计数长度任意,计数方式非顺序递增或递减的计数器,我们把这种计数器叫做任意进制计数器。

本文将介绍如何利用已有的集成计数器,通过外电路的不同连接,设计任意进制计数器。

任意进制计数器的设计方法有两类:

- 反馈复位法(清零法)

- 反馈置数法

1反馈复位法

1.1异步清零 反馈复位 74160

以例子来介绍,

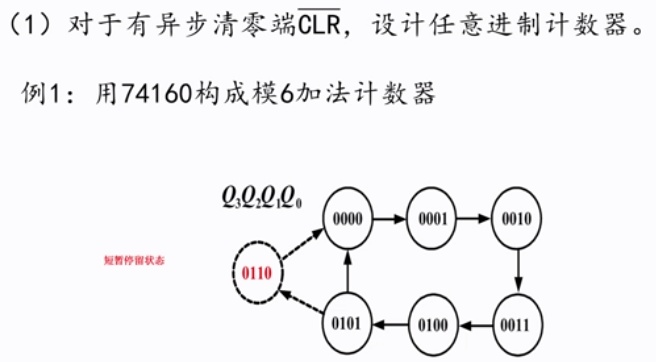

用带有异步清零端的十进制计数器74160构成模6加法计数器,设计思路是:

假设计数器74160从初始状态Q3Q2Q1Q0=0000开始计数,

接收到第1个时钟脉冲后状态变为0001,

接收到第2个时钟脉冲后状态变为0010,

接收到第3个时钟脉冲后状态变为0011,

接收到第4个时钟脉冲后状态变为0100,

接收到第5个时钟脉冲后状态变为0101,

接收到第6个时钟脉冲后状态变为0110,如果此时利用状态0110,通过组合电路产生异步清零信号,并反馈到74160的清零端,于是计数器尽在状态0110短暂停留后就立刻复位到0000状态,这样,就跳跃了计数器74160的4个状态,而获得了6进制计数器。

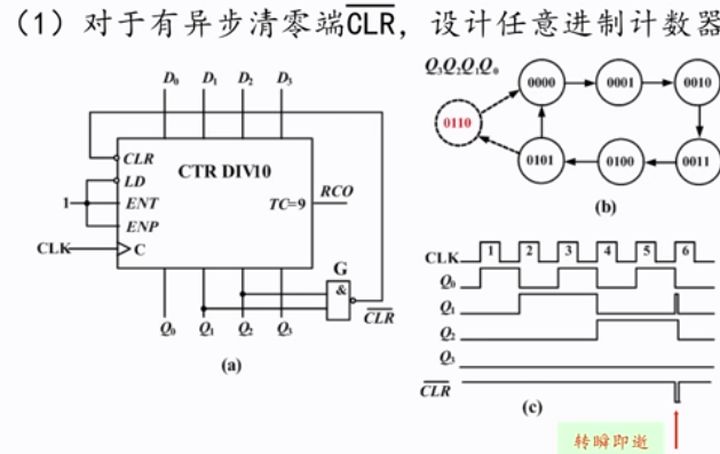

根据前面的设计思路,我们只需要附加1个与非门,与非门的输入为计数器状态Q2和Q1,与非门的输出连到计数器的异步清零端,如下图(a)所示。但是清零时Q3Q2Q1Q0不一定会同时变为0000,可能会产生中间状态,使得清零不可靠,所以可以使用一个RS锁存器来改进清零电路。如下下图所示。

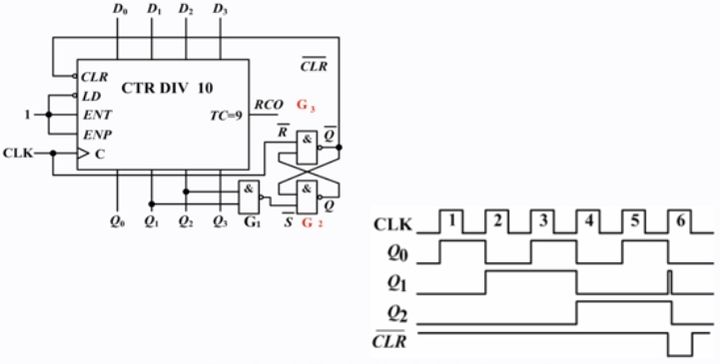

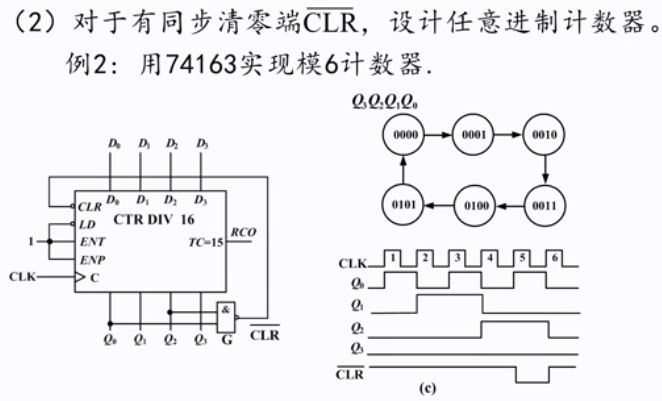

1.2 同步清零 反馈复位 74163

这里的反馈状态是0101(5)而不是之前的0110(6)。注意体会同步清零和异步清零的区别。

对于上图,设计数器的初始状态为Q3Q2Q1Q0=0000,

第1个时钟脉冲到来后,状态变为0001,(CLR非)为高电平,

第2个时钟脉冲到来后,状态变为0010,(CLR非)为高电平,

第3个时钟脉冲到来后,状态变为0011,(CLR非)为高电平,

第4个时钟脉冲到来后,状态变为0100,(CLR非)为高电平,

第5个时钟脉冲到来后,状态变为0101,导致(CLR非)变为低电平,但清零并不马上发生,

因为74163是同步清零,要等到第6个时钟脉冲到来后,清零才生效,使计数器状态变为0000,然后(CLR非)回到高电平。

我们可以发现这种采用同步清零的反馈法,不会出现短暂的过渡状态。

2反馈置数法

反馈置数法是利用计数器的同步置数控制端的数据输入端,把计数器状态置到某个数值来实现任意进制计数器。

置入的数值可以是0000到1111之间的任意数值。

当置入0000时,和复位或者清零的作用是相同的,因此这种方法比第一种反馈复位法灵活性要大。

如下图,现在我们还是用一个例子来介绍这种方法。

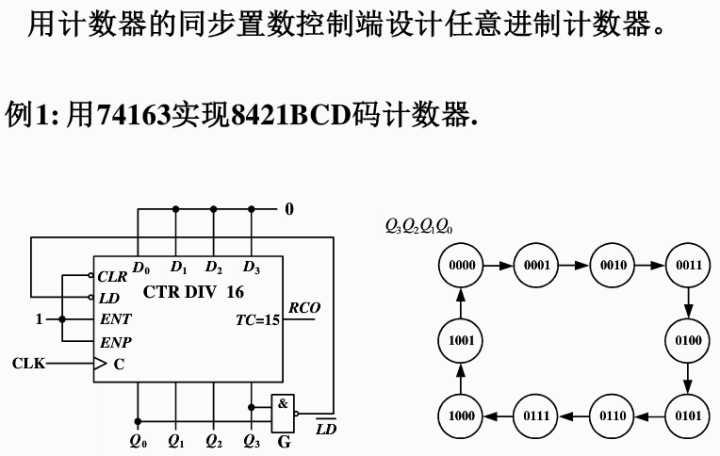

用带有同步置数控制端的74163构建8421BCD码计数器。

设计思路是:

假定计数器初始状态为Q3Q2Q1Q0=0000,

一开始让计数器正常计数,计到1001后,通过置数使计数器在下一个状态进入0000,跳过1010~1111这个状态。

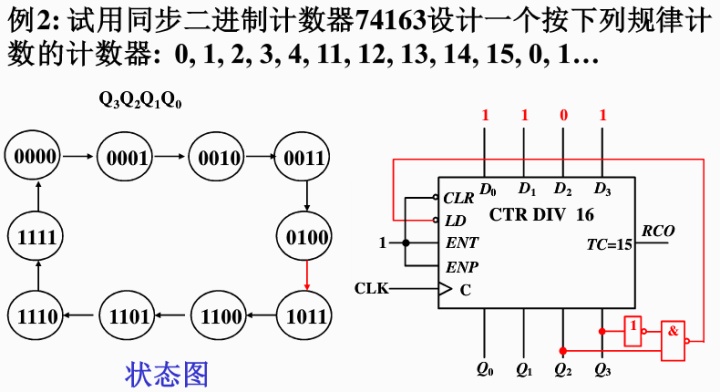

如下图,再看一个例子,很好理解了吧。

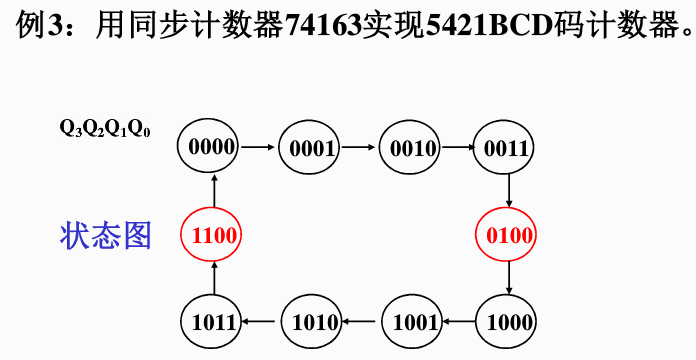

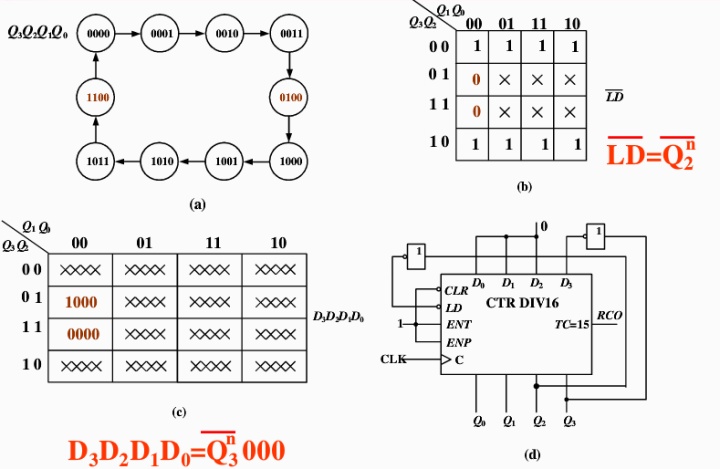

再看一个。

下面解答使用的方法是两次置数。

3采用多片集成计数器设计任意进制计数器

步骤:

- 根据待设计任意进制计数器的模,确定集成计数器所需要的数量,并进行级联。

- 用前面学习的反馈复位法或者反馈置数法完成任意进制计数器设计。

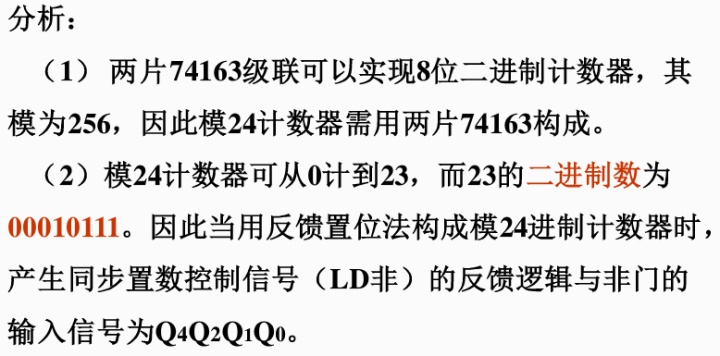

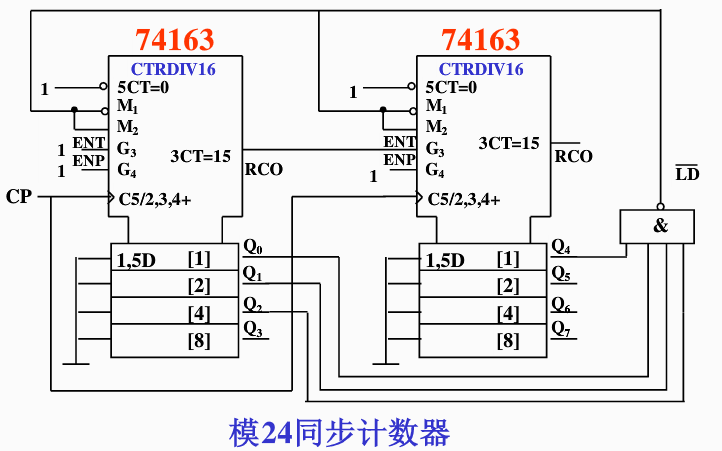

下面看一个例子,试用74163构成模24同步计数器。

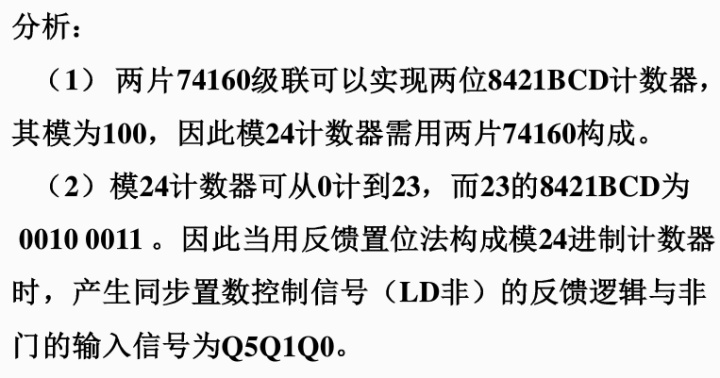

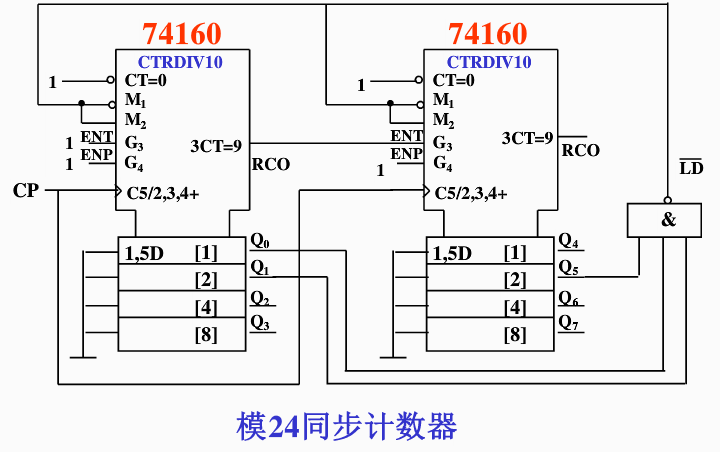

下面再看一个例子,使用74160构成模24同步计数器。

丢题目,

视频:MOOC-数字逻辑电路-第9单元 时序逻辑功能-任意进制计数器

本文介绍了如何利用反馈复位法(清零法)和反馈置数法设计任意进制计数器。通过74160和74163为例,详细阐述了异步清零与同步清零的区别,并通过实例展示了如何避免过渡状态,以及反馈置数法的灵活性。

本文介绍了如何利用反馈复位法(清零法)和反馈置数法设计任意进制计数器。通过74160和74163为例,详细阐述了异步清零与同步清零的区别,并通过实例展示了如何避免过渡状态,以及反馈置数法的灵活性。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?