【问题描述】

在使用Verilog对硬件逻辑进行建模和模拟的同时,必须理解代码与硬件实现的联系和Verilog语言本身的语法规则,如果对于这些理解不够,往往会造成代码调试周期延长,更有甚者造成电路逻辑功能异常的情况出现,从而拖延电路设计的周期。本文列举的错误不仅初学者经常遇到,在一些经验丰富的电路设计人员中也经常会出现这些问题,为此,本文以尽量浅显易懂的方式及示例展示这些常见的问题,希望对于广大有需要的朋友提供一些力所能及的帮助。同时,希望大家在完成必要的编码之后能够对编写的代码进行代码规则检查,目前常用的代码规则检查工具有:SpyGlass(Synopsys)、Leda(Synopsys)、HAL(Cadence)等,同时这些工具中还集成了大量的业界标准规则集,可以通过这些EDA工具对于设计代码进行比较全面的检查,为后续电路的仿真及实现提供必要的帮助,可以极大地缩短研制周期。

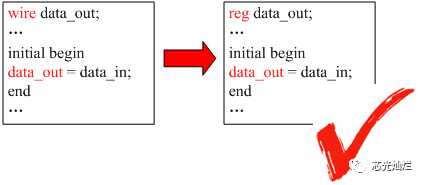

【问题一】

过程性赋值语句左侧信号没有声明为reg或者logic类型,而是声明为了线网类型,例如:

【问题二】

使用begin-end没有配对使用,导致语句执行与预期不相符,特别是在条件表达式中,例如:

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

923

923

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?