概述

高层次综合设计最常见的的使用就是为CPU创建一个加速器,将在CPU中执行的代码移动到FPGA可编程逻辑去提高性能。本文展示了如何在Zynq AP SoC设计中使用HLS IP。

在Zynq器件应用Vivado HLS IP

这里集成了HLS IP和由HLS创建的软件驱动,目的是控制在Zynq器件上实现的IP设计。

Step 1: 创建Vivado HLS IP Block

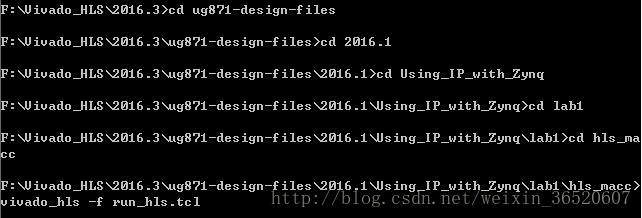

脚本完成时,会生成vhls_prj文件,里面包含HLS IP,下面介绍Vivado HLS IP blocks如何被集成到使用IP Integrator的Zynq器件中。

Step 2: 创建 Vivado Zynq Project

1.打开vivado 2016.3,点击Create New Project,选择Using_IP_with_Zynq\lab1路径,下一步在Project Type页面选择RTL Project和Do not specify sources at this time

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

9777

9777

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?