PCB的pin数反映了设计的复杂程度,在外包时有时也会按pin脚算设计费用。

查看pin数的两种方式:

1、原理图

Cadence原理图查看PIN总数_cadence统计pin数-CSDN博客

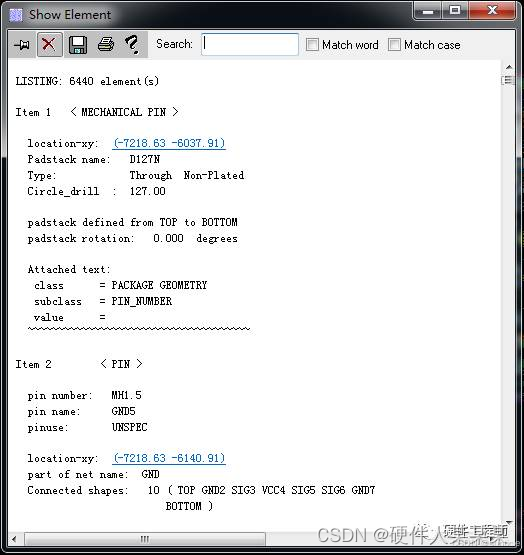

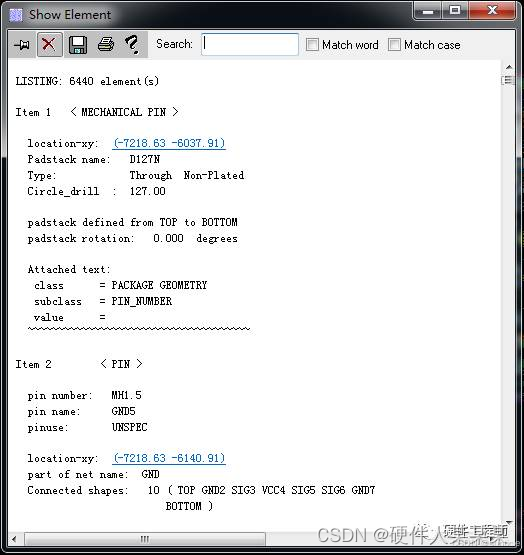

2、PCB(推荐)

Cadence Allegro如何查看PCB PIN脚数量-百度经验 (baidu.com)

PCB的pin数反映了设计的复杂程度,在外包时有时也会按pin脚算设计费用。

查看pin数的两种方式:

1、原理图

Cadence原理图查看PIN总数_cadence统计pin数-CSDN博客

2、PCB(推荐)

Cadence Allegro如何查看PCB PIN脚数量-百度经验 (baidu.com)

2106

2106

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?