ICC2时钟树综合从入门到精通

文章右侧广告为官方硬广告,与吾爱IC社区无关,用户勿点。点击进去后出现任何损失与社区无关。

最近小编分享了好多 Innouvs 的技术干货,比如如何查看 innovus timing report,如何在 innovus 分析 clock tree 质量,如何在 innovus 中做各种 Timing ECO 或 Function ECO 等等。今天小编打算再分享如何在 ICC2 中分析 clock tree 质量,希望能够帮助到有需要的朋友。

CTS(Clock Tree Synthesis)其实就是做一件事情,从时钟 root 点开始长 Buffer/Inverter tree 直至 sink 点。而 root 点是通过 create_clock 或 create_generated_clock 来告诉工具的,sink 点一部分是设计本身决定的,另外一部分是 user defined,它是通过约束文件告诉工具的。

当然,这个过程需要按照我们的要求来做,比如 clock skew,clock transition 等约束条件。

So,时钟树综合是不是超级简单?看懂上面这几句话,你就已经超越 80% 的数字 IC 后端工程师了!想要成为头部的 5%,你还需要继续认真看完今天剩下的内容。

Pre-CTS setup

在做时钟树综合前,需要预先检查哪些事项,可以参考之前分享的这篇文章,这里就不再重复了。

时钟树综合 (Clock Tree Synthesis) 之前应该做好哪些工作?

CTS Command

ICC2 中做 tree 的命令是 clock_opt -to build_clock,ICC 可以用下面两种方式来做。这个之前也介绍过无数次了,不懂的可以翻阅以前的文章温习下。

-

clock_opt -only_cts

-

optimize_clock_tree

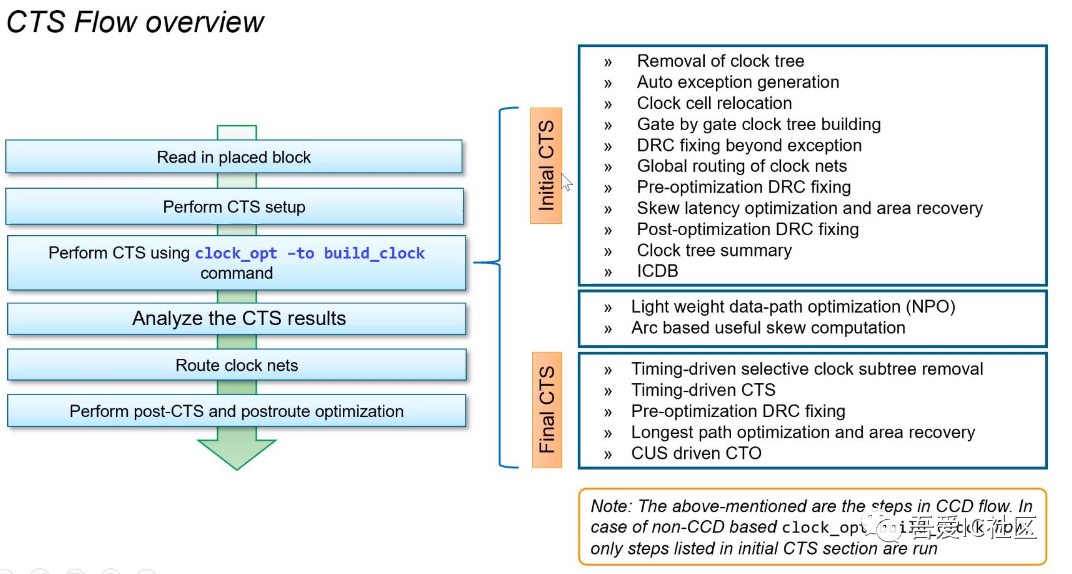

CTS 各子步骤

ICC2 中时钟树综合所包含的子步骤如下图所示。对于 non-CCD flow,整个 CTS 只包含 Initial CTS。对于 CCD 的应用场景和使用方法可以查阅小编知识星球上的这份培训教程(基于 ARM CortexA53 CPU 实现教程)。

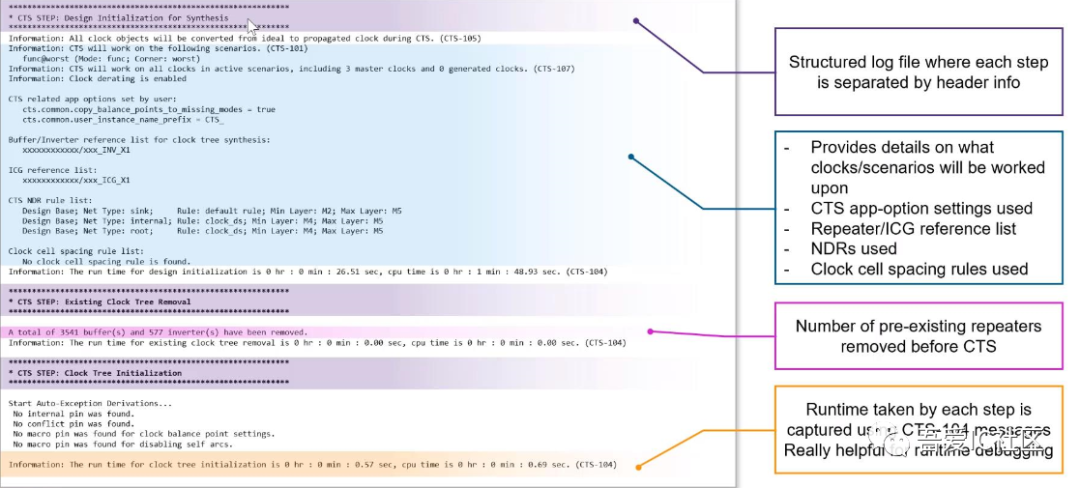

*** CTS STEP: Design Initialization for Clock Synthesis**

这步工具会报出 user 设置的一些参数。主要有下面几种:

-

用哪个 corner 来做 tree

-

可用于长 tree 的 buffer/inverter 类型

-

clock tree 上 ICG 可用的类型

-

clock net ndr

-

clock cell spacing rule

-

cts 相关的 app option

通过这些信息,我们可以来检查我们所有的 cts setting 是否全部被工具认到。经常有小伙伴们问到,为何 clock inverter 都指定了,但是做 tree 的过程就报no usable clock buffer/inverter呢?如果你认真看这部分 log,相信你能很快找到答案(提示:lib 相关)。

*** CTS STEP: Existing Clock Tree Removal**

这步顾名思义就是工具在长 tree 之前会将设计中已经存在的 clock tree 删掉。为什么要这么做呢?这就像同事交接一个 block 给你,可是只 release 一颗 place 后的 database,请问你会真的从 cts 开始做吗?是不是最多从 place 开始做起呢?虽然打的比方不是很恰当,但小编相信你懂的。

【思考题】 综合阶段为何不需要长 tree,不需要看 hold time?

***** CTS STEP: Clock Tree Initialization****

这步工具主要检查时钟树结构本身的问题。仔细看下图中这个步骤还可以看到这步工具所消耗的时间也会列出来,这个也可以提供 debug 用。

*** CTS STEP: Clock Cell Relocation**

这步从 log 中经常能看到报出某些 cell 不能 move,这些 cell 主要是 clock tree 上的 cell,大部分都是 ICG。所以看到这样的 log 需要仔细检查这些 dont touch 属性是否真的需要,如果不是 user defined 的,放开让工具自动摆放可能效果会更好。之所以会做这一步是因为工具在 cts 时发现原来 place 摆放的 icg 位置可能不是最佳的,所以会对 icg 重新摆放(比如实现 un-common path 更短等)。

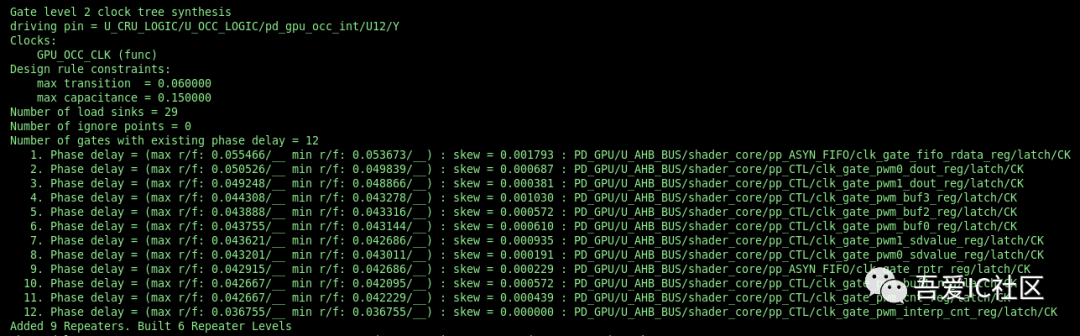

*** CTS STEP: Gate-By-Gate Clock Tree Synthesis**

这步类似于 Innovus 的 Clustering。Innovus 中支持单独做 clustering,便于快速 debug clock tree latency 是否合理。关于如何在 innovus 中快速得到 physical 和 logic max clock latency path,可以查阅这篇文章。

手把手教你如何在 Innovus 中分析 clock tree 质量

而 ICC2 小编目前好像没有看到这样的 option。如果 ICC2 也有这个 option,可以私信小编告知下。

根据上图的 gate by gate clock tree synthesis 信息,我们可以得到 AND0/X 后面带了两个 sink,分别是 FF0/CK 和 FF1/CK,长 tree 后工具在与门 AND0 后面插入了两颗 clock inverter。

如果 log 中提示有下图所示的 Number of gates with existing phase delay 为 12,请问这个代表什么意思呢?如果某个 phase delay 中存在一个 skew 比较大的点,请问这个信息给你的启示是什么呢?这些都是 debug clock skew 和 clock tree latency 非常有用的线索。

关于 clock skew 偏大的各种原因介绍,可以查阅上期推荐的文章。

盘点数字 IC 后端实现中 clock skew 大的各种场景

*** CTS STEP: DRC Fixing Beyond Exceptions**

这步工具会报出为了修这部分 Timing DRC 而加入了多少 clock inverter 和 buffer。

***** CTS STEP: Clock Net Global Routing****

做好时钟树后,为了让 clock skew 和 clock latency 更接近最终绕线后的值,工具会对 clock net 做下 global routing。

***** CTS STEP: Pre-Optimization DRC Fixing****

这步是基于 global routing 后再做的 DRC Fixing。报告中会报出 Global Skew 和 ID 等值。

【思考题】 如果这里发现 ID 值突然间增加 200ps,请问合理吗?为什么?如果不合理,请问有哪些原因会导致这种现象?

*** CTS STEP: Skew Latency Optimization and Area Recovery**

这步就是做 clock skew,clock latency 和面积优化的。这里会报告出工具每个 clock group 的clock skew,clock latency以及 timing drv 的情况。如果你仔细观察 log 会发现,CTS-037 都会报告 clock tree 的各种信息。因此,如果你想快速知道 clock tree 的信息,可以搜索 “CTS-037”。

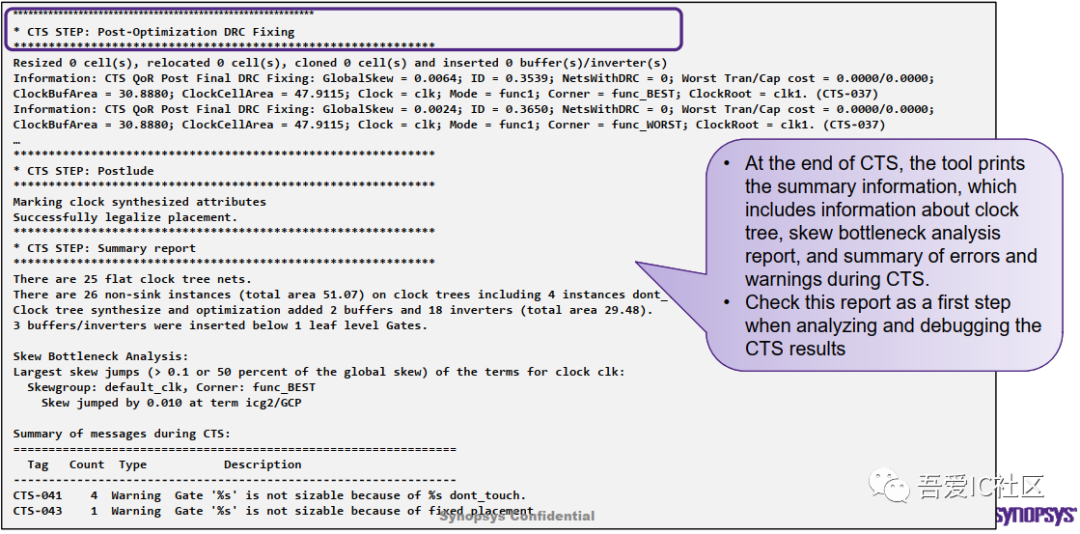

*** CTS STEP: Post-Optimization DRC Fixing**

这步工具继续做 DRC 修复,这个与 innovus 中的 log 也是比较像的。整个 cts 过程中有好多步骤都在做 drc fixing。

最后工具还出一份 summary report。这里面包含有 clock tree,clock skew bollteneck 分析以及 CTS 过程的错误和警告。这些信息都可以用来辅助分析 clock tree 质量的。

以上为整个 CTS 过程的详细 log 介绍,通过对每个子步骤的理解,我们可以快速从 log 中得知 clock tree 上可能存在的问题点。那么,如果发现某些点存在问题,那下一步应该怎么去 trace 找到 root cause 并解决掉问题呢?

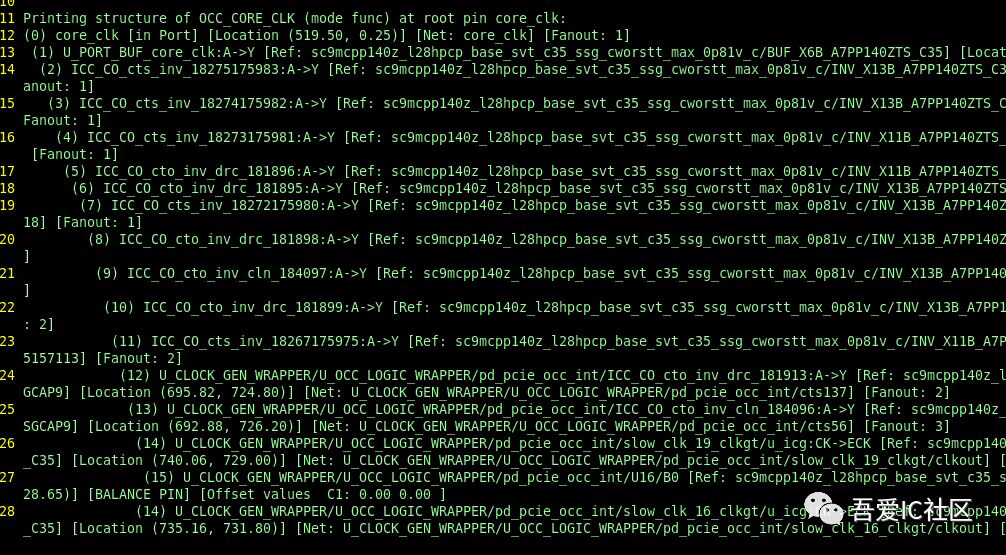

下面我们就得请出 clock tree debug 神器:clock tree structure。这个小编已经推荐过无数次了,相信社区的老铁们应该都能熟练应用了。

report_clock_qor -type structure > clock.structure.rpt

通过这个文件,可以很清晰得知各段时钟树是如何长的,经常可以用 ICC/ICC2 的 gui 和这个文件来协同 debug clock tree。比如可以在这个文件中搜索 clock tree 上有问题的点,进一步 trace 到根源问题。

通过 clock tree structure 文件,我们经常会看到cts_inv,cts_dlydt_inv等字样。这些带特殊关键词的 cell 名字是否有特殊的含义呢?答案是肯定的。具体含义见下图,熟悉这些规律后,能够大大提高 debug 的效率。

Innovus 中可以通过 show_ccopt_cell_name_info 来 list 各种关键词的含义。

时钟结构分析

大部分工程师可能也就停留在上面的这种分析方法。如果你想做的比别人要好,那么你需要将整个设计的时钟结构搞清楚,最好是将时钟结构图画出来。画出来后你就对每个时钟的走线就非常清楚,脑海里随时就能呈现出一种网络拓扑结构图。这样当发现 clock tree 上有一个比较异常的点的时候,就能立即定位到某段 tree 上。

下图为一个常见的时钟结构示意图。图中涉及到 CTS 的一些基本概念。什么是 ignore pin?什么是 stop pin 或 balance pin?什么是implict (explict)exclude pin?

想成为数字 IC 时钟树综合(clock tree synthesis)专家,建议好好看看这个!

这些基本概念需要非常熟练掌握。怎么验证你是否真的理解了这些概念呢?很简单,你自己不看任何参考资料,能够清晰地讲解给同事或者朋友听了,那就差不多了。

这里,需要重点提下两个地方。一个是对于output port来说,工具默认是ignore pin。因此,如果这类 port 是时钟的话,请一定要将其设置成 stop pin!另外一个是 ICG 的 CK 是 through pin 而非 stop pin。

针对上面这个案例,感兴趣的小伙伴可以利用 verilog 来写个这种时钟结构电路的电路,大家可以不用关心电路本身的具体功能,我们关心的是利用它来练习时钟树综合的技能。So,是不是有种到处都是案例的感觉!那就赶快行动吧!

好了,今天的内容分享就到这里。另外,因为公众号更改推送规则,小编分享的每篇干货不一定能及时推送给各位。为了避免错过精彩内容,请关注星标公众号,点击 “在看”,点赞并分享到朋友圈,让推送算法知道你是社区的老铁,这样就不会错过任何精彩内容了。

如果你想和小编有更进一步的沟通交流的机会,欢迎加入小编知识星球,让我们一起学习成长,共同进步。相信在这里能让你成就一个更完美的自己。

小编知识星球简介(如果你渴望进步,期望高薪,喜欢交流,欢迎加入 ****):

在这里,目前已经规划并正着手做的事情:

-

ICC/ICC2 lab 的编写

-

基于 ARM CPU 的后端实现流程

-

利用 ICC 中 CCD(Concurrent Clock Data)实现高性能模块的设计实现

-

基于 ARM 四核 CPU 数字后端 Hierarchical Flow 实现教程

-

时钟树结构分析

-

低功耗设计实现

-

定期将项目中碰到的问题以案例的形式做技术分享

-

基于 90nm 项目案例实现教程(ICC 和 Innovus 配套教程)

-

数字 IC 行业百科全书

吾爱 IC 社区知识星球星主为公众号” 吾爱 IC 社区” 号主,从事数字 ic 后端设计实现工作近八年,拥有55nm,40nm,28nm,22nm,14nm等先进工艺节点成功流片经验,成功tapeout 过三十多颗芯片。

这里是一个数字 IC 设计实现高度垂直细分领域的知识社群,是数字 IC 设计实现领域中最大,最高端的知识交流和分享的社区,这里聚集了无数数字 ic 前端设计,后端实现,模拟 layout 工程师们。

在这里大家可以多建立连接,多交流,多拓展人脉圈,甚至可以组织线下活动。在这里你可以就数字 ic 后端设计实现领域的相关问题进行提问,也可以就职业发展规划问题进行咨询,也可以把困扰你的问题拿出来一起讨论交流。对于提问的问题尽量做到有问必答,如遇到不懂的,也会通过查阅资料或者请教专家来解答问题。在这里鼓励大家积极发表主题,提问,从而促进整个知识社群的良性循环。每个月小编会针对活跃用户进行打赏。

最重要的是在这里,能够借助这个知识社群,短期内实现年薪百万的梦想!不管你信不信,反正已经进来的朋友肯定是相信的!相遇是一种缘分,相识更是一种难能可贵的情分!如若有缘你我一定会相遇相识!知识星球二维码如下,可以扫描或者长按识别二维码进入。目前已经有 753星球成员,感谢这753童鞋的支持!欢迎各位渴望进步,期望高薪的铁杆粉丝加入!终极目标是打造实现本知识星球全员年薪百万的宏伟目标。

欢迎关注 “吾爱 IC 社区”

微信号:ic-backend2018

568

568

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?