数字IC后端设计实现之时钟树综合答疑篇

文章右侧广告为官方硬广告,与吾爱IC社区无关,用户勿点。点击进去后出现任何损失与社区无关。

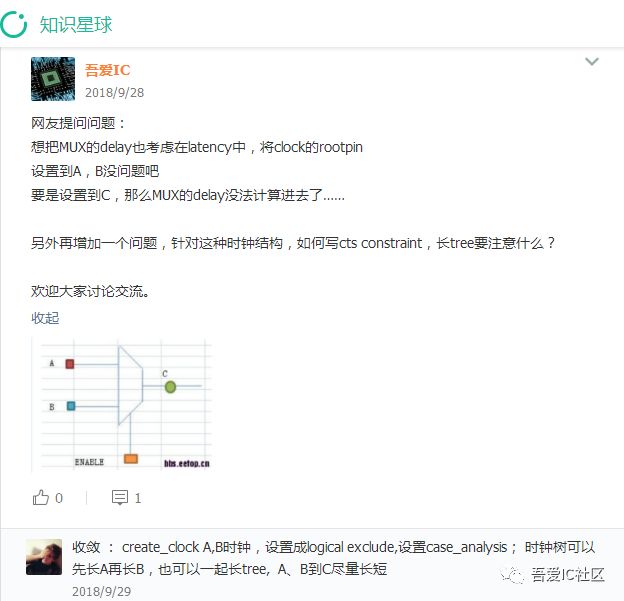

时钟树综合(clock tree synthesis)一直是很多数字 IC 后端工程师的难点也痛点。因为很多工程师向小编反映过这个问题。从我个人的理解时钟树综合的确这是一个难点,可以说是时钟树综合是数字后端实现中最难的一个工作。如果你可以搞定一个无论多复杂的时钟结构的 CLOCK Tree,那么数字后端对你来说,就是小菜一碟,我相信没有你搞不定的问题了。今天吾爱 IC 社区小编将为大家分享一个网友提问的关于时钟树综合的问题。

网友问题描述原文:

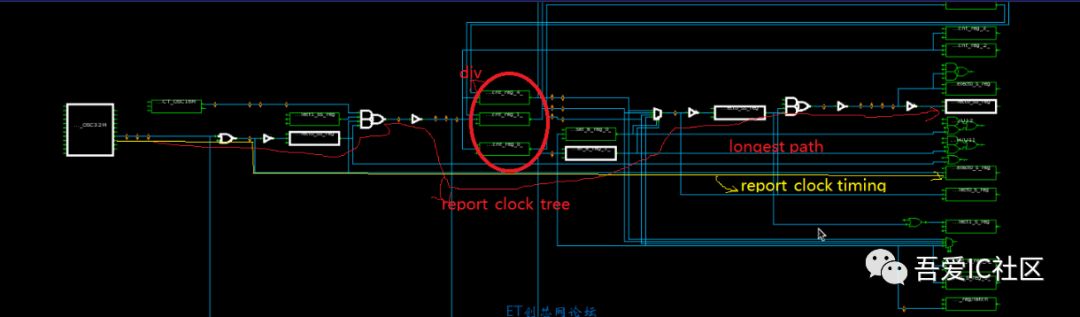

如图,在 cts 之后,我用 report clock tree(clock delay)和 report clock timing(clock latency)报的同一个 clock,但是两条路径,请问如何减小这个 reportclocktree 报出的 longestpath?

从问题描述上看,这位朋友不懂 report_clock_tree 和 report_clock_timing 之间的区别。

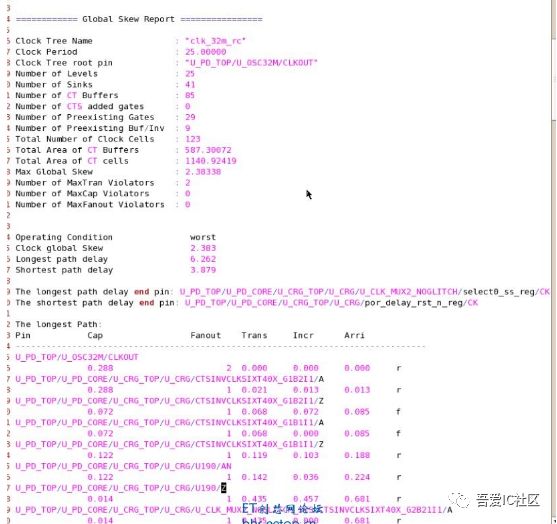

report_clock_tree 一般是用来报出时钟树结构层次,时钟树的 timing exception 等时钟树相关信息。而且报出来的 path 上的 delay 是不考虑 ocv 效应即忽略 set_timing_derate 的影响。

而 report_clock_timing 则是考虑了 OCV 的影响。一般用来报某些 sink 的实际 clock latency。

常用的时钟树分析利器:

Report_clock_tree -clock_tree -summary -all_drc_violations

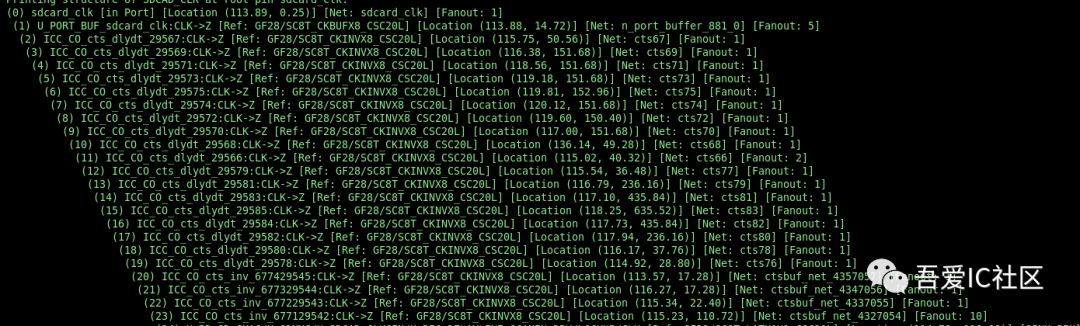

Report_clock_tree -structure

Report_clock_tree -exceptions -show_all_sinks

以上的命令可以用来分析和 debug clock tree 的质量,比如是否存在 timing drc,比如存在很大的 max transition 的点等。当你发现某个 sink 的 clock tree latency 比较长,你也可以将这个点贴到产生的 report 中去,一步步 trace,高效找出 clock tree latency 很长的原因。

所以 report_clock_tree 报出来的 path 的长度和 report_clock_timing 报出来的 path 长度一定是不一样的,就像图中标出的一样。

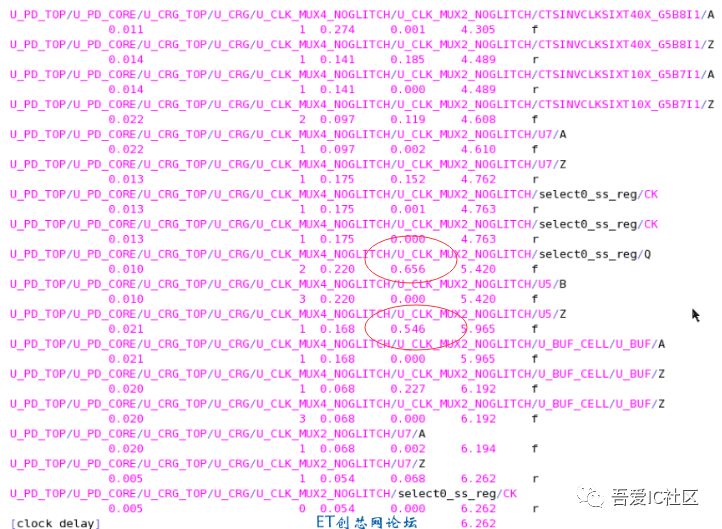

另外从时钟树的 clock skew 报告上看,Longest path delay 为 6.262ns,而 shortest path delay 为 3.879ns。除非是两个 clock domain 或者老死不相往来,不会进行 timing check,否则这么大的 skew,如何进行 timing signoff?这样的时钟树质量能拿得出手吗?

从网友贴出来的 clock tree path 上看,存在很大的不合理性。图中圈出来的部分为 delay 特别大的地方,这些地方不值得去分析原因吗?而且这个报告是不是还可以把 capacitance 和 crosstalk 选项打开,方便看看 crosstalk 的影响,如果是 post-layout 后的数据。

如何将时钟树做短?

做时钟树综合之前还是得分析时钟结构。小编已经在公众号和星球上说过 N 多次如何分析时钟结构了,方法真的是太多了,比如:

-

Verdi 读入设计 netlist,查看原理图

-

ICC/ICC2 中比如 clock tree analysis window,选中时钟,展开原理图

-

DC 或者 PT(Prime Time) 中 trace 电路结构

有了时钟结构后,自己画出时钟结构图,搞清楚时钟同步异步关系,然后就可以写时钟树约束文件 CTS Constraint。对于比较复杂的时钟结构设计,编写时钟树约束文件时建议采用分段 build clock tree 的思想,这样时钟树质量能够达到最佳。

写好时钟树约束文件 CTS Constraint 后,就可以开始 compiler clock tree 了。然后利用前面推荐的时钟树分析神器,找到问题点,逐一解决,直至长出一个 clock skew 小,clock latency 较短的 clock tree。

这个帖子我也是网上看到的,觉得比较基础,也是挺好的素材,拿出来分享下。从第一个图中可以看出,整个时钟结构还是很简单的。前面可能是一个 OCC 产生电路,中间经过分频电路,通过一堆的 clock gating,最后送达给 clock sink 端。

简单时钟树结构经典案例:

如果是一个比较复杂的时钟结构电路,是会涉及到一堆的时钟产生电路,时钟切换电路,为什么要这么做呢?因为 PLL 要钱的,而且也不便宜。另外,设计中各个模块的工作频率可能不一样。

只要涉及到这些的,你就需要搞清楚,时钟源在哪里,它要去哪里,时钟是什么切换的,时钟之间是什么关系等一系列问题。搞清楚了,一切就变的 so easy。

好了,今天的码字就到这里了。如果你觉得文章内容不错,或者对你有所帮助,欢迎转发点赞,让更多的朋友看到,谢谢!吾爱 IC 社区网站(www.52-ic.com)目前已经正式开始运营,希望各位多来捧场,谢谢!点击阅读原文即可自动跳转到吾爱 IC 社区,查看更多精彩内容。

小编知识星球简介:

在这里,目前已经规划并正着手做的事情:

-

ICC/ICC2 lab 的编写

-

基于 ARM CPU 的后端实现流程(已经发布)

-

利用 ICC 中 CCD(Concurrent Clock Data)实现高性能模块的设计实现(已经发布)

-

基于 ARM 四核 CPU 数字后端 Hierarchical Flow 实现教程(准备中)

-

时钟树结构分析

-

低功耗设计实现

-

定期在星球布置作业题(星球已经支持布置作业功能)

在这里,各位可以就公众号推文的内容或者实际项目中遇到的难题提问,小编会在 24 小时内给予解答(也可以发表你对数字后端设计实现中某个知识点的看法,项目中遇到的难点,困惑或者职业发展规划等)。

反正它是一个缩减版的论坛,增强了大家的互动性。更为重要的是,微信有知识星球的小程序入口。星球二维码如下,可以扫描或者长按识别二维码进入。目前已经有六十九位星球成员,感谢这位童鞋的支持!欢迎各位铁杆粉丝加入!终极目标是打造实现本知识星球全员年薪百万的宏伟目标。(星球的门槛将会越来越高,有需求的朋友趁早上车)

点击下方 “阅读全文” 查看更多时钟树专题

1091

1091

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?