基于TSMC 12nm ARM A55 upf flow后端设计实现训练营将于6月中旬正式开班!小班教学!目前还有3个名额,招满为止!有需要可以私信小编 ic-backend2018报名。吾爱IC社区所有训练营课程均为直播课!

这个课程支持升级成双核A55 Top后端训练营!

T12 A55后端训练营简介:

主时钟频率:>= 2.5GHz tt1v85c +rcworst85c

设计规模:140万instance

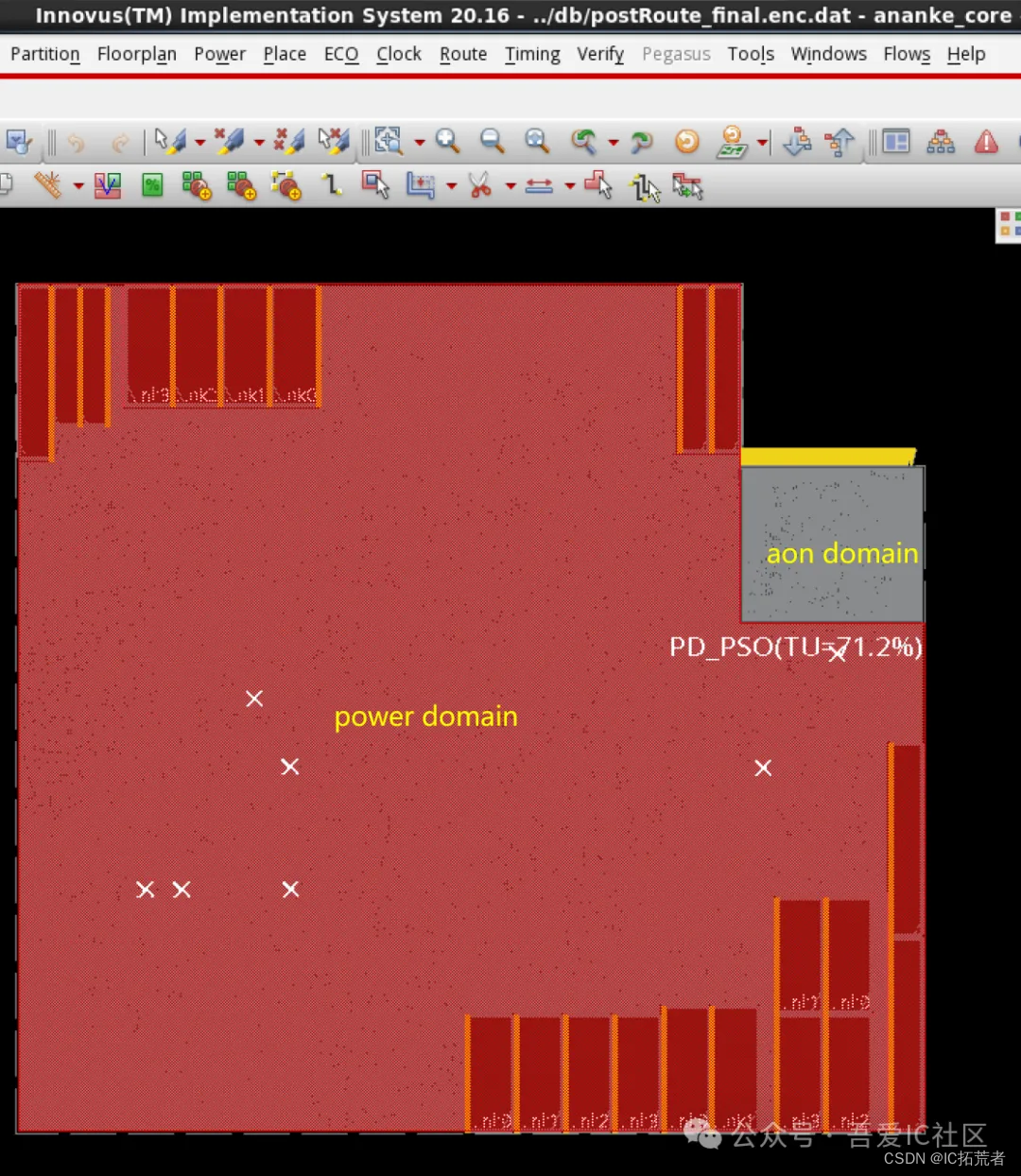

Power Domain数量:2个

实现方式:低功耗模块级UPF Flatten实现 (UPF Flow)

项目成果:Timing Signoff Timing Clean,DRC,Antenna,LVS clean

涉及EDA工具:Innovus,Starrc,PrimeTime,Calibre

授课形式:直播课+每日问题解答+远程协助。每周直播2次,每次近2小时。

课程费用:原价7900元(现价6900元)

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

4758

4758

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?