工艺极限

ss、tt、ff分别指的是左下角的corner,中心、右上角的corner。各种工艺角和极限温度条件下对电路进行仿真是决定成品率的基础。

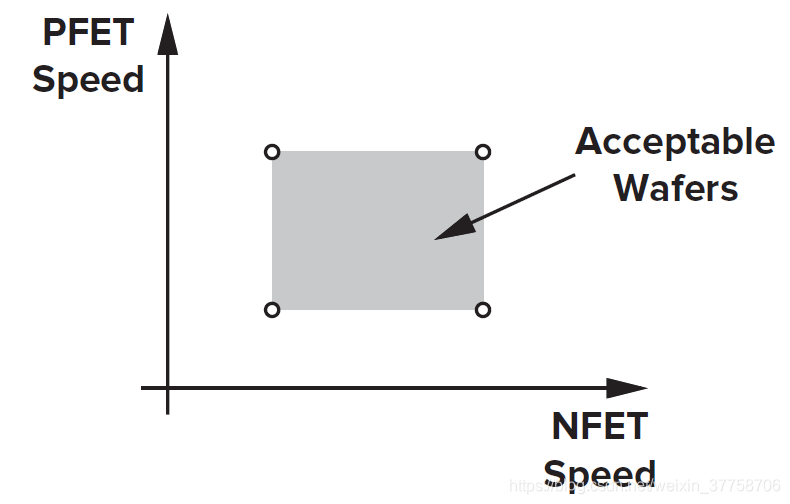

如果采用5-corner model会有TT,FF,SS,FS,SF 5个corners。如TT指NFET-Typical corner & PFET-Typical corner。其中, Typical指晶体管驱动电流是一个平均值,FAST指驱动电流是其最大值,而SLOW指驱动电流是其最小值(此电流为Ids电流)这是从测量角度解释,也有理解为载流子迁移率(Carrier mobility)的快慢。载流子迁移率是指在载流子在单位电场作用下的平均漂移速度。

单一器件所测的结果是呈正态分布的,均值在 TT,最小最大限制值为SS与FF。对于工艺偏差的情况有很多,比如掺杂浓度,制造时的温度控制,刻蚀程度等,因此造成了同一个晶圆上不同区域的情况不同,以及不同晶圆之间不同情况的发生。

PVT (process, voltage, temperature)

设计除了要满足上述5个corner外,还需要满足电压与温度等条件, 形成的组合称为PVT (process, voltage, temperature) 条件。电压如:1.0v+10% ,1.0v ,1.0v-10% ; 温度如:-40C, 0C 25C, 125C。设计时设计师还常考虑找到最好最坏情况. 时序分析中将最好的条件(Best Case)定义为速度最快的情况, 而最坏的条件(Worst Case)则相反。最好最坏的定义因不同类型设计而有所不同。最坏的延迟也不都出现在SS[19] 。至于延迟随PVT发生怎样的变化,还需要进一步查找资料。

根据不同的仿真需要,会有不同的PVT组合。以下列举几种标准STA分析条件[16]:

WCS (Worst Case Slow) : slow process, high temperature, lowest voltage

TYP (typical) : typical process, nominal temperature,nominal voltage

BCF (Best Case Fast ) : fast process, lowest temperature, high voltage

WCL (Worst Case @ Cold) : slow process, lowest temperature, lowest voltage

在进行功耗分析时,可能是另些组合如:

ML (Maximal Leakage ) : fast process, high temperature, high voltage

TL (typical Leakage ) : typical process, high temperature, nominal voltage

除此之外,另一个组合条件称为 Scenarios:

Scenarios = Interconnect + operation mode + PVT

噪声(noise)与串扰(crosstalk) 似乎需要另外考虑。

1. 内连线情况(interconnect corner)

制造对互连线造成的影响,如:R_typical C_typical, R_max C_max, R_max C_min, R_min C_min

2. 工作模式 (Operation Mode)

如:function mode, scan mode, sleep mode, standby mode, active mode

多种scenarios 的综合分析,称之为 MMMC (Multi-Mode Multi-Corner) Analysis。

OCV (On-chip Variations)

由于偏差的存在,不同晶圆之间,同一晶圆不同芯片之间,同一芯片不同区域之间情况都是不相同的。造成不同的因素有很多种,这些因素造成的不同主要体现:

1,IR Drop造成局部不同的供电的差异;

2,晶体管阈值电压的差异;

3,晶体管沟道长度的差异;

4,局部热点形成的温度系数的差异;

5,互连线不同引起的电阻电容的差异。

OCV可以描述PVT在单个芯片所造成的影响。更多的时候, 用来考虑长距离走线对时钟路径的影响。在时序分析时引入derate参数模拟OCV效应,其通过改变时延迟的早晚来影响设计。

博客介绍了电路设计相关知识。工艺极限方面,不同工艺角和极限温度下电路仿真影响成品率,5 - corner model有5个corners。设计需满足PVT条件,不同仿真有不同PVT组合,还有Scenarios组合及MMMC分析。OCV体现芯片不同区域差异因素,可描述PVT对单个芯片影响,时序分析引入derate参数模拟其效应。

博客介绍了电路设计相关知识。工艺极限方面,不同工艺角和极限温度下电路仿真影响成品率,5 - corner model有5个corners。设计需满足PVT条件,不同仿真有不同PVT组合,还有Scenarios组合及MMMC分析。OCV体现芯片不同区域差异因素,可描述PVT对单个芯片影响,时序分析引入derate参数模拟其效应。

3660

3660

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?